Fターム[5F033QQ12]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | プラズマエッチング (898)

Fターム[5F033QQ12]に分類される特許

141 - 160 / 898

配線の作製方法

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

素子搭載用基板、半導体モジュールおよび携帯機器

【課題】半導体素子との接続信頼性の向上が可能な突起電極を有する素子搭載用基板を提供する。

【解決手段】素子搭載用基板20は、絶縁樹脂層32と、絶縁樹脂層32の一方の主表面S1に設けられた配線層34、その配線層34と電気的に接続され、配線層34から絶縁樹脂層32側に突出している突起電極36とを備える。この突起電極36に半導体素子50が電気的に接続されて半導体モジュール10が形成される。突起電極36の頂部面には凹部が設けられている。この凹部は突起電極36の側面に設けられた開放口と連通している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

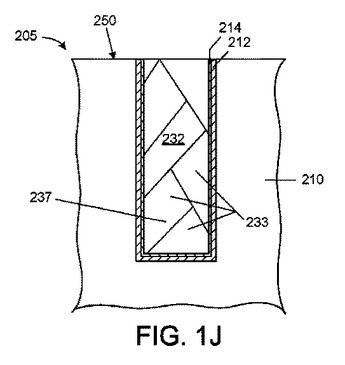

切欠構造のなかで長尺状ルテニウム膜上に多段階式銅鍍金を行う方法。

先端の集積回路にみられる切欠構造(206,207,208,209,211,213,264,275a,275b)において、長尺のルテニウム金属膜(214)に多段階で銅鍍金を行う方法である。長尺のルテニウム金属膜 (214)を利用すると、銅金属がトレンチ(266)及びビア(268)のような高アスペクト比の切欠構造(206,207,208,209,264,275a,275b)を充填するあいだ、不要な微細気泡が形成を防ぎ、前記ルテニウム金属膜(214)上に長尺の銅金属層(228)を含むサイズの大きい銅粒(233)が鍍金形成される。銅粒(233)は銅が充填された切欠構造(206,207,208,209,211,213,275a,275b)の電気抵抗を低下させ、集積回路の信頼性を向上させる。  (もっと読む)

(もっと読む)

半導体集積回路装置の製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

薄膜抵抗素子、および、その製造方法

【課題】安定して配線と抵抗体薄膜との接触が可能な接続構造をもつ薄膜抵抗素子を実現する。

【解決手段】互いに離間する2つの電極配線(3A,3B)に、抵抗体薄膜5を接続させている。2つの電極配線の各々が、主配線部3mと、当該主配線部3mのコア配線部3cより酸化されにくい導電材料で側面に形成されている側壁導電膜3sとを有する。抵抗体薄膜5は、2つの電極配線の各々に対して、側壁導電膜3sを介して電気的に接続している。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

半導体装置の製造方法

【課題】 広範囲にわたって全導電性領域に、断切れ及び上層配線層との間のリーク電流の発生のない、均一な膜厚の銅配線層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】 ガラス基板上に薄膜トランジスタ及び配線を有する半導体装置を製造する方法において、ガラス基板上に下地絶縁層を形成する工程と、前記下地絶縁層上に下地バリア層を形成する工程と、前記下地バリア層上にシード層を形成する工程と、前記シード層を前記配線に対応する形状にパターニングしてシード層パターンを形成する工程と、前記シード層パターンの表面に銅配線層を無電解めっき法で形成する工程と、前記銅配線層マスクとして前記下地バリア層をパターニングする工程と、前記銅配線層を被覆するように絶縁層を形成する工程とを備えたことを特徴する半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電子回路領域の露光と、耐湿リング領域の露光とを、解像度の高い露光装置を用いて別々に行うと、露光装置の占有時間が長くなってしまう。

【解決手段】 半導体基板の上に絶縁膜を形成する。絶縁膜の上に、一方向に長い平面パターン部を含む第1の開口が形成された第1のレジストパターンを形成する。第1のレジストパターンをエッチングマスクとして、第1の開口の一方向に長い平面パターン部の幅方向の中央部に、堆積物が堆積する条件で、絶縁膜をエッチングすることによって、開口に対応する第1の溝を形成する。レジストパターンを除去した後、絶縁膜及び堆積物の上に導電部材を堆積させるとともに、第1の溝内を導電部材で埋め込む。堆積物が露出するまで、導電部材を研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜の膜強度を十分に確保する。

【解決手段】第1の配線層絶縁膜と、第1の配線層絶縁膜に埋め込み形成されている複数の第1の銅配線8と、第1の銅配線8上及び第1の配線層絶縁膜上に形成されている層間絶縁膜(第2の低誘電率膜10)と、を有する。層間絶縁膜上に形成されている第2の配線層絶縁膜と、第2の配線層絶縁膜に埋め込み形成されている複数の第2の銅配線16と、を有する。第1、第2の配線層絶縁膜は、第1、第2の低誘電率膜(第1の低誘電率膜4、第3の低誘電率膜11)を含む。層間絶縁膜は、第1及び第2の配線層絶縁膜よりも高強度である。

(もっと読む)

ドライエッチングガスおよびドライエッチング方法

【課題】高アスペクト比のコンタクトホールを形成する、及び低誘電率膜を良好にエッチングする。

【解決手段】CF3CF=CFCF=CF2及び/又はCF2=CFCF=CF2を必要に応じてHe、Ne、Ar、Xe、Kr、O2、CO及びCO2からなる群から選ばれる少なくとも1種のガスと混合してなるドライエッチングガスプラズマ(例えば、ICP放電電力200-3000W,バイアス電力50-2000W,圧力100mTorr(13.3Pa)以下)で、酸化シリコン膜及び/又は窒化シリコン膜をレジスト、シリコンに対して選択的にエッチングする方法;二重結合を二つ有する一般式(1):CaFbHc(a=4〜7、b=1〜12、c=0〜11、b+c=2a-2を示す。)で表される化合物を少なくともひとつ含むドライエッチングガス及び該ガスプラズマで、酸化シリコン膜及び/又はシリコンを含有する低誘電率膜などのシリコン系材料をエッチングするドライエッチング方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造過程において生じるウエハ外周部分からのパーティクルの発生を防止し、十分な歩留りを実現する。

【解決手段】ウエハにゲート電極となる導電膜4、5を形成する第一工程と、導電膜4、5の中の、ウエハの外周部分に形成された導電膜4、5の上に選択的に保護膜7を形成する第二工程と、導電膜4、5の上に第一レジストパターンを形成し、前記第一レジストパターンをマスクとして導電膜4、5をエッチングすることにより、ゲート電極を形成する第三工程と、前記ゲート電極を覆う層間絶縁膜を形成する第四工程と、前記層間絶縁膜の上に第二レジストパターンを形成し、前記第二レジストパターンをマスクとして前記層間絶縁膜をエッチングすることにより、コンタクトホールを形成する第五工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

半導体装置の設計方法および半導体装置の製造方法

【課題】本発明によれば、素子や配線の配置面積を縮小しつつ、ビアの高抵抗不良およびオープン不良が発生しないようにする。

【解決手段】半導体装置100は、下部電極106と上部電極110と、その間に形成された容量膜108とを含む容量112と、下部電極106に電気的に接続する一以上の第1のビア(128)を含む第1のビア群と、上部電極110に電気的に接続するとともに第1のビア群と同時に形成される一以上の第2のビア(130)を含む第2のビア群と、を含む。半導体装置100は、容量112の容量値を第1のビア群および第2のビア群に含まれる第1のビア(128)および第2のビア(130)の総数で除した値が所定値以下となるように第1のビアおよび第2のビアの数を設定する工程を含む方法で設計される。

(もっと読む)

基板の処理方法及び基板の処理装置

【課題】 層間絶縁膜にLow−k材を使用した基板であっても、層間絶縁膜の経時劣化や変質の可能性を低くできる基板の処理方法を提供すること。

【解決手段】 シリコン酸化膜よりも低い誘電率の誘電体層を含む基板を処理する基板の処理方法であって、不活性ガスの雰囲気中で、前記誘電体層を脱水縮合処理するために加熱する脱水工程と、少なくとも水素原子を含むガスの雰囲気中で、前記基板をアニールする工程と、を備える。

(もっと読む)

半導体装置ならびに半導体装置の製造方法

【課題】ヒロックに対して400℃程度の耐熱性を有するNd添加量2at%のAlNd層を塩素系ガスでプラズマエッチングする場合、フェンスと呼ばれる反応生成物が堆積した領域が生じる。フェンスの存在により、AlNd層をゲート電極としてTFTを形成した場合、ゲート電極脇に電気的に不安定な領域ができることから、TFTの電気的特性が不安定になる場合があるという課題がある。

【解決手段】AlNd層203を層厚0.45μm以上0.8μm以下、Ndの含有量を0.5at%以上1.0at%以下に形成した。この条件範囲であれば、塩素ガスを主としたプラズマエッチングを行ってもフェンスの発生が抑えられる。また、基板温度を500℃まで上げられることから、層間絶縁層211として信頼性が高い酸化シリコン層をAlNd層203にヒロックを発生させることなく形成することができ、信頼性が高いTFT220を提供することが可能となる。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3〜1.2原子%、Ni:0.1〜1.0原子%未満、Laおよび/またはNd:0.1原子%〜1.0 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】ソース電極とドレイン電極のドライエッチングレートの低下や、エッチング残さを引き起こすことがなく、半導体層と、ソース電極やドレイン電極といった配線金属の間からバリアメタルを省略することができる薄膜トランジスタ基板および表示デバイスを提供する課題とする。

【解決手段】半導体層1、ソース電極2、ドレイン電極3、透明導電膜4を有する薄膜トランジスタ基板において、ソース電極2とドレイン電極3は、ドライエッチング法によるパターニングで形成されたGe:0.3原子%〜1.2原子%、Co:0.05原子%〜2.0原子%、Laおよび/またはNd:0.1原子%〜0.5 原子%を含有するAl合金薄膜より成り、半導体層1と直接接続している。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】35mmデジタル一眼レフ・カメラ用のCMOSイメージ・センサは、チップサイズが非常に大きく、200φウエハ上に20チップ程度しか配置できない。従って、ウエハあたり、ショート欠陥が数個存在しただけで、歩留まりが大きく低下する。そこで、これらの欠陥を一般的なレーザ・トリミング技術により、除去することを検討したが、サブ・ミクロン・オーダの加工は非常に困難であることが判明した。

【解決手段】本願発明は、ピクセル・アレイ、これを横断又は縦断する複数のグローバル配線、および、各ピクセル内に設けられたローカル配線を有する半導体集積回路装置であって、第1のグローバル配線と、第1のピクセル内にあるローカル配線との間のショート不良箇所が、そのローカル配線の機能を実質的に破壊し、前記第1のグローバル配線の機能を実質的に破壊しないように、レーザ・リペア処理された修正処理部を有するものである。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

141 - 160 / 898

[ Back to top ]