Fターム[5F033QQ14]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | イオンミリング、スパッタエッチング (405)

Fターム[5F033QQ14]に分類される特許

1 - 20 / 405

半導体装置、半導体装置の製造方法、および電子機器

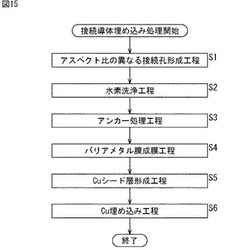

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

半導体装置

【課題】フリップチップ実装に用いられる半導体チップと実装基板との電気的な接続信頼性を向上させた半導体装置を提供する。

【解決手段】半導体チップ2と、半導体チップ2の主面に配置された複数の電極パッドと、複数の電極パッドの上に配置された複数のバンプ5とを有し、半導体チップ2のコーナー部において、第1のバンプと第2のバンプとが、第1のピッチで、隣接して配置され、半導体チップの中心部において、第3のバンプと第4のバンプとが、第2のピッチで、隣接して配置され、第1のピッチは、第2のピッチよりも狭い。

(もっと読む)

半導体装置の製造方法

【課題】レジスト形状の制限が無く、またステップカバレッジの悪い成膜方法を用いなくても良いリフトオフ工程が行えるようにする。

【解決手段】レジスト2の上に被パターニング膜3を成膜したのち、イオン照射によって被パターニング膜3のコーナ部を選択的にエッチングすることでレジスト2を露出させるようする。そして、レジスト2を除去することで、レジスト2の上の被パターニング膜3をリフトオフさせ、被パターニング膜3をパターニングする。このようにしてリフトオフ工程を行えば、レジスト2の側面において被パターニング膜3が厚く形成されていたとしても、イオン照射によってレジスト2を露出させることができる。このため、レジスト2の側面での被パターニング膜3の厚みの制限を受けないため、あえてステップカバレッジの悪い成膜方法を用いなくても良くなり、ステップカバレッジの良い成膜方法を選択することもできる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性が高く、ソースとドレインの間にリーク電流が生じにくく、コンタクト抵抗が小さい半導体装置を提供する。

【解決手段】酸化物半導体膜により形成されるトランジスタの電極膜上に酸化物半導体膜に接して設けられた第1の絶縁膜、及び第2の絶縁膜を積層して形成し、第2の絶縁膜上にエッチングマスクを形成し、エッチングマスクの開口部と重畳する部分の第1の絶縁膜及び第2の絶縁膜をエッチングして電極膜を露出する開口部を形成し、第1の絶縁膜及び第2の絶縁膜の開口部をアルゴンプラズマに曝し、エッチングマスクを除去し、第1の絶縁膜及び第2の絶縁膜の開口部に導電膜を形成し、第1の絶縁膜は加熱により酸素の一部が脱離する絶縁膜であり、第2の絶縁膜は第1の絶縁膜よりもエッチングされにくく、第1の絶縁膜よりもガス透過性が低い。または逆スパッタリングを行ってもよい。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】貫通電極を生産性良く形成できる貫通電極の構造を提供する。

【解決手段】配線基板1は、第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、ビアホール2cの面に設置され基板2と同じ材質のシード膜5と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3とシード膜5を囲む場所とに設置され熱酸化膜を含む第3絶縁膜6と、ビアホール2c内でシード膜5に囲まれた導電体7と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

配線基板、赤外線センサー及び貫通電極形成方法

【課題】基板と貫通電極との間で形成される浮遊容量が小さい基板を提供する。

【解決手段】第1面2aと第1面2aと対向する第2面2bとを貫通して開口するビアホール2cを有する基板2と、基板2の第1面2aに設置され熱酸化膜を含む第1絶縁膜3と、ビアホール2c内の面とに設置され熱酸化膜を含む第3絶縁膜5と、ビアホール2c内で第3絶縁膜5に囲まれた導電体7と、を有し、第1面2aにおける第1絶縁膜3の厚みに比べてビアホール2c内の面における第3絶縁膜5の厚みが厚くなっている。

(もっと読む)

電力用半導体装置及びその製造方法

【課題】本発明は、信頼性の高い外部電極との接続構造を有する電力用半導体装置及びその製造方法の提供を目的とする。

【解決手段】本発明の電力用半導体装置は、段差を有する絶縁膜9と、絶縁膜9の前記段差を覆って形成された上部配線10と、上部配線10上の少なくとも前記段差の側壁に対応する部分を含む所定箇所に、部分的に形成された酸化膜16と、上部配線10及び酸化膜16上に形成され、半田21により外部導体22と接合するバリア層20とを備える。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

電子デバイス、及び、その製造方法

【課題】素子に不具合が生じることが抑制された電子デバイス、及び、その製造方法を提供する。

【解決手段】接合された2つの基板(10,50)に素子(20,60)と貫通電極(30)とが形成されて成る電子デバイスであって、素子(20,60)は、2つの基板(10,50)の少なくとも一方に形成され、貫通電極(30)は、2つの基板(10,50)の少なくとも一方に形成されており、貫通電極(30)は、一方の基板(10)における他方の基板(50)との接合面(10a)側から、その裏面(10b)まで除去されて成るトレンチ(31)と、該トレンチ(31)を構成する壁面の一部に形成された導電膜(35)と、を有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線信頼性が向上される。

【解決手段】半導体基板上に配線層11と層間絶縁膜12とが順に形成され、層間絶縁膜12にトレンチ溝13とトレンチ溝13中に配線層11に達するビア孔14とが形成され、トレンチ溝13内、ビア孔14内および層間絶縁膜12上に、チタン、ジルコニウムおよびマンガンのうちのいずれか、もしくはこれらの合金である金属膜15が成膜され、スパッタ法を用いて、ビア孔14の底部の金属膜15をエッチングするとともに、トレンチ溝13の底部および側壁とビア孔14の側壁に、タンタル、タングステンのいずれか、もしくはこれらの合金である金属膜16が成膜されて、さらに、ビア孔14の側壁にそれぞれの金属によって新たな金属膜が生成され、ビア孔14とトレンチ溝13とを導電性材料17aで埋め込んだ配線層が形成されるようになる。

(もっと読む)

1 - 20 / 405

[ Back to top ]