Fターム[5F033QQ16]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 異方性エッチング (964)

Fターム[5F033QQ16]の下位に属するFターム

斜めエッチング (8)

Fターム[5F033QQ16]に分類される特許

1 - 20 / 956

半導体ウェハ、半導体装置及びその製造方法

半導体装置およびその製造方法

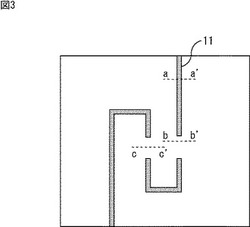

【課題】同一レイヤに成膜された後、複数回のエッチングにより形成された導電性被加工物を、下地層に段差を作ることなく、異なる電位に固定する。

【解決手段】同一レイヤに成膜された後、複数回のエッチングにより線状に形成された導電性被加工物を備え、導電性被加工物は、自身を電気的に分断する2以上の分断部分を有し、分断部分における導電性被加工物は、その一部が平行になるように形成されており、平行に形成された部分の少なくとも一方は分断されている。複数回のエッチングに用いられるレジストパターンのうちの、所定回数目のエッチングに用いられる第1のレジストパターンと、他の回数目のエッチングに用いられる第2のレジストパターンとが重なる領域の、平行に形成された部分に対応する箇所の幅は、エッチングによる導電性被加工物の後退量より小さい。本技術は、半導体装置に適用することができる。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成時スループットやコスト悪化を回避する。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【目的】配線間のコンタクト配置において配線間距離をより小さく形成する。

【構成】実施形態の半導体装置は、第1と第2の配線と、第1の絶縁膜と、第2の絶縁膜と、第1のコンタクトと、第2のコンタクトと、を備えている。第1と第2の配線は、基板上に互いに並行するように形成される。第1の絶縁膜は、第1と第2の配線を覆うように形成される。第2の絶縁膜は、第1と第2の制御ゲート線間の所定位置で第1と第2の配線と並行して延びるように形成され、第1の絶縁膜と材料が異なる。第1のコンタクトは、第1と第2の配線間で、前記第2の絶縁膜に対して前記第1の配線側に位置する前記第1の絶縁膜を通して形成される。第2のコンタクトは、前記第1と第2の配線間で、前記第1と第2の配線が延びる方向に沿って前記第1のコンタクトと互いに位置をずらしつつ、前記第2の絶縁膜に対して前記第2の配線側に位置する前記第1の絶縁膜を通して形成される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通ビアを用いた実装における端子間のショートや実装精度の低下を防止する。

【解決手段】半導体チップ88の貫通ビア86の上に、他の半導体チップ101を実装する。半導体チップ101のバンプ103は、4つの貫通ビア86で囲まれた領域に導かれて接合される。各貫通ビア86は、バンプ103に面する側面及び上面の保護膜31がエッチングによって除去されており、バンプ103のハンダ材料への濡れ性が保護膜31で覆われた領域よりも良好になっている。このために、ハンダ材料のはみ出しによる他の電極との間のショートが防止される。さらに、1つのバンプ103に複数の貫通ビア86からなる接続端子を配置するので、バンプ103に確実に接合できる。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】外部からの不純物等に対する耐性を向上することができる半導体装置及びその製造方法を得る。

【解決手段】GaAs基板1上に下層配線2が設けられている。GaAs基板1及び下層配線2上に樹脂膜4が設けられている。樹脂膜4は、下層配線2上に開口5を有する。下層配線2及び樹脂膜4上にSiN膜6が設けられている。SiN膜6は、開口5内に開口7を有する。下層配線2及び樹脂膜4の一部上に上層配線8が設けられている。上層配線8は、開口5,7を介して下層配線2に接続されたTi膜8aと、Ti膜8a上に設けられたAu膜8bとを有する。上層配線8及び樹脂膜4上にSiN膜9が設けられている。SiN膜9は、樹脂膜4上においてSiN膜6に付着している。SiN膜6,9はTi膜8aの周囲を保護する。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

エッチング方法、エッチング装置、および記憶媒体

【課題】工程および装置構成を煩雑にすることなく、高エッチングレートで銅を異方性エッチングする装置、及びその方法を実施するプログラムを記憶した媒体を提供する。

【解決手段】チャンバ内に表面に銅膜104を有する基板101を配置し、チャンバ内を真空状態としつつ、チャンバ内に有機化合物106を供給し、銅膜に酸素ガスクラスターイオンビームを照射し、酸素ガスクラスターイオンビーム中の酸素ガスクラスターイオン107により、銅膜の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅膜を異方的にエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】スルーホールの底部における突起の形成を防止して、半導体装置の品質を安定させる手段を提供する。

【解決手段】配線層5と、該配線層上に形成された金属窒化膜8とを覆う層間絶縁膜9とを形成した半導体ウェハに、層間絶縁膜を貫通し金属窒化膜に達するスルーホール10を形成する工程を備えた半導体装置の製造方法において、スルーホールを形成する工程は、層間絶縁膜上に、レジストマスク18を形成する工程と、半導体ウェハを第1の温度とし、異方性エッチングにより層間絶縁膜をエッチングする第1のエッチング工程と、半導体ウェハを、第1の温度より高い第2の温度とし、レジストマスクをそのまま用いて、異方性エッチングにより金属窒化膜の上表面をエッチングする第2のエッチング工程と、レジストマスクを除去する工程と、を備え、第1のエッチング工程と、第2のエッチング工程で用いるエッチングガスとを同一とする。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

1 - 20 / 956

[ Back to top ]