Fターム[5F033QQ23]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングストッパー (1,788)

Fターム[5F033QQ23]の下位に属するFターム

Fターム[5F033QQ23]に分類される特許

1 - 20 / 52

半導体装置の製造方法及び半導体装置

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

半導体装置

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

半導体装置

【課題】端子部のコンタクトホールのテーパー形状を高い精度で制御する。

【解決手段】酸化物半導体層7a、ソース配線13as、ドレイン電極13adを備えた薄膜トランジスタと、第1接続部3c、第2接続部13cおよび第2接続部上に形成された第3接続部19cを備えた端子部とからなる薄膜トランジスタである。第2接続部は、第1および第2絶縁膜5,9に設けられた第1開口部内で第1接続部と接し、第3接続部19cは、保護膜に設けられた第2開口部内で第2接続部と接する。第1開口部は、第1絶縁膜5および第2絶縁膜9を同時にエッチングすることによって形成、第2開口部は、保護膜15を前記第1および第2絶縁膜とは別個にエッチングすることによって形成される。第2接続部13cは、第1開口部における第1および第2絶縁膜の端面を覆い、かつ、第2開口部における保護膜15の端面を覆っていない。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板を貫通するビアホールの形成時におけるノッチの発生を抑制することができ、製造歩留まり及び信頼性の向上をはかる。

【解決手段】 シリコン基板貫通電極を有する半導体装置の製造方法であって、表面側に機能素子と配線層15が形成され、且つ配線層15の下層にエッチング停止層12を有するシリコン基板10の表面側に支持基板30を取着した後、基板10の裏面側を研削して厚みを減少させる。次いで、基板10の裏面側に、ビアホール用開口及び該開口よりも小径のダミーホール用開口を有するマスクを形成した後、基板10の裏面側からエッチングすることにより、配線層15の一部に達するビアホール42を形成すると共に、基板10の途中までダミーホール43を形成する。次いで、ビアホール42の側面に絶縁膜44を形成した後、ビアホール42内に配線材料を形成する。

(もっと読む)

信頼性を改良するための導電性層間のビア

【課題】ビアの信頼性を改良するための技術を提供する。

【解決手段】別の半導体デバイスが、複数の導電性配線(12−20)を含む第1層(21)および第2層(33)を含み、複数の非機能的ビアパッド(34)が、第2層または第1層と第2層との間に含まれる。複数のダングリングビア(40)は、第1層の特定の領域内に含まれる。ダングリングビアは、第1層の1つまたは複数の配線をビアパッドの対応する一つに接続する。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

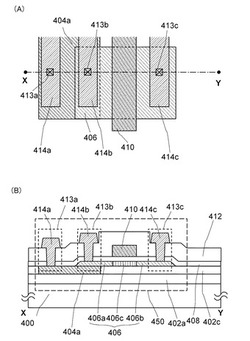

半導体装置とその作製方法

【課題】特性が良好なトランジスタを提供する。

【解決手段】例えば、ボトムゲート・ボトムコンタクト構造のトランジスタを作製するに際して、ソースとドレインを構成する導電層を3層の積層構造とし、2段階のエッチングを行う。すなわち、第1のエッチング工程には、少なくとも第2の膜及び第3の膜に対するエッチングレートが高いエッチング方法を採用し、第1のエッチング工程は少なくとも第1の膜を露出するまで行う。第2のエッチング工程には、第1の膜に対するエッチングレートが第1のエッチング工程よりも高く、「第1の膜の下に接して設けられている層」に対するエッチングレートが第1のエッチング工程よりも低いエッチング方法を採用する。第2のエッチング工程後にレジストマスクをレジスト剥離液により剥離するに際し、第2の膜の側壁が少し削られる。

(もっと読む)

半導体装置及び製造方法

【課題】 ビアホール上にオーミック電極が形成された半導体装置において、装置の小型化を図ること。

【解決手段】 本半導体装置は、基板10と、基板10上に形成された半導体層12と、半導体層上12に形成されたソースまたはドレイン電極を構成するオーミック電極20と、を備え、基板10及び半導体層12には、基板10及び半導体層12を貫通するビアホール30が形成され、ビアホール30は、少なくとも半導体層を貫通する第1ビアホール32と、第1ビアホール32下の基板10に形成された、第1ビアホール32より開口断面積が大きい第2ビアホール34と、を含み、オーミック電極20は、第1ビアホール32の上に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】少ない工数の追加でロジック回路とメタル容量素子とを混載し、かつ、ロジック動作特性の劣化を生じることがない半導体装置の製造方法を提供する。

【解決手段】基板11上に第1層間絶縁膜13を形成し、第1層間絶縁膜13に導電体柱14A、14Bを形成する。第1層間絶縁膜13の上面に溝配線部絶縁膜15を形成する。導電体柱14Bの上方において溝配線部絶縁膜15を除去して容量用開口部151を形成し、第1層間絶縁膜15の上面に容量素子用絶縁膜16を形成する。導電体柱14Aの上方において容量素子用絶縁膜16および第1層間絶縁膜15を除去して配線用溝152を形成する。容量用開口部151および配線用溝152に金属体17A、17Bを埋め込む。容量用開口部152の金属体17Aを容量素子の上部電極とし、配線溝152の金属体17Bをロジック配線とする。

(もっと読む)

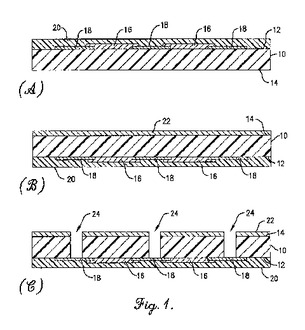

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電子回路領域の露光と、耐湿リング領域の露光とを、解像度の高い露光装置を用いて別々に行うと、露光装置の占有時間が長くなってしまう。

【解決手段】 半導体基板の上に絶縁膜を形成する。絶縁膜の上に、一方向に長い平面パターン部を含む第1の開口が形成された第1のレジストパターンを形成する。第1のレジストパターンをエッチングマスクとして、第1の開口の一方向に長い平面パターン部の幅方向の中央部に、堆積物が堆積する条件で、絶縁膜をエッチングすることによって、開口に対応する第1の溝を形成する。レジストパターンを除去した後、絶縁膜及び堆積物の上に導電部材を堆積させるとともに、第1の溝内を導電部材で埋め込む。堆積物が露出するまで、導電部材を研磨する。

(もっと読む)

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

半導体装置の製造方法

【課題】個片化時に切断部分が欠けてしまうことを防止できる半導体装置の製造方法を提供する。

【解決手段】複数の素子領域と複数の素子領域を区画する区画領域とを具える上面(第1面)と、上面(第1面)の反対側の裏面(第2面)とを有する半導体ウエハ101Aを準備する工程と、上面(第1面)の各素子領域上に、上層配線102をそれぞれ形成する工程と、裏面(第2面)側から半導体ウエハ101Aを例えばDeep−RIEなどによりエッチングすることで、上層配線102を露出する貫通孔A2を形成すると共に、上面(第1面)の区画領域に対応する裏面(第2面)の領域に半導体ウエハ101Aを貫通する溝B22を形成する工程とを有する。

(もっと読む)

三次元積層型半導体集積回路及びその製造方法

【課題】スルーシリコンビアの高密度化、製造歩留りの向上及び製造コストの低減を同時に実現する。

【解決手段】本発明の例に係る三次元積層型半導体集積回路は、同一方向を向いて互いに積み重ねられる第一及び第二チップC1,C2と、第一チップC1を構成する第一半導体基板21及び第二チップC2を構成する第二半導体基板21を貫通し、かつ、第一チップC1内に設けられる半導体素子に繋がる第一電極14を貫通するスルーシリコンビア13とを備える。第一及び第二チップC1,C2は、面で結合する。

(もっと読む)

半導体デバイスのメタライゼーションシステムにおいて優れたエレクトロマイグレーション性能を提供すること及び敏感な低k誘電体の劣化を低減すること

【解決手段】

複雑なメタライゼーションシステムの形成の間、全体的な伝導性に否定的な影響を与えることなしにエレクトロマイグレーション性能を高めるために、伝導性キャップ層(122C)が銅含有金属領域(122A)上に形成されてよい。その一方で熱化学的処理が実行されてよく、その結果、敏感な誘電体材質(121)の優れた表面状態をもたらすことができる他、敏感なULK材質の材質特性の大きなばらつきを従来的にはもたらすことがある炭素減損を抑制することができる。

(もっと読む)

半導体装置とその製造方法

【課題】集積回路の信号用の端子との干渉を避けつつ、半導体装置のシールリングを介したノイズの影響を低減する。

【解決手段】半導体装置は、基板上に形成された集積回路と、その集積回路を取り囲むシールリングとを有する。シールリングの第一部分は基板の裏面に到達し、その裏面側において電位が一定の端子に接続されている。裏面側から一定電位の端子に接続することにより、表面側の信号用端子と干渉することなくシールリングによるノイズ伝搬を防ぐことができる。

(もっと読む)

半導体素子の製造方法および半導体素子

【課題】 半導体素子の微細パターン製造方法を提供する。

【解決手段】フィーチャー層310の第1領域Aには第1マスク構造物を形成し、第2領域Bには第2マスク構造物を形成する。各々デュアルマスク層とエッチングマスク層とを含むように第1マスク構造物及び第2マスク構造物を形成する。第1マスク構造物及び第2マスク構造物のエッチングマスクパターンを等方性エッチングし、第1マスク構造物からエッチングマスクパターンを除去する。第1マスク構造物及び第2マスク構造物の両側壁にスペーサ350A、350Bを形成する。第2マスク構造物上にあるエッチングマスクパターンをマスクとして第1領域Aで間にボイドが形成されるように側壁スペーサ350Aを含む第1マスクパターンと、第2領域Bで間に第2マスク構造物が介在するように側壁スペーサ350B、350Cを含む第2マスクパターンを形成する。

(もっと読む)

誘電体層と導電性層との間の付着性改善およびエレクトロマイグレーション改善

基板を加工処理するための方法および装置を提供する。基板を加工処理するための方法は、導電性材料を備えた基板を準備することと、導電性材料上に前処理プロセスを実行することと、シリサイド層を形成するために導電性材料上にシリコン系化合物を流すことと、シリサイド層上に後処理プロセスを実行することと、基板上にバリア誘電体層を堆積することとを含む。  (もっと読む)

(もっと読む)

1 - 20 / 52

[ Back to top ]