Fターム[5F033QQ26]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングマスク (2,287)

Fターム[5F033QQ26]の下位に属するFターム

導電膜 (467)

絶縁膜 (1,171)

多層レジスト (195)

エッチング後も残存させるもの (194)

Fターム[5F033QQ26]に分類される特許

1 - 20 / 260

半導体ウェハ、半導体装置及びその製造方法

半導体装置およびその製造方法

半導体装置およびその製造方法

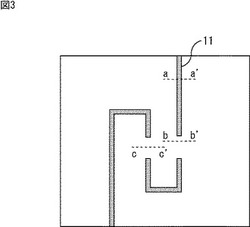

【課題】同一レイヤに成膜された後、複数回のエッチングにより形成された導電性被加工物を、下地層に段差を作ることなく、異なる電位に固定する。

【解決手段】同一レイヤに成膜された後、複数回のエッチングにより線状に形成された導電性被加工物を備え、導電性被加工物は、自身を電気的に分断する2以上の分断部分を有し、分断部分における導電性被加工物は、その一部が平行になるように形成されており、平行に形成された部分の少なくとも一方は分断されている。複数回のエッチングに用いられるレジストパターンのうちの、所定回数目のエッチングに用いられる第1のレジストパターンと、他の回数目のエッチングに用いられる第2のレジストパターンとが重なる領域の、平行に形成された部分に対応する箇所の幅は、エッチングによる導電性被加工物の後退量より小さい。本技術は、半導体装置に適用することができる。

(もっと読む)

ビットライン接触面積確保のための半導体素子、その半導体素子を有するモジュール及びシステム

【課題】埋め込みゲートを有する半導体素子に関し、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

【解決手段】ビットラインコンタクト136が活性領域120の上部面だけではなく側面とも接触されることにより、ビットラインコンタクトと活性領域の接触面積を増加させビットラインコンタクトの高抵抗性フェイルを防止する。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、工程数削減によるコスト低減を図れる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、第2の被加工膜の上に第2の方向に延びる複数の第2の芯材膜であって、第1のスペースを隔てて第1の方向に並んだ第1の配列部と、第1のスペースよりも大きな第2のスペースを第1の方向に隔てて配置された第2の配列部とを有し、第2のスペースがループ部の上に位置する第2の芯材膜を形成する工程と、第2の芯材膜を除去し第2の被加工膜上に第2のスペーサー膜を残す工程と、第2のスペーサー膜をマスクにしたエッチングにより、第1の配列部の下の第2の被加工膜を、第2の方向に延びる第2のラインパターンを含む第2のラインアンドスペースパターンに加工するとともに、第2のスペースの下の第2の被加工膜と、第1の被加工膜のループ部とを除去する工程とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

厚膜レジストの現像方法、及び半導体デバイスの製造方法

【課題】生産性を低下させることなく、基板の外周部にレジスト残渣が発生することを抑制可能な厚膜レジストの現像方法、及び半導体デバイスの製造方法を提供する。

【解決手段】回路素子層の上面に、厚膜レジストを形成する工程と、厚膜レジストを露光する工程と、露光後に、30〜50rpmの範囲内の一定の回転速度で炭化珪素基板を回転させながら、厚膜レジストの上方から現像液を供給することで、厚膜レジストの上面に現像液よりなるパドルを形成し、該パドルにより厚膜レジストを現像して、厚膜レジストに回路素子層の上面を露出する開口部を形成する工程と、を有する。

(もっと読む)

成膜方法、これを含む半導体装置の製造方法、成膜装置、及び半導体装置

【課題】柱状形状を有し密に配列される電極の倒壊を防ぐことが可能な半導体装置を提供する。

【解決手段】電界効果トランジスタと、柱状形状を有するキャパシタとを有する半導体装置であって、前記電界トランジスタの不純物拡散領域と電気的に接続し、柱状形状を有する第1の電極と、前記第1の電極の少なくとも側面に形成される誘電体膜と、前記誘電体膜上に形成される第2の電極と、前記柱状形状を有する前記第1の電極の長手方向と交差する方向に延び、前記第2の電極の少なくとも一部を貫通して前記第1の電極を連結するホウ素添加窒化シリコン膜により形成される支持膜とを備える半導体装置により、上記の課題が達成される。

(もっと読む)

プラズマ処理方法及びプラズマアッシング装置

【課題】Low-k膜を有する試料のプラズマアッシング処理において、高速にアッシング処理を行いつつ、Low-k膜に対する膜ダメージを抑制または低減する処理方法を提供する。

【解決手段】Low-k膜15を有する試料をプラズマ処理するプラズマ処理方法において、前記試料をプラズマエッチングする工程と、炭化水素系ガスであるメタン(CH4)ガス19と希ガスであるアルゴン(Ar)ガスとからなる混合ガスを用いて、プラズマエッチング工程でプラズマエッチングされたレジストマスク13、炭素ハードマスク14、反応生成物16が付着したLow-k膜15を有する試料を、メタン(CH4)ガス19からの炭素(C+)ラジカル18と水素(H+)ラジカル19により、プラズマアッシングする工程を有するプラズマ処理方法である。

(もっと読む)

電子デバイス及びその製造方法

【課題】貫通電極の基板等との熱膨張率差に起因する変形を抑えるにあたり、製造プロセスの工程数を増加させることなく貫通電極の側面形状に起因するデバイス特性の劣化を抑止する、信頼性の高い電子デバイスを提供する。

【解決手段】基板1と、基板1の表面上方に形成された配線18と、基板1の裏面から基板1を貫通しており、基板1の深さ方向において、第1の開孔1Aaと、第1の開孔1Aaよりも開口総面積が小さい第2の開孔1Abとが接続された貫通孔1Aに形成されてなる貫通ビア30とを含み、貫通ビア30は、第1の開孔1Aaに形成された第1の電極部30aと、第2の開孔1Abに形成された第2の電極部30bとが、最外側面が一体形成される。

(もっと読む)

半導体装置の製造方法

【課題】TATの短縮及び製造コストの低下を図る。

【解決手段】実施形態に係わる半導体装置の製造方法は、下地層上にピラーを形成する工程と、GCIB法を用いて、下地層上に、ピラーを覆い、かつ、上面の最も低い部分がピラーの上面よりも下にある絶縁層を形成する工程と、CMP法を用いて、絶縁層及びピラーを、絶縁層の上面の最も低い部分まで研磨する工程とを備える。

(もっと読む)

1 - 20 / 260

[ Back to top ]