Fターム[5F033QQ50]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 研磨 (4,337) | 研磨材、研磨液 (82)

Fターム[5F033QQ50]に分類される特許

1 - 20 / 82

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置の製造方法

【課題】CMP法により、金属膜を研磨して、層間絶縁膜に設けられた開口部内に導体パターンを形成する際、リセス、ディッシング、及びエロージョンを抑制可能な半導体装置の製造方法を提供する。

【解決手段】CMP法により、層間絶縁膜14の上面よりも上方に形成された金属膜19及びバリア膜18を除去することで、開口部内に、バリア膜18及び金属膜19よりなる導体パターンを形成する研磨工程と、を有し、該研磨工程では、層間絶縁膜14の上面が露出する前に、金属膜19の研磨レートと層間絶縁膜14の研磨レートとの差が小さい研磨条件を用いて研磨を行なうことで、導体パターンを形成する。

(もっと読む)

半導体デバイス用基板洗浄液及び洗浄方法

【課題】基板表面を腐食することなく微粒子付着による汚染、有機物汚染及び金属汚染を同時に除去することができ、しかも水リンス性も良好で、短時間で基板表面を高清浄化することができる半導体デバイス用基板洗浄液を提供する。

【解決手段】

半導体デバイス製造における化学的機械的研磨工程の後に行われる、半導体デバイス用基板の洗浄工程に用いられる洗浄液であって、以下の成分(A)〜(D)を含有してなる半導体デバイス用基板洗浄液。

(A)有機酸

(B)スルホン酸型アニオン性界面活性剤

(C)ポリビニルピロリドン及びポリエチレンオキシド−ポリプロピレンオキシドブロック共重合体から選ばれる少なくとも1種の高分子凝集剤

(D)水

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】複数のゲート電極3bを覆うように窒化シリコン膜(第1絶縁膜)5を形成した後、オゾンTEOS膜(第1酸化シリコン膜)6、プラズマTEOS膜(第2酸化シリコン膜)を順次積層する。ここで、オゾンTEOS膜6を積層後、プラズマTEOS膜を積層する前に、窒化シリコン膜5をCMPストッパ膜として、CMP法により研磨する。これにより、プラズマTEOS膜の膜厚を均一化させることができるので、半導体装置の信頼性を向上させることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

絶縁膜および半導体装置

【課題】誘電率の低い絶縁膜であって、半導体装置の製造においてCMP法により当該絶縁膜上の膜を好適に除去することができるとともに、キャップ層を備えておらず、かつ、信頼性に優れた半導体装置の製造に好適に用いることができる絶縁膜を提供すること。

【解決手段】本発明の絶縁膜は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて形成された絶縁膜であって、0.03〜20μmの膜厚を有し、ナノインデンターを用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする測定から求められる弾性率が、4.0GPa以上であることを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】低誘電率の絶縁膜を備える一方で、当該絶縁膜上に選択的に設けられたキャップ層を備えておらず、信頼性に優れた半導体装置を効率よくかつ確実に製造することができる製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、分子内に、アダマンタン型のかご型構造を含む部分構造と、重合反応に寄与する重合性反応基とを有する重合性化合物および/または当該重合性化合物が部分的に重合した重合体を含む組成物を用いて、膜厚の2分の1以上の最大押し込み深さにおいて、弾性率測定変位を膜厚の10分の1とする、ナノインデンターを用いた測定から求められる弾性率が、4.0GPa以上である絶縁膜を形成する工程を有する一方で、絶縁膜上にキャップ層を形成する工程を有していない。

(もっと読む)

半導体装置の製造方法

【課題】配線間のショートを抑制すること。

【解決手段】半導体基板10上に第1絶縁膜20を形成する工程と、前記第1絶縁膜の上面を研磨する工程と、研磨された前記第1絶縁膜に接続30孔を形成する工程と、前記接続孔の内面および前記第1絶縁膜上に前記第1導電層32を形成する工程と、前記接続孔内の前記第1導電層上に第2導電層34を形成する工程と、前記第1絶縁膜上の前記第1導電層を研磨し前記第1絶縁膜の上面を露出させる工程と、前記第2導電層のエッチングレートより前記第1導電層のエッチングレートが大きいエッチャントを用い、前記接続孔内上部の前記第1導電層をエッチングする工程と、前記絶縁膜上に配線層50を形成する工程と、を含む半導体装置の製造方法。

(もっと読む)

基板製造方法及び基板

【課題】CMPの処理時間を短縮する。

【解決手段】基板製造方法は、基板上に絶縁層を形成する工程と、絶縁層上に第1のマスクを形成する工程と、第1のマスクを介して絶縁層をエッチングすることにより絶縁層に溝を形成する工程と、第1のマスクを除去する工程と、絶縁層上及び溝の表面に第1の金属層を形成する工程と、溝の内部及び上方に第2のマスクを形成する工程と、第1の金属層上及び第2のマスクの表面に第2の金属層を形成する工程と、第2のマスク及び第2のマスクの表面に形成された第2の金属層を除去する工程と、溝の上方が開口された第3のマスクを第2の金属層上に形成する工程と、溝の内部及び上方に第3の金属層を電界めっきにより形成する工程と、第3のマスクを除去する工程と、第3の金属層を化学機械研磨により平坦化する工程と、を備える。

(もっと読む)

絶縁膜への金属の平坦化埋め込み方法

【課題】研磨パッドを用いず、さらに砥粒を用いないスラリー液による絶縁膜への金属の平坦化埋め込み方法を提供する。

【解決手段】スラリー液に微細気泡(マイクロバブル)を分散させ、微細気泡の平均直径より微細な寸法のパターンを形成した基板に金属膜を堆積させ、微細気泡を分散したスラリー液に金属膜を堆積した基板を浸漬することにより、堆積した金属膜のうち凹部のものを残留させ、絶縁膜への金属の平坦化埋め込みを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】プラグの上面の形状を工夫することにより、半導体装置の電気的特性において、信頼性の向上を図ることができる技術を提供する。

【解決手段】本願発明におけるプラグPLGは、上面がコンタクト層間絶縁膜CILの表面(上面)よりも突出した上に凸のドーム形状をしている。つまり、プラグPLGは、上面が上に凸のドーム形状となっており、コンタクト層間絶縁膜CILの上面の高さよりもバリア導体膜BF1の上端部の高さが高く、かつ、タングステン膜WFの上端部の高さはバリア導体膜BF1の上端部の高さよりも高くなっている。

(もっと読む)

固体撮像装置およびその製造方法

【課題】本発明は、固体撮像装置に含まれる配線層間の絶縁膜の平坦性の向上に有利な技術を提供することを目的とする。

【解決手段】半導体基板上に、第1の配線層の導電パターンと、当該導電パターンの上部を覆う絶縁性を有する第1の研磨停止層とを形成する第1の形成工程と、第1の研磨停止層が形成された半導体基板上に層間絶縁層を形成する工程と、層間絶縁層の上に、半導体基板の少なくとも受光領域を覆うように絶縁性を有する第2の研磨停止層を形成する第2の形成工程と、導電パターンの上部を覆う第1の研磨停止層が少なくとも露出し、且つ受光領域を覆う第2の研磨停止層の少なくとも表面が研磨されるまで、第2の研磨停止層が形成された半導体基板の上側表面を平坦化するように研磨する研磨工程と、研磨された半導体基板に、第2の配線層の導電パターンを形成する工程とを含むことを特徴とする固体撮像装置の製造方法が提供される。

(もっと読む)

半導体装置及びその製造方法

【課題】比誘電率が小さい層間絶縁膜に形成された配線の配線密集部に生じるエロージョンを抑制して、比誘電率が小さい層間絶縁膜の露出を防止できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたELK膜12と、該ELK膜12の上に形成されたSiN膜13と、ELK膜12及びSiN膜13に形成され、実質的に同一の高さに配置された複数の配線16とを有している。複数の配線16は、単位面積当たりの配線占有率である第1の配線面積率を持つ配線非密集部Aと、第1の配線面積率よりも高い第2の配線面積率を持つ配線密集部Bとを有し、SiN膜13における配線密集部Bの上面の高さは、SiN膜13における配線非密集部Aの上面の高さよりも低い。

(もっと読む)

研磨方法

【課題】 二酸化珪素を主体とする層間絶縁膜とlow−k膜を、共に高速に研磨でき、更には、研磨傷が少なくできる研磨方法を提供する。

【解決手段】 表面に凹部及び凸部を有する層間絶縁膜と、この層間絶縁膜を被覆するバリア層と、前記凹部を充填し、バリア層を被覆する導電性物質層とを有する基板の研磨方法において、導電性物質層を研磨して前記凸部のバリア層を露出させる第1の化学機械研磨工程の後に、基板をショア硬度(Dスケール)で40以上のハードタイプパッド上に押圧した状態で、CMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、バリア層と凹部の導電性物質層と層間絶縁膜とを研磨し、更にショア硬度(Dスケール)で40未満のソフトタイプパッド上に押圧した状態で、上述のCMP用研磨液と同一組成のCMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、導電性物質層と層間絶縁膜を研磨する第2の化学機械研磨工程を行う研磨方法。

(もっと読む)

半導体装置の製造方法

【課題】配線抵抗の面内ばらつきを低減することが可能な半導体装置の製造方法を提供する。

【解決手段】低誘電率膜101上にキャップ絶縁膜102を形成し、キャップ絶縁膜および低誘電率膜の上部をエッチングして、配線層105aを形成する領域にキャップ絶縁膜を貫通して低誘電率膜にトレンチ103を形成する。トレンチ内およびキャップ絶縁膜上に、バリアメタル膜104と導電性材料を成膜する。バリアメタル膜をストッパとして導電性材料を第1のCMPにより平坦化する。次に、導電性材料に対する濡れ性が低誘電率膜に対する濡れ性よりも高いスラリーを用いた第2のCMPにより、導電体層、バリアメタル膜およびキャップ絶縁膜を研磨する。このとき、キャップ絶縁膜は途中まで研磨する。残ったキャップ絶縁膜をエッチング除去する。この後、バリア膜、層間絶縁膜を形成する。

(もっと読む)

強誘電体メモリ装置の製造方法

【課題】コンタクトプラグ上に直接形成される下地層の結晶配向性を良好にし、さらにこの下地層の平坦性をも良好にすることで、下部電極や強誘電体膜の結晶配向性の改善を図った強誘電体メモリ装置の製造方法を提供する。

【解決手段】基板の上方に導電性の下地層を形成する工程と、下地層の上方に第1電極と強誘電体膜と第2電極とを積層する工程と、を含む強誘電体メモリ装置の製造方法である。下地層の形成工程は、プラグ20を含む層間絶縁膜26上に、自己配向性を有する導電材料からなる導電層411を形成する工程と、導電層411を窒素雰囲気中で熱処理し、窒化導電層412とする工程と、窒化導電層412を、シリコン酸化膜研磨用のスラリーを用いたCMP法によって低研磨速度で平坦化処理し、プラグ20を含む層間絶縁膜26上を覆った状態の平坦化窒化チタン層41とする工程と、を含む。

(もっと読む)

配線構造の製造方法

【課題】金属キャップの横方向の成長を無くし、その選択的成長を良好に調整することが可能な配線構造の製造方法を提供する。

【解決手段】本発明の製造方法は、誘電体層30にダマシン構造を形成する工程と、導体50’として銅または銅合金によりダマシン構造を充填する工程と、導体50’の上表面を誘電体層30の上表面よりも低くするために、硝酸,次亜塩酸,或いはクロム酸からなる酸性の環境内で行われる洗浄処理により、導体50’の表面を陥凹させる工程と、導体50’の表面を陥凹させた後に、金属コバルト,コバルトタングステン,コバルトタングステンリン化物またはコバルトタングステンホウ化物からなるコバルト含有キャップ54を、凹んだ導体50’上に選択的成長によって形成する工程と、コバルト含有キャップ54と誘電体層30を覆ってエッチング停止層56を形成する工程と、からなる。

(もっと読む)

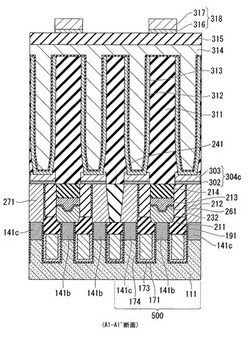

半導体素子の金属配線及びその形成方法

【課題】埋め込み金属配線の形成時に、イン-サイチュウ(in-situ)で平坦化を行うことができ、層間絶縁膜形成の回数を減らし、製造工程にかかる時間及び費用を減らすことができる半導体素子の製造方法を提供する。

【解決手段】半導体基板100上の第1の層間絶縁膜102にコンタクトプラグ104を形成する。第1の層間絶縁膜及びコンタクトプラグの上部にエッチング停止膜106a及びハードマスクパターンを形成する。ハードマスクパターンに沿ってエッチング停止膜をパターニングし、露出された第1の層間絶縁膜及びコンタクトプラグをエッチングしてコンタクトプラグの上部の第1の層間絶縁膜にトレンチを形成する。金属膜を形成後、エッチング停止膜までシリカ研磨剤とセリア研磨剤を混合したスラリーを用いて平坦化を行い、金属配線114aを形成する。エッチング停止膜を除去し、第2の層間絶縁膜116を形成する。

(もっと読む)

1 - 20 / 82

[ Back to top ]