Fターム[5F033QQ56]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611)

Fターム[5F033QQ56]の下位に属するFターム

Fターム[5F033QQ56]に分類される特許

1 - 3 / 3

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

埋め込み配線の形成方法

【課題】配線抵抗が低く、EM耐性及び信頼性に優れた埋め込み配線の形成方法を提供することにある。

【解決手段】半導体基板10上に形成された絶縁層11内に溝12を形成した後、溝12の側面及び底面を覆うように、絶縁層11上にALD法でバリアメタル層13を形成し、その表面に、イオン注入法またはALD法により不純物層14、17を形成する。その後、バリアメタル層13と不純物層14、17とを合金化した後、溝12内にCuシード層15及びCuメッキ層16からなる埋め込み配線層を形成し、然る後、合金化されたバリアメタル層13内の不純物元素を埋め込み配線層内に熱拡散させる。

(もっと読む)

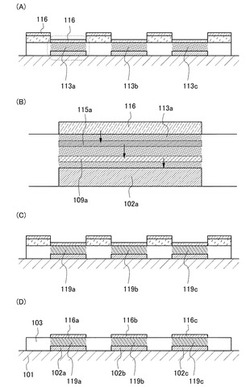

直接書き入れ方式のウェーハ修復方法

【課題】修復工程において直接書き入れ方式で処理することにより、時間および費用を節減する直接書き入れ方式のウェーハ修復方法を提供する。

【解決手段】次の工程を含む。半導体ウェーハ100から複数の欠陥領域の複数の位置およびパターンを探し出す。欠陥領域の位置およびパターンを直接書き入れツール220へ伝送する。半導体ウェーハ100上に、フォトレジスト層を形成する。エネルギービームを用いて、欠陥領域中のフォトレジストを局部的に露光する。半導体ウェーハ100上のフォトレジストを現像する。露光および現像の後、フォトレジスト層の下方にある半導体ウェーハ100を処理する。

(もっと読む)

1 - 3 / 3

[ Back to top ]