Fターム[5F033QQ60]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 絶縁膜 (83)

Fターム[5F033QQ60]に分類される特許

1 - 20 / 83

半導体装置

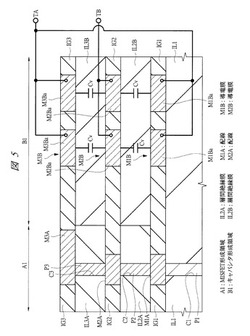

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域に歪みを導入して半導体装置の特性を向上するとともに、応力印加膜に覆われたゲート配線の断線を防止する。

【解決手段】半導体装置は、第1の素子形成領域101に形成された第1の活性領域104と、第2の素子形成領域102に形成された第2の活性領域105と、第1の活性領域104上から第2の活性領域105上に亘って延伸するゲート配線103と、第1の活性領域104のうちゲート配線103の直下領域に形成された第1のチャネル領域80と、第2の活性領域のうちゲート配線の直下領域に形成された第2のチャネル領域90とを備える。ゲート配線103は、第1の活性領域104上に形成され、引張り応力又は圧縮応力である第1の応力を有する第1の領域164と、第1の領域164よりも緩和された第1の応力を有する第2の領域162とを有している。

(もっと読む)

電気光学装置の製造方法

【課題】素子基板に絶縁膜を成膜した際にフッ素が混入しても、電界効果型トランジスターに特性異常が発生することを防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】素子基板10にシリコン酸化膜からなる絶縁膜12を成膜する第1絶縁膜成膜工程の後、画素トランジスター30(電界効果型トランジスター)の半導体層1aを形成する半導体層形成工程を行う前に、絶縁膜12に水素を導入する第1絶縁膜水素導入工程を行う。また、シリコン酸化膜からなる層間絶縁膜41を形成する第2絶縁膜成膜工程の後、層間絶縁膜41に対して水素の導入を行う第2絶縁膜水素導入工程を行う。このため、絶縁膜12や層間絶縁膜41にフッ素が混入していた場合でも、かかるフッ素は、水素と結合してフッ化水素として放出される。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】n型FET及びp型FET(電界効果トランジスター)のうち、一方のFETの電流駆動能力の低下を抑制し、他方のFETの電流駆動能力の向上を図る。

【解決手段】n型FET及びp型FETを覆うように、第1の膜を形成する工程と、その後、p型(n型)FET上の前記第1の膜に対して、イオン注入法によって選択的に不純物を打ち込む工程とを有し、n型(p型)FETのチャネル形成領域には、n型(p型)FET上の前記第1の膜によって、主として、n型(p型)FETのゲート電極のゲート長方向に引張(圧縮)応力が発生しており、不純物を打ち込む工程によって、前記p型(n型)FETのチャネル形成領域に発生する引張(圧縮)応力は、n型(p型)FETのチャネル形成領域に発生する引張(圧縮)応力よりも小さくなっている。

(もっと読む)

固定用構造および嵌合構造

【課題】チップの縁領域は、膨張係数が異なることによって、温度サイクル中に、TC応力とも称される特定の負荷を受けることが多い。これらの縁領域は特にTC応力を受け易いため、同領域内において様々な不良が生じる可能性がある。これによって、実際のデバイスにおける信頼性のリスクが増大する可能性がある。

【解決手段】半導体デバイスの金属構造210のための固定用構造200は、オーバーハング形状の側壁230を少なくとも1つ含んだ固定用凹部構造220を含んでいる。上記金属構造210は、少なくとも部分的に上記固定用凹部構造220内に配置されている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】第2の層間絶縁膜14に、配線の上面を露出するように、第1の開口径とされた第1の開口部16、及び第1の開口径よりも小さい第2の開口径とされた第2の開口部17を一括形成し、次いで、第1及び第2の開口部の内面を覆う高誘電率絶縁膜19を成膜し、次いで、斜めイオン注入法により、第2の開口部の底面に形成された高誘電率絶縁膜にイオンが注入されないように、少なくとも第1の開口部の底面の外周に形成された高誘電率絶縁膜にイオンを注入し、その後、ウエットエッチングにより、イオンが注入された高誘電率絶縁膜を除去し、次いで、第1及び第2の開口部内を導電膜21で埋め込むことで、第1の開口部内にコンタクトプラグ22を形成すると共に、前記第2の開口部内に、第2の開口部に高誘電率絶縁膜及び導電膜よりなるアンチヒューズ素子23を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】溝部を絶縁膜で埋設する際に、溝部のアスペクト比が大きい場合であっても、内部にボイドを残存させることなく、溝部内に絶縁膜を充填する。これにより微細化した半導体装置の製造を容易に行うことを可能とする。

【解決手段】隣り合う凸部の間に形成される溝部の上端部においてオーバーハング形状を有すると共に、溝部の上部にボイドを有するように溝部内に溝部用絶縁膜を形成する。凸部の高さ方向に対して斜め方向から、溝部用絶縁膜に不純物をイオン注入することにより、溝部内に形成された溝部用絶縁膜の一部に不純物をドープする。溝部用絶縁膜の不純物がドープされた部分を除去した後、溝部内に溝部用絶縁膜を充填する。

(もっと読む)

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置の製造方法及び成膜装置

【課題】バリアメタル膜の酸化を十分に抑制することができる半導体装置の製造方法及び成膜装置を提供する。

【解決手段】基板1の上方に導電膜5を形成し、導電膜5を覆う絶縁膜7を形成し、絶縁膜7のエッチングを行って、絶縁膜7に導電膜5の少なくとも一部を露出する開口部51を形成する。また、還元ガス雰囲気中で開口部51に紫外線を照射し、開口部51内に絶縁膜7及び導電膜5に接するバリアメタル膜9を形成し、バリアメタル膜9上に導電膜10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 膜ストレス低減を図った無機SOG膜を有した半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された下層配線3と、前記下層配線3上及び下層配線3間に形成され、不純物がイオン注入されることで圧縮応力を示す無機SOG膜5aと、前記無機SOG膜5aを含む層間絶縁膜7に形成されたコンタクトホールを介して前記下層配線に接続する上層配線とを具備することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

コンタクト構造体を有する半導体素子の製造方法

【課題】 コンタクト構造体を有する半導体素子の製造方法を提供する。

【解決手段】 この製造方法は半導体基板上に絶縁膜を形成する第1工程と、前記絶縁膜の所定領域内に選択的に不純物イオンを注入して前記絶縁膜の前記所定領域内に格子欠陥(lattice defects)を生成する第2工程とを含む。さらに、格子欠陥を有する絶縁膜を熱処理して前記所定領域内の格子欠陥の生成を加速する第3工程を含む。その結果、前記所定領域内に電流通路(current paths)を有する導電性の領域が形成される。前記第3工程は前記絶縁膜を少なくとも20℃/min以上の温度変化率で急冷する段階を含む。

(もっと読む)

半導体装置

【課題】温度が上昇するほど電子又はホールの移動度を向上できる半導体装置を提供する。

【解決手段】半導体装置は、半導体基板中のPウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Pウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ負の膨張係数を有しチャネル領域に引っ張り応力を加える第1絶縁層20を備えたN型の絶縁ゲート型電界効果トランジスタN1と、半導体基板中のNウェル上に設けられたゲート電極と、前記ゲート電極を挟むように前記Nウェル中に隔離して設けられたソースまたはドレインと、前記ソースまたはドレイン上から前記ゲート電極上に亙って設けられ正の膨張係数を有しチャネル領域に圧縮応力を加える第2絶縁層30を備えたP型の絶縁ゲート型電界効果トランジスタP1とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率膜に対するUVキュア処理による低誘電率膜の下で且つ配線の上に形成されるライナ膜とその下層の膜との間の界面剥離を、UVブロッキング膜を用いずに防ぐことにより、高歩留まりの配線構造を有する信頼性が高い半導体装置を得られるようにする。

【解決手段】基板の上に、第1の絶縁膜11を形成し、形成した第1の絶縁膜11の上部に第1の金属配線12を形成し、第1の絶縁膜11の上に、第1の金属配線12を覆うように第2の絶縁膜13を形成し、第2の絶縁膜13に対して膜質の改質処理を行う。その後に、第2の絶縁膜13の上に第3の絶縁膜14を形成し、形成した第3の絶縁膜14に対してキュア処理を行う。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

1 - 20 / 83

[ Back to top ]