Fターム[5F033QQ64]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入するもの (714) | 窒素系 (42)

Fターム[5F033QQ64]に分類される特許

1 - 20 / 42

半導体装置の作製方法及び半導体装置

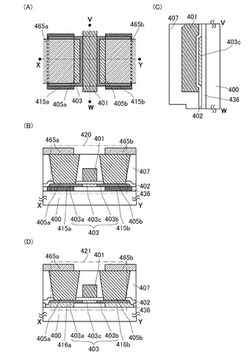

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

Cu膜の形成方法

【課題】バリアメタル膜とCu膜との密着性を向上する。

【解決手段】基板上に、スパッタ法によりバリアメタル膜としてTi膜又はTa膜を形成し、このバリアメタル膜上にスパッタ法により窒化物膜を形成し、この窒化物膜の上にCVD法によりCu膜を形成した後、100〜400℃でアニール処理を行う。このようにCu膜を形成することにより、バリアメタル膜とCu膜との密着性が向上する。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体デバイス用基板およびSOI基板

【課題】 裏面研削加工および裏面CMP処理が施されて製造される薄型半導体デバイスに用いられる半導体デバイス用基板であって、裏面研削を過不足なく行うことが可能であるとともに、研削加工の高速化を図ることができて、生産効率を向上させることができる半導体デバイス用基板を提供することである。

【解決手段】 半導体デバイス用基板10は、結晶性のシリコン基板11の内部に、構造変化層12が形成されたものである。この構造変化層12は、導電型領域を形成することがないイオンが注入されてなる層であって、シリコンとは異なる結晶構造に変化した層である。

(もっと読む)

半導体装置の製造方法

【課題】低誘電率膜に対するUVキュア処理による低誘電率膜の下で且つ配線の上に形成されるライナ膜とその下層の膜との間の界面剥離を、UVブロッキング膜を用いずに防ぐことにより、高歩留まりの配線構造を有する信頼性が高い半導体装置を得られるようにする。

【解決手段】基板の上に、第1の絶縁膜11を形成し、形成した第1の絶縁膜11の上部に第1の金属配線12を形成し、第1の絶縁膜11の上に、第1の金属配線12を覆うように第2の絶縁膜13を形成し、第2の絶縁膜13に対して膜質の改質処理を行う。その後に、第2の絶縁膜13の上に第3の絶縁膜14を形成し、形成した第3の絶縁膜14に対してキュア処理を行う。

(もっと読む)

ビアホールの形成方法

【課題】異なる種類の絶縁体が積層された構造を有する絶縁膜に、高精度の加工形状を有するビアホールを形成することができるビアホールの形成方法を提供する。

【解決手段】

ドライエッチングによって第2の絶縁層に第1の貫通孔を形成する工程と、第1の絶縁層及び第2の絶縁層の第1の貫通孔からの露出部分を同一組成からなる絶縁体にする同一化工程と、第1の貫通孔から露出する第1の絶縁層をドライエッチングにより除去して下層配線に達するビアホールを形成する工程と、を有すること。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜の表面に対するダメージを防ぎ、配線膜厚を均一に制御することにより、配線間ショート及び信頼性劣化を防止できるようにする。

【解決手段】半導体基板101の上に絶縁膜102を形成し、絶縁膜102の内部にイオン注入法によりイオン注入層103を形成し、絶縁膜102に少なくともイオン注入層103に達する深さの配線溝104を形成し、配線溝104に導電膜107Aを形成し、絶縁膜102及び導電膜107Aにおけるイオン注入層103よりも上に形成されている領域を除去する。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

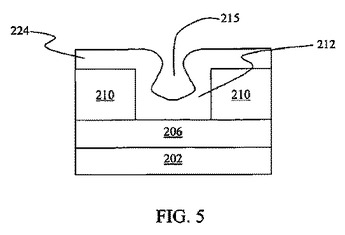

半導体装置及びその製造方法

【課題】不純物層が浅く形成された場合にも接合リーク電流の増大を抑制できるようにすると共に、コンタクトホール形成時に位置合わせずれが生じた場合にもコンタクト抵抗の上昇を抑制できるようにする。

【解決手段】基板100上に素子分離領域102及び不純物層103が互いに隣接するように形成されている。不純物層103上にシリサイド層106Bが形成されており、シリサイド層106B上に形成されたコンタクト109が形成されている。不純物層103とシリサイド層106Bとの界面は、素子分離領域102の上面よりも低く、シリサイド層106Bは素子分離領域102の上部コーナーを覆っている。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

カーボンナノチューブを利用した半導体素子の配線形成方法およびその方法により製造された半導体素子

【課題】高い電流密度を持つカーボンナノチューブを利用した半導体素子の配線形成方法、およびその方法により製造される超高集積度の半導体素子を提供する。

【解決手段】半導体素子の電極120表面を前処理して活性化させる段階と、電極の活性化した表面122上に絶縁層130を形成した後、電極の活性化した表面の一部を露出させるために絶縁層を貫通するコンタクトホール132を形成する段階と、コンタクトホールを通じて電極の活性化した表面に炭素が含まれているガスを供給して前記電極の活性化した表面からカーボンナノチューブ140を成長させて配線を形成する段階と、を具備する半導体素子の配線形成方法およびその方法により製造された半導体素子。

(もっと読む)

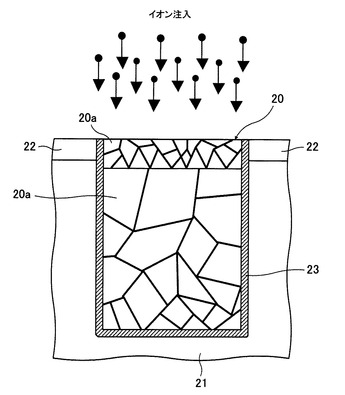

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】炭化珪素半導体装置100aの製造方法は、以下の工程を備えている。まず、炭化珪素半導体層110が準備される。そして、炭化珪素半導体層110の表面に、金属層が形成される。そして、金属層を熱処理することにより電極150が形成される。そして、電極150の表面の炭素を除去するためのエッチングが行なわれる。金属層を形成する工程では、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い金属層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】Wを材料とする接続部の下地膜の形成工程として、形成容易なプロセスを選択することができ、下層のCu配線である第1の配線のCuの浸食を抑制することにより、第1の配線と接続部との間における接触抵抗を低く抑えるとともにその均一性を高め、信頼性の高い半導体装置を実現する。

【解決手段】熱CVD法によりWF6、H2及びB2H6を含有し、シラン系ガスを含有しない第1の供給ガスを用いてW膜18aを形成した後、WF6及びH2を含有する第2の供給ガスを用いてW膜18bを形成し、CMPを経て、ビア孔16をW膜18で充填するWプラグ19を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】同一配線層の配線間における実効誘電率の増大及び配線幅のばらつきの増加を解消しつつ、ナノホールパターンの形成時における反射率差に起因する課題と、エッチングによる配線信頼性低下の課題とを同時に解決できるようにする。

【解決手段】半導体装置は、半導体基板の主面に垂直な方向に筒状に延びる複数の空間部である第1のナノコラム型ホール11bを有する第1の層間絶縁膜11と、該第1の層間絶縁膜11に選択的に形成された下層配線12とを有している。下層配線12の上部には、金属又は金属を含む材料からなるキャップ膜12cが形成されている。

(もっと読む)

1 - 20 / 42

[ Back to top ]