Fターム[5F033QQ66]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入するもの (714) | ハロゲン (19)

Fターム[5F033QQ66]に分類される特許

1 - 19 / 19

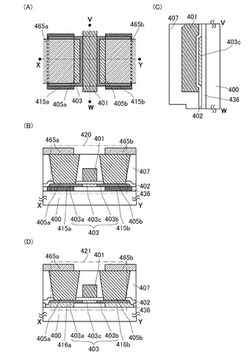

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することの可能な半導体装置の製造方法を提供する。

【解決手段】第2の層間絶縁膜14に、配線の上面を露出するように、第1の開口径とされた第1の開口部16、及び第1の開口径よりも小さい第2の開口径とされた第2の開口部17を一括形成し、次いで、第1及び第2の開口部の内面を覆う高誘電率絶縁膜19を成膜し、次いで、斜めイオン注入法により、第2の開口部の底面に形成された高誘電率絶縁膜にイオンが注入されないように、少なくとも第1の開口部の底面の外周に形成された高誘電率絶縁膜にイオンを注入し、その後、ウエットエッチングにより、イオンが注入された高誘電率絶縁膜を除去し、次いで、第1及び第2の開口部内を導電膜21で埋め込むことで、第1の開口部内にコンタクトプラグ22を形成すると共に、前記第2の開口部内に、第2の開口部に高誘電率絶縁膜及び導電膜よりなるアンチヒューズ素子23を形成する。

(もっと読む)

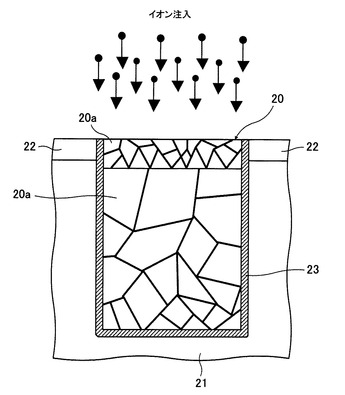

半導体装置及びその製造方法

【課題】貫通電極を有する半導体装置の信頼性を向上させる。

【解決手段】半導体基板1は、素子形成面である第1の面1a及びその反対側の第2の面1bを有する。第1の面1aから第2の面1bまで半導体基板1を貫通するように貫通孔20が形成されている。貫通孔20の内壁上に絶縁膜21及びバリア膜22が順次形成されている。絶縁膜21及びバリア膜22が形成された貫通孔20が埋まるように導電部23が形成されている。貫通孔20の周辺に位置する部分の半導体基板1における少なくとも第1の面1a側にゲッタリングサイト30が形成されている。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

アレイ基板及びアレイ基板の製造方法

【課題】製造歩留まりの高いアレイ基板及びアレイ基板の製造方法を提供する。

【解決手段】アレイ基板1は、チャネル層19と、ゲート絶縁膜21と、ゲート配線と、ゲート電極23と、層間絶縁膜25と、非晶質シリコン層27aと、データ配線と、を備えている。データ配線は、非晶質シリコン層27aに積層され、金属で形成され、ゲート絶縁膜21及び層間絶縁膜25に形成されたコンタクトホールh1を介してチャネル層19に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

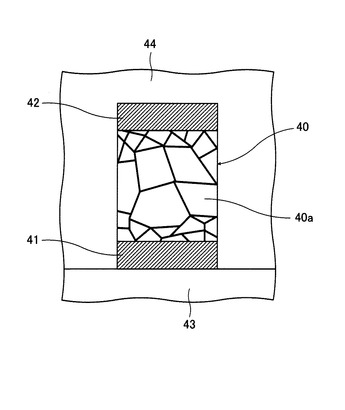

半導体装置及びその作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子と、半導体素子上の絶縁膜と、絶縁膜中に、欠陥の多い領域と欠陥の少ない領域とを有し、欠陥の多い領域は、金属元素が拡散され、絶縁膜の表面の一部と裏面の一部をつなぐ導電領域である半導体装置、及び、基板上に半導体素子を形成し、半導体素子上に絶縁膜を形成し、絶縁膜上に、半導体素子と電気的に接続された第1の導電膜を形成し、絶縁膜中にイオンを添加して、あるいはレーザビームを照射して、欠陥の多い領域を形成し、欠陥の多い領域上に、金属元素を含む導電材料を形成し、欠陥の多い領域に、金属元素を拡散させ、絶縁膜中に、第1の導電膜と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

半導体装置及びその製造方法

【課題】ICチップなどの半導体チップをより薄型化することが可能な技術を提供する。

【解決手段】集積回路が形成された半導体基板をCMP等により研磨し、半導体基板中に脆化層を形成して半導体基板の一部を分離することにより半導体基板を薄膜化して、従来にない薄さのICチップなどの半導体チップを得る。また、このような薄膜化したICチップに設けられた配線と、インターポーザに設けられた配線とを、導電性材料又はめっき処理により形成される導電膜を介して電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】LSIチップなどの半導体チップをより薄型化することが可能な技術を提供する。また、三次元半導体集積回路において、LSIチップをより薄型化して積層することで集積密度を向上させることが可能な技術を提供する。

【解決手段】LSIなどの集積回路が形成された半導体基板をCMP等により研磨し、半導体基板中に脆化層を形成して半導体基板の一部を分離することにより半導体基板を薄膜化して、従来にない薄さのLSIチップなどの半導体チップを得る。また、このような薄型化したLSIチップを積層し、半導体基板を貫通する配線によって電気的に接続することで、集積密度が向上した三次元半導体集積回路を得る。

(もっと読む)

半導体装置およびその製造方法

【課題】Cu配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Cu配線10を、その中央部のCu粒子10aが比較的大きく、その上部や下部のCu粒子10aが比較的小さくなるような構造にする。このような構造は、Cu配線10をダマシン法により形成する際の電解めっき時の電流密度を制御することによって形成することができる。このような構造にしたCu配線10では、その上部よりも中央部に比較的電流が流れやすくなり、その上部のCu原子の拡散が抑えられるようになり、また、それにより、キャップ膜14界面からのCu原子の拡散が抑えられるようになる。

(もっと読む)

半導体装置の製造方法

【課題】 半導体基板上に形成された配線に密の領域と疎の領域とがあったとしても、研磨によって、配線上に形成された層間絶縁膜上における各領域上の段差を少なくすることができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板12上の、アルミ配線14が密集して形成された第1領域16とアルミ配線14が形成されていない第2領域17と、の上に形成された第1層間絶縁膜13上に、第2層間絶縁膜15を形成する工程と、第2層間絶縁膜15上における第1領域16の上方の凸状の部分15bに、研磨速度を上げるべく不純物23の注入及び拡散を行う工程と、凸状の部分15bを含む第2層間絶縁膜15の上面をCMP研磨によって平坦化する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 銅配線のEM耐性とSM耐性を、ともに向上させる。

【解決手段】 不純物を含む銅めっき膜をシリコン基板1の上に成膜した後、銅めっき膜を結晶成長させて、複数の銅結晶粒とそれらの粒界に分布する不純物層とで構成された第一銅膜9cを形成する。次に、第一銅膜9cより不純物濃度が高い第二銅膜10を第一銅膜9cの上に形成し、第二銅膜10に含まれる不純物を第一銅膜9cに拡散させて、第一銅膜9cの結晶粒界に偏析する不純物濃度を高める。

このように形成することにより、第一銅膜9cの結晶粒の粒径は十分に大きくなる。これにより、結晶粒界における拡散パスを減少させ、EM耐性を向上させることができる。また、第一銅膜9cに発生するボイドの移動を抑え、SM耐性を向上させることができる。

(もっと読む)

貫通電極の形成方法、貫通電極および半導体装置

【課題】 工数や手間の増大を招くことなく、半導体基板の汚染を防止できる貫通電極の形成方法を提供すること。

【解決手段】 シリコン基板1に非貫通孔を形成し、この非貫通孔の底面からシリコン基板1に不純物を添加して、不純物添加部2を形成する。非貫通孔の側面および底面に表面側絶縁膜3を形成し、表面側絶縁膜3の内側に埋め込み電極4を形成する。シリコン基板1の裏面部分を除去して、不純物添加部2を裏面に露出させる。シリコンに対してエッチングレートが高いエッチングによって、不純物添加部2を、埋め込み電極4に対してセルフアライメントした状態で除去できる。

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

1 - 19 / 19

[ Back to top ]