Fターム[5F033QQ72]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱処理の対象 (3,254)

Fターム[5F033QQ72]の下位に属するFターム

Fターム[5F033QQ72]に分類される特許

1 - 20 / 31

導電膜除去方法および導電膜除去剤

【課題】エッチング工程設備へ与える腐食性の負荷を減らし、かつ作業者の安全性に優れた、汎用性の高い、エッチング跡の変色等の生じない、導電膜除去剤および導電膜除去方法を提供することを目的とする。

【解決手段】本発明は、導電膜付き基材の少なくとも一部に、20℃におけるpHが6.0〜8.0の導電膜除去剤を塗布する工程、導電膜除去剤を塗布した導電膜付き基材を加熱処理する工程、および加熱処理した導電膜付き基材から液体を用いた洗浄によって導電膜を除去する工程を有する導電膜除去方法であって、加熱処理する工程において塗布された導電膜除去剤の少なくとも一部の成分が揮発することで該導電膜除去剤のpHを6.0未満、または8.0より大きくすることを特徴とする導電膜除去方法である。

(もっと読む)

半導体装置の製造方法

【課題】感光性樹脂膜を塗布した後のパターン形成不良を抑制する。

【解決手段】まず、基板上に、配線を形成する(S110)。次いで、配線上にパッシベーション膜を形成する(S120)。次いで、基板をアニールする(S130)。次いで、基板をアニールする工程(S130)の後、パッシベーション膜上に、感光性樹脂膜として、フォトレジスト膜を塗布する(S140)。次いで、フォトレジスト膜が塗布された基板を少なくとも一回以上ベークする(S150)。次いで、フォトレジスト膜を、露光および現像によりパターニングする(S160)。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、簡便に形成できて、チャージアップしにくいハードマスクを用いた半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体装置の製造方法であって、半導体基板上に形成された被加工膜上に、アミン化合物と水素化アルミニウムとの錯体を含有するアルミニウム膜形成用材料を塗布して、塗布膜を形成する工程と、前記塗布膜に対して、加熱処理および光照射処理から選ばれる少なくとも一種の処理を行いアルミニウム膜を形成する工程と、 該アルミニウム膜をエッチングしてハードマスクを形成する工程と、前記ハードマスクをマスクにして被加工膜をエッチングする工程を有することを特徴とする。

(もっと読む)

半導体記憶装置

【課題】さらなるDRAMの大記憶容量化を図る。

【解決手段】半導体記憶装置が、単結晶半導体材料を含む基板の一部を有する駆動回路と、当該駆動回路上に設けられる多層配線層と、当該多層配線層上に設けられるメモリセルアレイ層とを有する。すなわち、当該半導体記憶装置においては、駆動回路と、メモリセルアレイとが重畳して設けられる。したがって、単結晶半導体材料を含む基板に駆動回路及びメモリセルアレイを同一平面に設ける場合と比較して、当該半導体記憶装置の集積度を高めることが可能となる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

成膜方法、半導体装置及びその製造方法、並びに基板処理装置

【課題】真空装置を使用せずに、トランジスタ等の半導体装置に適用できるMOS構造の積層膜を形成する。

【解決手段】成膜方法は、半導体膜3を有する基板に、ポリシラン溶液を塗布し、半導体膜3上にポリシラン膜5を形成する工程(STEP1)と、ポリシラン膜5上に、金属塩溶液を塗布し、金属イオン含有膜7を形成することにより、ポリシラン膜5をポリシロキサン膜5Aへ、金属イオン含有膜7を金属微粒子含有膜7Aへ、それぞれ改質する工程(STEP2)を備え、MOS構造の積層膜100を形成する。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィ時のフォトマスクの位置合わせを十分な精度で行うことが可能となる位置合わせ用の目合わせパターンを形成することを課題とする。

【解決手段】基板1上に第1絶縁層2を形成する工程と、第1絶縁層2に、1つ以上の接続孔4と、接続孔4よりも幅が広い位置合わせ用の目合わせパターンを形成するための目合わせ孔3と、を形成する工程と、第1絶縁層2の上に、接続孔4が金属で完全に埋まり、かつ、目合わせ孔3が金属で完全に埋まらないよう金属膜5を形成する工程と、金属膜5の上に、少なくとも目合わせ孔3が完全に埋まるように第1フォトレジスト膜6を形成する工程と、第1絶縁層2をストッパーとしてCMP処理を行うことで、第1フォトレジスト膜6及び金属膜5の一部を除去する工程と、を有する半導体装置の製造方法を提供する。

(もっと読む)

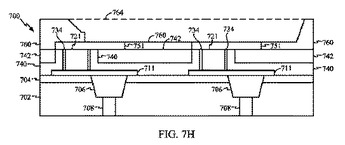

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

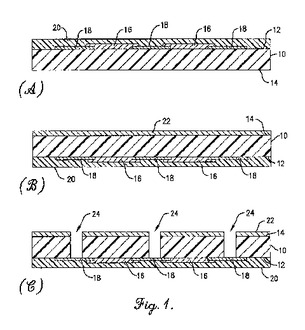

背面処理中に前面側電気回路を保護するための耐傷性コーティング

マイクロエレクトロニクスメカニカルおよび半導体デバイス特徴の前面側を保護する、耐傷性コーティングを、その使用方法とともに提供する。上記コーティングは、非感光性で、除去可能であり、高い処理温度に耐える。また、これらのコーティングは、デバイス設計において、別個のエッチング停止層を不要とする。上記コーティングは、溶媒系に溶解または分散した成分を含有する組成物から形成される。上記成分は、スチレンアクリロニトリル共重合体および芳香族スルホンポリマーからなる群から選択される。  (もっと読む)

(もっと読む)

薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物

【課題】パターンの不良が減少した薄膜トランジスタ表示板の製造方法およびこれに使用されるネガティブフォトレジスト組成物を提供する。

【解決手段】基板上に導電性物質からなる導電膜を形成する段階と、導電膜上にネガティブフォトレジスト組成物からなるエッチングパターンを形成する段階と、エッチングパターンをエッチングマスクとして利用して導電膜をエッチングし、導電膜パターンを形成する段階とを含み、ネガティブフォトレジスト組成物は、アルカリ現像液に溶解性を有するヒドロキシル基を含有するノボラック樹脂10〜50重量部、第1光酸発生剤(特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、第2光酸発生剤(第1光酸発生剤とは構造の異なる特定構造のスルホニルオキシイミド化合物)0.5〜10重量部、架橋結合剤1〜20重量部および溶媒10〜90重量部を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

コバルトカルボニル錯体組成物及びコバルト膜の形成方法

【課題】コバルト前駆体の保存安定性に優れ、長期保存後に化学気相成長法に供した場合であっても昇華残存物の少ないコバルト前駆体組成物及びコバルト前駆体の使用効率の高い、化学気相成長法によるコバルト膜の形成方法を提供すること。

【解決手段】上記組成物は、コバルトカルボニル錯体及び溶媒を含有する組成物であって、前記溶媒に溶存する一酸化炭素の濃度が0.001〜1重量%であることを特徴とする。上記方法は、上記のコバルトカルボニル錯体組成物に由来するコバルトカルボニル錯体を昇華して基体上に供給し、該基体上で該コバルトカルボニル錯体をコバルトに変換することを特徴とする。

(もっと読む)

表示装置およびその製造方法

【課題】 TFT液晶表示装置の動作不良や動作特性のばらつきを低減する。

【解決手段】 絶縁基板の表面上に複数の導電体パターンと、複数の半導体パターンと、複数の絶縁膜とを積層して、当該絶縁基板の表面上に走査信号線と、映像信号線と、TFT素子と、前記TFT素子に接続された画素電極と、前記映像信号線に接続された第1の外部接続端子と、前記走査信号線に接続された第2の外部接続端子とを設けた基板を有する表示装置であって、前記絶縁基板の表面上には、1つの材料膜をエッチングまたは露光現像して形成された複数の同時形成パターンを有し、当該複数の同時形成パターンは、同一の機能を有する前記同時形成パターンの側面の勾配が概ね等しく、かつ、すべての前記同時形成パターンの側面の勾配には2通り以上ある表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】エアギャップにビアが侵入することを防止すると共に配線間容量のさらなる低減を図り、また、空隙部を有する多層配線構造の機械的強度の向上及び酸化性物質の拡散防止を図り、歩留まりの低下を抑止できるようにする。

【解決手段】半導体装置は、第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の第1の配線105とを有している。第1の層間絶縁膜101における複数の第1の配線105の隣り合う配線同士の間には、空隙部112が選択的に形成されており、空隙部112の上で且つ配線同士の間に形成されたキャップ絶縁膜111が形成されている。空隙部112における下端部の幅及び上端部の幅は、空隙部112と隣接する配線同士の間隔と同一であり、空隙部112の下端部の位置は、該空隙部112と隣接する第1の配線105の下端部の位置よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】本発明の課題は、電極や配線の周囲に空間部を形成するに際し、電極材料や配線材料が耐フッ酸性がない材料であっても適用でき、かつ有機汚染の心配のない半導体装置の製造方法を提供することである。

【解決手段】本発明の半導体装置の製造方法は、ゲート電極21aの周囲を昇華性を有する材料としての塩化アルミニウム膜22aからなる犠牲膜で被覆し、その犠牲膜の周囲を外殻層としてのSiN膜23で被覆し、外殻層に設けた開口部24を通して犠牲膜をその昇華温度以上に加熱し除去して、ゲート電極21aの周囲に空間部25を形成する。

(もっと読む)

半導体装置の製造方法

【課題】ビアの密度の変動による上部配線の厚さの変動を低減し、歩留りや信頼性の高い半導体装置を提供することを目的としている。

【解決手段】埋め込みプラグ107を形成後、埋め込みプラグ107を成長させるか、もしくは、埋め込みプラグ107の表面に貼り付けプラグを形成することにより、ビアの密度が高い領域で発生している第2絶縁膜104の表面と埋め込みプラグ107の表面の段差が緩和もしくは解消され、反射防止膜108厚を一定とすることができるので、ビアの密度の変動により上部配線の厚さが変動する現象を低減することができ、歩留りや信頼性の高い半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上での抵抗が十分に高く、且つ銅配線上での抵抗が十分に低いキャップ層を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】シリコン基板1上に第3の層間絶縁膜10を形成する工程と、第3の層間絶縁膜10に第1の配線溝10aを形成する工程と、第1の配線溝10aに銅を埋め込んで第1、第2の銅配線12a、12bにする工程と、第3の層間絶縁膜10と第1、第2の銅配線12a、12bの上に、希ガスと窒素ガスとの混合ガスを用いる反応性スパッタ法により、キャップ層13として窒化ジルコニウム層を形成する工程とを有し、第3の層間絶縁膜10上に形成されるキャップ層13は、比抵抗が1×109μΩ・cm以上となるように形成される半導体装置の製造方法による。

(もっと読む)

カーボンナノチューブの形成方法、及びそれを利用した半導体素子の配線形成方法

【課題】カーボンナノチューブの形成方法及びそれを利用した半導体素子の配線形成方法を提供する。

【解決手段】(i)複数の突起部を有する基板を準備する段階と、(ii)前記基板上に、前記突起部を覆い、カーボンナノチューブの成長を促進させる触媒層を形成する段階と、(iii)前記触媒層上にカーボンが含まれるガスを注入して、前記触媒層の表面上に前記カーボンナノチューブを成長させる段階と、を含むカーボンナノチューブの形成方法である。本発明によれば、カーボンナノチューブの成長密度を上昇させて電気的抵抗を低下させうる。その結果、電流密度が上昇し、微細ビアホールにも適用可能で、半導体素子の超高集積化を達成しうる配線形成方法が提供される。

(もっと読む)

1 - 20 / 31

[ Back to top ]