Fターム[5F033QQ79]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 熱処理 (5,181) | 熱拡散 (194)

Fターム[5F033QQ79]の下位に属するFターム

固相拡散 (157)

Fターム[5F033QQ79]に分類される特許

1 - 20 / 37

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】微細配線においてボイドの発生を確実に防ぐ。

【解決手段】層間絶縁膜102、103に形成された開口部12の底面及び側壁、並びに、開口部12以外の層間絶縁膜103上にあるフィールド部に、第一の金属を含むシード膜を形成し、シード膜上にレジストを形成して、開口部12をレジストで埋め込んだ後、開口部12の底面上に形成されたシード膜にレジストを残しつつレジストの一部を除去して、開口部12の側壁202A、Bの上部からフィールド部203にわたって形成されたシード膜を露出させ、開口部12の側壁の上部、及び、フィールド部203に位置するシード膜上に、第一の金属よりも抵抗率が高い第二の金属を含むカバー膜を形成した後、レジストを除去してシード膜を露出させ、露出させたシード膜に、第一の金属を含むめっき膜を形成するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】埋め込み絶縁層により活性層と支持基板とが電気的に絶縁された半導体基板において、支持基板の電位を活性層の表面から取り出すための基板コンタクトの低抵抗化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】活性層16に素子領域4およびコンタクト領域5が形成された厚膜SOI基板2において、CMOSトランジスタ7のB/L層29およびL/I層37、npnバイポーラトランジスタ8のコレクタ層49と同一層に、n型基板コンタクト12の貫通コンタクト58を取り囲むn型コンタクト埋め込み層57を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

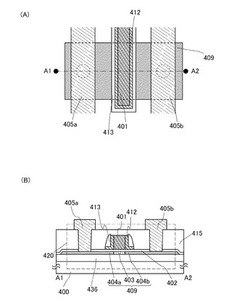

タンタルチューブとPIT炭素芯の製造方法、タンタルチューブとPIT炭素芯、タンタル炭化物配線の製造方法及びタンタル炭化物配線

【課題】簡易な方法で、所定の形状のタンタルと炭素との固相拡散接合を可能とし更に、タンタルと炭素の固相拡散接合を行う場所以外のタンタル表面に炭化物を形成する方法を提供する。

【解決手段】タンタル若しくはタンタル合金をチューブ状の形状に加工し、チューブの中に炭素粉末を圧入し、その後、チューブをコイル形状に加工した後に真空熱処理炉内に設置し、タンタル若しくはタンタル合金表面に形成されている自然酸化膜であるTa2O5を除去した後、タンタル若しくはタンタル合金チューブ内面と前記炭素粉末PITを固相拡散結合で分子接合させるとともに、前記真空熱処理炉内に炭素源を導入してタンタル若しくはタンタル合金チューブの外表面に炭素を侵入させてTaCを形成する。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

ダマシンインターコネクトのエレクトロマイグレーション抵抗を向上させる界面層

【課題】、ダマシンインターコネクトのエレクトロマイグレーション特性を向上させるべく銅線内に保護キャップを形成する方法を提供する。

【解決手段】a)酸化物を含まない銅または銅合金107の露呈領域と誘電体の露呈領域とを含む基板100を、アルミニウムを含む化合物に、少なくとも約摂氏350度の基板温度で曝して、前記誘電体および前記銅または銅合金の層の両方の上にアルミニウムを含む第1の層を形成する工程と、(b)前記第1の層の少なくとも一部を化学的に修正して、アルミニウムを含むパッシベーション層109を形成する工程と、(c)前記パッシベーション層の上に誘電体層111.を堆積させる工程とを備える方法。

(もっと読む)

電子モジュールの製造方法、および、電子モジュール

半導体基板に集積された回路と、基板と、ヒートシンクとしての支持体と、基板および支持体をはんだ付けにより接続する熱伝導性接続部とを備えた電子モジュールを提案する。ここでは、基板で用いられる後面金属化部として、まず第1の厚いAu層(23)、ついでバリア層(24)、最後に第2の薄いAu層(25)が堆積される。バリア層の材料は、はんだ付け過程において、第2のAu層の領域のAuSn液相のSnないしAuSnが第1のAu層(23)へ浸入することを阻止するように選定される。また、基板の貫通孔にも、後面金属化部の積層体が堆積される。ここで、第2のAu層の表面は、バリア層から拡散する材料によって、はんだ付け材料に対する低減された濡れ性を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】自己整合的にバリア膜を形成する配線構造の信頼性を向上できるようにする。

【解決手段】半導体基板の上に酸素及び炭素を含む層間絶縁膜11を形成し、該層間絶縁膜11に溝部13を形成し、溝部13の底面上及び側壁上に所定の第1の金属元素及び第2の金属元素を含む補助膜14を形成し、熱処理を行い、銅を主成分とする配線本体層19を、溝部13の内部を埋め込むように形成する。熱処理を行うことにより、補助膜14中の第1の金属元素を補助膜14と対向する層間絶縁膜11に拡散させ、溝部13の底面及び側壁における層間絶縁膜11の上において、第1の金属元素と層間絶縁膜11の酸素元素との化合物を主成分とする第1のバリア膜15を形成させた後、補助膜14中の第2の金属元素が補助膜14と対向する層間絶縁膜11に拡散させ、第2の金属元素と層間絶縁膜11の炭素元素との化合物を主成分とする第2のバリア膜17を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】 CVD−MnOxをバリア膜に用いても歩留りの低下を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】 N層以上の銅、又は銅合金配線4、8を有し、これらN層の銅、又は銅合金配線4、8のバリア膜としてCVD−MnOx膜を使用する半導体装置の製造方法であって、第1層乃至第N−1層のCVD−MnOx膜3は、セルフリミットがかかる前に成膜を完了させ、第N層のCVD−MnOx膜7は、セルフリミットがかかるように成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線とバリア膜との密着性の低下、エレクトロマイグレーション耐性の低下、及び工程数の増加を抑制しつつ、めっき膜の膜厚がウェハ中心部とウェハ周辺部で異なることを抑制できる半導体装置の製造方法を提供する。

【解決手段】絶縁膜100に形成された溝102の側面及び底面に、添加元素を含む金属バリア膜120を形成する。次いで、金属バリア膜120上にシード膜142を形成し、さらにシード膜142をシードとしてめっき層(Cu膜144)を形成することにより、溝102内に金属膜140を埋め込む。次いで、金属バリア膜120及び金属膜140を熱処理することにより、金属バリア膜120と金属膜140の間に、金属バリア膜120を構成する金属、添加元素、及び金属膜140を構成する金属を含む合金層を形成し、かつ添加元素を金属膜140中に拡散させる工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面に対する合金膜の付着性(サイドカバレッジ)を向上させることができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18は、バイアススパッタ法により形成される。そして、そのバイアススパッタ法による合金膜18の形成時には、第2溝11およびビアホール12の内面に向けて飛散するスパッタ粒子のエネルギーにより、第2溝11およびビアホール12の底面に付着しているスパッタ粒子が弾き飛ばされ、その弾き飛ばされたスパッタ粒子が第2溝11およびビアホール12の側面に再付着(リスパッタ)するように、スパッタ粒子を加速するためのRFバイアスが設定される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、配線上面部からの金属拡散を抑制することができる、半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明では、半導体基板上の第一層間膜1内に形成された溝2内に、銅と第一金属元素とを含有する銅シード膜4を形成する。その後、銅メッキ処理を施す。その後、銅層の酸化が行われない第一雰囲気中にて第一熱処理を行う。そして、余分な銅合金金属層を除去し、溝2内に銅合金配線6を形成する。その後、酸素を含有する第二雰囲気中にて第二熱処理を行うことにより、銅合金配線6表面に、第一金属元素の酸化物である酸化物層7を形成する。

(もっと読む)

光電変換装置、撮像システム、及び光電変換装置の製造方法

【課題】光電変換部へ向けて入射した光の反射を低減するとともに、光電変換部の受光表面におけるダングリングボンドを減少させる。

【解決手段】光電変換装置は、受光表面を有する光電変換部と、前記光電変換部の上方における開口領域を規定する多層配線構造とを備え、前記多層配線構造は、前記開口領域における輪郭辺を規定する最上の配線層と、前記最上の配線層と同一のパターンを有し且つ前記受光表面に垂直な方向から見た場合に前記最上の配線層に完全に重なるように前記最上の配線層の上に配され、水素を含む水素含有層と、少なくとも前記開口領域を満たす層間絶縁膜と、前記最上の配線層、前記水素含有層、及び前記層間絶縁膜を覆うように延びており、前記水素含有層より水素の含有率が低い保護膜とを含む。

(もっと読む)

1 - 20 / 37

[ Back to top ]