Fターム[5F033QQ89]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 酸化処理 (296)

Fターム[5F033QQ89]に分類される特許

1 - 20 / 296

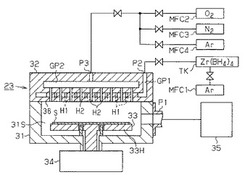

絶縁膜形成方法及び絶縁膜形成装置

【課題】信号遅延の抑制と絶縁性の向上との両立が可能な絶縁膜形成方法及び絶縁膜形成装置を提供する。

【解決手段】

シリコン貫通電極用の貫通孔が形成されたシリコン基板を備える基板Sに絶縁膜を形成するに際し、抵抗加熱ヒータ33Hによって加熱された基板Sを収容する反応室31Sに、酸素ガス及びキャリアガスであるアルゴンガスと混合されたZr(BH4)4を供給する。そして、Zr(BH4)4を上記基板S上で熱酸化することによって、基板Sの表面及び上記貫通孔の内側面にジルコニウム、ホウ素、及び酸素を含む絶縁膜の一つであるZrBO膜を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体基板、電子デバイス及びその製造方法

【課題】シリコン基板、半導体回路素子または絶縁層にクラックが発生することのない高信頼度のTSVを有する半導体基板、電子デバイス及びその製造方法を提供する。

【解決手段】貫通電極を囲む環状の溝に形成された絶縁層3は、シリカ微粒子311と、シリカ微粒子311−311間に生じる隙間に浸透してこれを埋めるナノ結晶またはナノアモルファスのシリカ320とからなるナノコンポジット構造である。

(もっと読む)

エッチング方法、エッチング装置、および記憶媒体

【課題】工程および装置構成を煩雑にすることなく、高エッチングレートで銅を異方性エッチングする装置、及びその方法を実施するプログラムを記憶した媒体を提供する。

【解決手段】チャンバ内に表面に銅膜104を有する基板101を配置し、チャンバ内を真空状態としつつ、チャンバ内に有機化合物106を供給し、銅膜に酸素ガスクラスターイオンビームを照射し、酸素ガスクラスターイオンビーム中の酸素ガスクラスターイオン107により、銅膜の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅膜を異方的にエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置の製造方法

【課題】煩雑な工程を経ることなく、マイクロスリットの発生による断線が生じ難い、銅配線を含む半導体装置の製造方法を提供すること。

【解決手段】基板上の凹部を有する層間絶縁膜上にバリア膜を介して凹部を埋めるように銅膜を形成した構造体を準備する工程と、構造体の銅膜をバリア膜との界面まで化学機械研磨により除去し、凹部内にCu配線を形成する工程と、Cu配線をエッチングしてその表面を層間絶縁膜表面よりも後退させる工程と、バリア膜を化学機械研磨により除去する工程とを有し、Cu配線の表面を層間絶縁膜表面よりも後退させる際に、構造体を真空状態の有機化合物雰囲気に配置し、構造体の銅配線表面を含む面に酸素ガスクラスターイオンビームを照射し、その中の酸素ガスクラスターイオンにより、銅配線の表面の銅を酸化させて酸化銅とするとともに、酸化銅と有機化合物を反応させて銅配線を異方的にエッチングする。

(もっと読む)

有機シリケート材料からの炭素の除去方法

【課題】有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去すること。

【解決手段】本明細書中に記載されているのは、酸化剤等の、しかし酸化剤に限られない薬品を用いてOSG膜を処理する工程、OSG膜紫外線を含むエネルギー源に曝す工程、またはOSG膜を薬品で処理する工程およびOSG膜をエネルギー源に曝す工程により、有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去するための方法である。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

成膜装置およびバリアメタル形成方法

【課題】スパッタチャンバ内を汚染することなく、バリアメタルを形成することができる成膜装置を提供すること。

【解決手段】実施形態の成膜装置は、第1のプロセスチャンバと、第2のプロセスチャンバと、第3のプロセスチャンバと、を備えている。そして、第1のプロセスチャンバは、スパッタ処理を行うことにより、基板上に第1のバリアメタルを成膜する。また、前記第2のプロセスチャンバは、前記第1のバリアメタルが成膜された前記基板上に第1のガスを導入することにより、前記第1のバリアメタルの上層部を前記第1のガスによって表面処理し、これにより前記第1のバリアメタル上に第2のバリアメタルを形成する。さらに、前記第3のプロセスチャンバは、前記第2のバリアメタルが形成された前記基板にスパッタ処理を行うことにより、前記第2のバリアメタル上に第3のバリアメタルを成膜する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

金属パターンの製造方法

【課題】簡易なプロセスでパターン欠陥を抑制することが可能な金属パターンの製造方法を提供する。

【解決手段】アルミニウムを含む金属パターン20を製造する際に、真空雰囲気下にて、気相法により、基板上にアルミニウムを含む金属膜21を成膜する工程(1)と、金属膜21の表面に酸化処理により酸化膜22を形成する工程(2)と、酸化膜22上に金属パターンに対応したレジストパターン30を形成する工程(3)と、レジストパターン30をマスクとして、金属膜21をエッチングする工程(4)とを順次実施する。工程(1)と工程(2)との間において、少なくとも工程(2)の実施直前には、基板の雰囲気を真空雰囲気とする。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

貫通電極を備えた配線基板とその製造方法

【課題】深孔相互間の距離を狭くする事ができ、深孔を微細化しても周囲の配線基板から及ぼされる応力の増加が防止でき、信頼性が保たれ、プロセス全体を低コストできる配線基板とその製造方法を提供する。

【解決手段】基体の主表面からその反対側裏面の両面に貫通する複数の貫通孔を備え、それらの孔が実質的に金属で埋められて貫通電極とされており、それらの内の少なくとも2以上の電極が電気的に並列に接続されている配線基板の製造方法であって、それらの2以上の孔を形成する場合に、それらの2以上の孔を含む領域より大きいサイズのマスクパターンを利用してそれらの2以上の孔を陽極酸化法を含む自己組織的穴明けプロセスにより所定の深さ以上の孔を形成した後に裏面から基体を削って、孔を裏面に露出させて貫通孔とする事を特徴とする配線基板の製造方法。

(もっと読む)

電力用半導体装置及びその製造方法

【課題】本発明は、信頼性の高い外部電極との接続構造を有する電力用半導体装置及びその製造方法の提供を目的とする。

【解決手段】本発明の電力用半導体装置は、段差を有する絶縁膜9と、絶縁膜9の前記段差を覆って形成された上部配線10と、上部配線10上の少なくとも前記段差の側壁に対応する部分を含む所定箇所に、部分的に形成された酸化膜16と、上部配線10及び酸化膜16上に形成され、半田21により外部導体22と接合するバリア層20とを備える。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、簡便に形成できて、チャージアップしにくいハードマスクを用いた半導体装置の製造方法を提供することを目的とする。

【解決手段】

半導体装置の製造方法であって、半導体基板上に形成された被加工膜上に、アミン化合物と水素化アルミニウムとの錯体を含有するアルミニウム膜形成用材料を塗布して、塗布膜を形成する工程と、前記塗布膜に対して、加熱処理および光照射処理から選ばれる少なくとも一種の処理を行いアルミニウム膜を形成する工程と、 該アルミニウム膜をエッチングしてハードマスクを形成する工程と、前記ハードマスクをマスクにして被加工膜をエッチングする工程を有することを特徴とする。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

1 - 20 / 296

[ Back to top ]