Fターム[5F033QQ92]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 清浄化 (1,803) | コンタクトホール部の清浄化 (522)

Fターム[5F033QQ92]に分類される特許

1 - 20 / 522

Cu層形成方法及び半導体装置の製造方法

半導体装置、半導体装置の製造方法、および電子機器

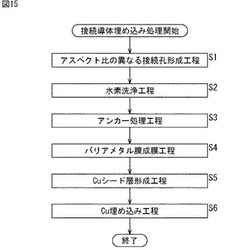

【課題】アスペクト比の異なる複数の開口下部に接続される配線に対して最適な処理を施すことができるようにする。

【解決手段】半導体装置の製造方法において、第1の半導体基板と第2の半導体基板が接合された半導体基板の第1の開口の下部配線と、貫通接続孔と異なるアスペクト比の第2の開口の下部配線に対して、バリアメタル膜の成膜と、スパッタガスによる物理エッチングを同時に行うアンカー処理工程が含まれる。本技術は、例えば、固体撮像装置などの半導体装置に適用できる。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極の形成時スループットやコスト悪化を回避する。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタのオン電流を十分に確保することが可能な信頼性の高い半導体装置を提供する。

【解決手段】活性領域6を分断する2つの埋め込みゲート用の溝部8a,8bにゲート絶縁膜9を介して埋め込まれたゲート電極7a,7bと、ビットコンタクト用の溝部12を挟んで対向する一対の埋め込みゲート用の溝部8a,8bの底部に不純物が拡散された領域13a,13bと、ビットコンタクト用の溝部12に不純物が拡散された領域13cと、が結合されて設けられた第1の不純物拡散層13と、中央部を挟んだ両側に位置する活性領域6a,6cに、ゲート電極7a,7bの上面と同程度の深さで不純物を拡散させることによって形成された第2の不純物拡散層14a,14bとを備える。

(もっと読む)

半導体装置の製造方法

【課題】穴部の側壁を基板の表面に対して垂直に形成するとともに、高速にシリコン層をエッチングするプラズマエッチング方法を提供する。

【解決手段】レジスト層をマスクとしてシリコン層をプラズマエッチングする方法であって、前記プラズマエッチング工程が、所定の比率で混合した堆積性ガスおよびエッチング性ガスの混合ガスを処理容器内に導入し、該混合ガス雰囲気で前記被処理基板をプラズマエッチングする第1のエッチングステップと、前記処理容器内に前記堆積性ガスを導入し、前記第1のエッチングステップによりプラズマエッチングされた被処理基板を該堆積性ガスが主体の雰囲気で堆積処理する堆積ステップ、および、前記処理容器内に前記エッチング性ガスを導入し、前記堆積ステップにより堆積処理された被処理基板を該エッチング性ガスが主体の雰囲気でプラズマエッチングする第2のエッチングステップを、複数回繰り返す。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極と配線との接続部位の抵抗のバラつきを低減させて、配線信頼性を向上させる。

【解決手段】貫通電極用の穴部を設け、配線層に対してオーバエッチングを施す。穴部に銅を埋め込むことにより、銅からなる貫通電極を形成させて、アルミニウムからなる配線と接続させた後、熱処理により貫通電極と配線とが接続される接触領域Gを合金化させることで、貫通電極と配線との抵抗バラつきを低減させて、配線信頼性を向上させる。本技術は、半導体装置と、その製造に適用することができる。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】実施形態は、一括して形成することが可能なメモリセルを有し、その直下に制御回路を設けた構成を実現する半導体装置およびその製造方法を提供する。

【解決手段】実施形態は、基板上に設けられたメモリアレイと、前記基板と前記メモリアレイとの間の前記基板の表面に設けられた制御回路と、を有する半導体装置の製造方法であって、前記制御回路のp形半導体領域およびn形半導体領域を覆う絶縁層に、前記p形半導体領域に連通する第1のコンタクトホールを形成する工程と、前記第1のコンタクトホールの内部に、前記p形半導体領域に接したコンタクトプラグを形成する工程と、を備える。さらに、前記n形半導体領域に連通する第2のコンタクトホールを前記絶縁層に形成する工程と、前記コンタクトプラグと、前記第2のコンタクトホールの内部に露出した前記n形半導体領域と、に接する配線を形成する工程と、を備える。

(もっと読む)

半導体ドライプロセス後の残渣除去液及びそれを用いた残渣除去方法

【課題】本発明は、Cu及びlow-k膜にダメージを与えずに、従来のポリマー剥離液で解決し得なかったわずかな亀裂状のCu腐食の抑制が可能なドライプロセス後の残渣除去液を提供し、これを用いた半導体デバイスの製造方法を確立する。

【解決手段】ドライエッチング及び/又はアッシング後の半導体基板に存在する残渣の除去液であって、フッ素化合物を含まず、銅に配位し得る2以上の酸素原子を有する中性有機化合物及び/又はC4以上のモノアルコールのうち少なくとも1種と、水とを含むことを特徴とする残渣除去液、或いは、過塩素酸塩と水とを含むことを特徴とする残渣除去液に関する。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置の製造方法

【課題】SiCOH膜からなる層間絶縁膜に形成された埋め込み用の凹部に銅材を埋め込んで導電路を形成するにあたり、導電路の抵抗を低くすること。

【解決手段】SiCOH膜にプラズマにより凹部を形成すると表面が疎水性になる。このSiCOH膜に水素ガスのリモートプラズマを供給し、Hラジカル及びHイオンにより凹部の表面を親水性に改質する。またプラズマに代えて過酸化水素水を供給してもよく、この場合表面にOH基が形成される。次いで例えばRu3(CO)12ガスとCOガスとを用いてCVDによりRu膜4を成膜し、その後銅材5を埋め込み、CMP処理をして上層側の配線構造を形成する。また改質にあたって、グリム、DMEDAなどを用いてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保する。

【解決手段】半導体装置100は、半導体基板と、半導体基板上に設けられた層間絶縁膜50と、層間絶縁膜50に埋め込まれた、Cuにより構成される配線10と、配線10の表層に設けられた、銅錯体を含有する表面層20と、を備える。配線10の表層に銅錯体を含有する表面層20を備えることにより、配線抵抗の上昇や絶縁耐性の劣化を抑制しつつ、配線信頼性を確保することができる。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置、電子機器、及び、半導体装置の製造方法

【課題】 より信頼性の高い接合界面を有する半導体装置を提供する。

【解決手段】 半導体装置1を、接合界面Sj側の表面に形成された第1金属膜16を有する第1半導体部10と、接合界面Sjで第1金属膜16と接合された第2金属膜26を有する第2半導体部20と、界面バリア部28とを備える構成とする。第2金属膜26の接合界面Sj側の表面面積は第1金属膜16の接合界面Sj側の表面面積より小さくする。そして、第1金属膜16の接合界面Sj側の面領域のうち第2金属膜26と接合しない面領域を含む領域に界面バリア部28を設ける。

(もっと読む)

1 - 20 / 522

[ Back to top ]