Fターム[5F033RR04]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化物 (6,040) | SiO2 (5,243)

Fターム[5F033RR04]に分類される特許

2,001 - 2,020 / 5,243

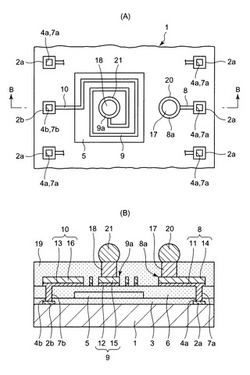

半導体装置およびその製造方法

【課題】 渦巻き形状の薄膜誘導素子を備えたCSPと呼ばれる半導体装置において、シリコン基板に発生する渦電流に起因する薄膜誘導素子の渦電流損を低減する。

【解決手段】 シリコン基板1と薄膜誘導素子9との間には低誘電率膜5が設けられている。これにより、シリコン基板1に発生する渦電流に起因する薄膜誘導素子9の渦電流損を低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁膜に設けたホールパターンに形成された導電体膜の断線を防止できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、第1の導電体膜上に絶縁膜を形成し、絶縁膜を露出する開口部を有するマスク膜を用いた異方性エッチングにより、開口部に露出した絶縁膜の上部に凹部を形成すると共に、マスク膜の側壁部下部に反応生成物を付着させる。次に、等方性エッチングにより、マスク膜の側壁部を水平方向に後退させると共に、異方性エッチングにより、凹部の底部に露出した絶縁膜を垂直方向に掘り下げながら、マスク膜の側壁部下部に付着した反応生成物を除去する。次に、異方性エッチングにより、凹部の周囲に存在する絶縁膜を鉛直方向に掘り下げて段差部を形成すると共に、凹部の底部を貫通させて第1の導電体膜を露出させる。その後、第1の導電体膜の上に第2の導電体膜を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体の製造工程において、層間絶縁膜へのダメージを極力抑えることが可能な配線の還元処理方法の開発。

【解決手段】本発明は、基板上に導電部材および絶縁膜を有する半導体装置の製造方法であって、該方法は、基板上に導電部材を形成する工程、該導電部材上に絶縁膜を形成する工程、該導電部材上の絶縁膜を除去する工程、該導電部材上の酸化された領域を還元するために有機シランガスおよび水素ガスをブローする工程からなり、ここで該導電部材上の酸化された領域は、該絶縁膜が除去されたときに形成されることを特徴とする。

(もっと読む)

半導体基板の電解めっき方法および電解めっき装置

【課題】貫通孔を有するシリコンウエハの貫通孔にオーバーハング形状や内部ボイドがなくめっきを充填する方法を提供すること。

【解決手段】シリコンウエハ内の貫通孔開口部と同位置に開口部を有するプレートを一定の距離をおいてシリコンウエハの貫通孔開口部にプレート開口部を合わせて、めっき電極側に向けて配置してめっきを行う。プレート開口径は貫通孔開口径より少し小さくする。プレート開口径と貫通孔開口径Rの差を2xとしたとき、x/Rを0.1〜0.3、シリコンウエハとプレートの距離を0.05mm〜1.0mmとしたときに、前記課題を実現できる。プレートは、多孔質セラミックのような絶縁体でかつ多孔質材料が望ましく、シリコンウエハ表面のめっき成長も抑制できる。

(もっと読む)

半導体装置

【課題】ダイシング時に半導体チップの側壁からのクラックが侵入するのを抑制することで信頼性向上を図る。

【解決手段】半導体チップ領域10の表面の端部上に、集積回路領域31を取り囲んでクラックストッパ用シールリング30が形成されている。クラックストッパ用シールリング30は、集積回路領域31の外の半導体基板11上に形成された積層構造体であり、第1ダミー金属層20、第2ダミー金属層21、第3ダミー金属層22が、それぞれ、第1層間絶縁膜12、第2層間絶縁膜14、第3層間絶縁膜16を間に挟んで積層されている。第1ダミー金属層20、第2ダミー金属層21、第3ダミー金属層22は、集積回路領域31の半導体素子や配線とは第1乃至第3の層間絶縁膜12,14,16によって電気的に絶縁されている。

(もっと読む)

半導体装置

【課題】多層の金属配線層を有する半導体装置において、より一層のパッド配置面積の低減を図る。

【解決手段】アルミ3と、アルミ3との間に層間絶縁膜を介して設けられたアルミ2と、アルミ2,3間を接続するコンタクトと、アルミ3に対応して設けられた保護膜の開口部1と、を備え、開口部1の内側領域が、外部電極用パッドであり、かつ、ボンディング領域とプローブテスト領域の二つに分けて使用される半導体装置である。前記ボンディング領域では、アルミ3が露出され、該アルミ3によりアルミ2が隠れている。前記プローブテスト領域では、アルミ2が露出されている。

(もっと読む)

配線用セルフアライン(自己整合)バリア層

集積回路中の銅線を完全に取り囲んでいるケイ酸マンガン層及び窒化ケイ素マンガン層を組み込んだ集積回路用の配線構造、及びその製造方法を提供する。ケイ酸マンガンは、銅が配線から拡散しないためのバリアを形成し、それにより、絶縁体が磁気尚早に損しないよう保護し、トランジスタが銅により劣化しないように保護する。また、ケイ酸マンガン及び窒化ケイ素マンガンは、銅と絶縁体の間の強い接着を促進し、これゆえに製造及び使用の間のデバイスの機械的な完全性が保持される。また、銅−ケイ酸マンガン界面及び窒化ケイ素マンガン界面における強い接着は、デバイスの使用の間の銅のエレクトロマイグレーションによる損傷から保護する。また、マンガン含有シースは、銅がその周囲の酸素又は水により腐食しないよう保護する。 (もっと読む)

半導体装置の製造方法

【課題】膜厚の異なる半導体層上においても、良好にゲート電極を形成可能な半導体装置の製造方法を提供する。

【解決手段】絶縁体2上の膜厚の異なる半導体層3a,3bにそれぞれ形成された電界効果型トランジスタを有する半導体装置の製造方法である。まず、膜厚の異なる半導体層3a,3bを絶縁体上に形成する。そして、半導体層3a,3b上にゲート絶縁膜5a,5bを形成し、ゲート絶縁膜5a,5b上にゲート電極材料を積層する。パターニング時におけるフォトリソグラフィに影響を与えない膜厚を有する犠牲膜をゲート電極材料上に形成し、エッチングにより犠牲膜をパターニングするとともに、パターニングされた犠牲膜8aをマスクに用いてゲート電極材料をパターニングしてゲート電極11,12を形成する。

(もっと読む)

洗浄剤組成物及び半導体基板の製造方法

【課題】従来の洗浄剤組成物は、枚葉処理装置に用いるには除去能力は必ずしも十分ではない。HSQ、MSQ等のシロキサン膜からなる低誘電率膜のドライエッチングにおいてはHSQ、MSQのエッチング表面に変質層が生成されるが、従来の洗浄剤組成物は、この変質層に対するエッチング速度が極めて速く、このため、この組成物を用いたドライエッチングの後処理洗浄においては意図するエッチング寸法よりも実際のエッチング寸法が拡大してしまう問題がある。

【解決手段】半導体回路の製造工程においてドライエッチング後及び/又はアッシング後の半導体基板からフォトレジスト残渣及び/又はポリマー残渣を除去する洗浄剤組成物であって、残渣除去成分(A)、半導体基板の配線材料に用いる金属の腐食防止成分(B)、半導体基板の層間絶縁膜材料の保護成分(C)及び水を含有し、(A)、(B)及び(C)が下記化合物であることを特徴とする洗浄剤組成物。

(もっと読む)

半導体装置およびその製造方法

【課題】微細なコンタクト構造であっても、低コンタクト抵抗のコンタクト構造を形成することができる半導体装置およびその製造方法を提供する。

【解決手段】シリコン基板11の表面部に形成された不純物領域15と、不純物領域15の表面から所定深さにわたって形成された金属シリサイド層16とを備える。シリコン基板11上には層間絶縁膜18が形成され、層間絶縁膜18を貫通して底部が金属シリサイド層16に到達するコンタクトホール19が形成されている。コンタクトホール19は、金属シリサイド層16からなる側壁の面積が、金属シリサイド層16からなる底面の面積よりも大きい開口部になっている。さらに、コンタクトホール19の、金属シリサイド層16からなる側壁および底面に接触するコンタクトプラグ21がコンタクトホール19に埋め込まれている。

(もっと読む)

集積回路及びその製造方法

【課題】配線層の上に層間絶縁膜を堆積した集積回路において熱処理を施すと、配線間の狭い間隙部と、これにつながる広い開口部との接続部分にて、層間絶縁膜の破裂が起こり得る。

【解決手段】間隙部10と開口部12との接続部分に位置する配線4bの角部を面取りして、間隙部10の端部62を開口部12へ向けて末広がり形状とする。このようにパターニングした配線層の上に層間絶縁膜を堆積する。層間絶縁膜は間隙部10の狭い溝に起因して当該位置に空洞を形成し得る。端部62を設けることで、層間絶縁膜の堆積に関して、間隙部10と開口部12との接続部分での不連続性が緩和され、間隙部10の空洞の端が層間絶縁膜によって封止されにくくなり、熱処理での空洞の気圧上昇に伴う層間絶縁膜の破裂が抑制される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】二次配線と半導体チップの電子回路部とが重なり合う場合においても、当該二次配線と当該電子回路部との間の電磁界的干渉を抑制することができると共に、ウエハの彎曲を抑えることができ、かつ、ダイシング工程において、チッピングが発生する危険性を低減することができる半導体装置を提供する。

【解決手段】半導体装置1aは、半導体チップ2において、第1の二次配線未形成領域の絶縁層が、第1の二次配線形成領域の絶縁層よりも薄く形成される。また、半導体チップ2における、電極パッド10が形成された回路形成面が伸びている方向に関し、半導体チップの縁31が、上層絶縁層12の縁である側壁部12sよりも突出している。

(もっと読む)

三次元構造体の製造方法および三次元構造体

【課題】導電体内の欠陥の発生を抑制し、導電体が連続的に形成される三次元構造体の製造方法および三次元構造体を提供する。

【解決手段】第1の導電体上に、絶縁体と、この絶縁体内に、第1の導電体と異なる第2の導電体で構成される縦構造体と横構造体が組み合わされた三次元の擬似導電体構造とを形成する工程と、擬似導電体構造を溶解除去して三次元の空洞を形成し、第1の導電体を露出させる工程と、第1の導電体をシード層として、電解めっき法により第3の導電体を空洞に充填し、三次元の導電体構造を形成する工程を有することを特徴とする三次元構造体の製造方法およびこれによる三次元構造体。

(もっと読む)

半導体装置およびその製造方法

【課題】SOIウエハを用いずに、誘電体分離構造を有する安価な半導体装置を得ること。

【解決手段】複数の半導体素子が形成された半導体ウエハ(半導体基板12)のおもて面に表面電極17、再配線19およびポスト21を形成し、おもて側封止樹脂20で封止する。ウエハの裏面を研磨してウエハを薄くする。研磨により露出する面からウエハを貫通しておもて面の層間絶縁膜16に達する分離溝を形成する。ウエハの裏面に絶縁膜を積層して、分離溝を分離絶縁膜15で埋めるとともに、研磨による露出面を裏面絶縁膜14で被覆することによって、誘電体分離構造を形成する。ウエハを複数のチップに分割する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】信頼性を低下することなく高集積化が可能な半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】半導体装置は、コンタクト層40及びAl層の真上にAl層を積層したAlスタック構造をなすものであり、コンタクト層40の真上に1stAl層10が積層され、1stAl層10の真上に2ndAl層20が積層され、2ndAl層20の真上に3rdAl層30が積層されてなるものである。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜が剥離しにくいようにする。

【解決手段】 シリコン基板1の上面の周辺部を除く領域には低誘電率膜4と配線5との積層構造からなる低誘電率膜配線積層構造部3が設けられている。低誘電率膜配線積層構造部3の上面には第1のパッシベーション膜7が設けられている。そして、第1のパッシベーション膜7および低誘電率膜配線積層構造部3の側面は第2のパッシベーション膜9によって覆われている。これにより、低誘電率膜4が剥離しにくい構造となっている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、電気的接続について信頼性を向上させることを目的とする。

【解決手段】集積回路12及び集積回路12に電気的に接続された電極14を有する半導体基板10に、熱硬化性樹脂前駆体24を設ける。電極14上から、熱硬化性樹脂前駆体24の表面に至るように、配線20を形成する。熱硬化性樹脂前駆体24を、熱によって硬化収縮させて表面積を小さくし、配線20に凸部22となるしわを形成する。

(もっと読む)

半導体装置

【課題】従来の半導体装置に比べてさらなる小型化を可能とする、複数の半導体素子が並列に接続された半導体装置を提供する。

【解決手段】半導体装置1は、ソース領域15と、ドレイン領域17と、ゲート領域16とを有するJFET10を複数個備えている。複数個のJFET10は、ソース領域15同士を接続するソース電極25と、ドレイン領域17同士を接続するドレイン電極27と、ゲート領域16同士を接続するゲート電極26とにより並列に接続されている。ソース電極25は、ソース電極25を外部と接続するソース電極パッド25Aを含んでいる。ドレイン電極27は、ドレイン電極27を外部と接続するドレイン電極パッド27Aを含んでいる。そして、ソース電極パッド25Aおよびドレイン電極パッド27Aは、絶縁体からなる絶縁保護膜28を挟んでゲート電極26の上側に突出するように形成されている。

(もっと読む)

ナノプリント用スタンパ、及び微細構造転写方法

【課題】ナノプリント法において、基板からスタンパを剥離する工程を高精度かつ容易に行うことを目的とする。

【解決手段】プレス装置を用い、基板上に微細構造を形成するためのスタンパにおいて、前記スタンパが剥離機構を有することを特徴とするナノプリント用スタンパ、及び該スタンパを用いるパターン転写方法。

(もっと読む)

膜特性を求める方法

【課題】配線形成過程に起きる膜物性値変化を、再現性と簡便性とを両立して追跡できる技術を提供することである。

【解決手段】基板上に膜が順に複数積層されてなる複合膜における任意の膜Ckの比誘電率を求める方法であって、前記基板上に前記複合膜を設ける複合膜成膜工程と、前記基板上に前記任意の膜Ck以外の膜を一つずつ設ける単一膜成膜工程と、前記複合膜成膜工程で得た複合膜の比誘電率k(複合膜)を求める工程と、前記単一膜成膜工程で得た膜Ck以外の単一膜の比誘電率k(単一膜)を各々求める工程と、前記複合膜成膜工程で得た複合膜の厚さd(複合膜)を求める工程と、前記複合膜成膜工程で得た複合膜における各々の膜の厚さd(単一膜)を求める工程とを具備する。

(もっと読む)

2,001 - 2,020 / 5,243

[ Back to top ]