Fターム[5F033RR09]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 無機SOG膜(無機物質又は不明な場合) (711)

Fターム[5F033RR09]に分類される特許

1 - 20 / 711

半導体記憶装置及びその製造方法

【課題】エッチングに対して耐性を持つ保護膜が設けられた記憶素子を有する半導体記憶装置を提供する。

【解決手段】実施形態にかかる半導体記憶装置は、半導体基板の上面に形成された複数の記憶素子と、隣り合う各記憶素子の間に埋め込まれた層間絶縁膜と、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、各記憶素子の側面において膜厚が10nm以下である保護膜と、層間絶縁膜中に形成されたコンタクトとを有し、保護膜は、各記憶素子の側面と、隣り合う各記憶素子の間の半導体基板の上面との上に連続的に形成され、且つ、酸化シリコン膜、窒化シリコン膜、又は、酸窒化シリコン膜からなる第1の保護膜と、第1の保護膜上に連続的に形成され、且つ、ボロン膜又は窒化ボロン膜からなる第2の保護膜とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

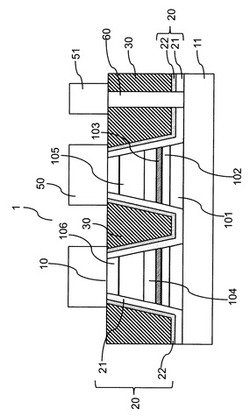

積層半導体基板、半導体基板および積層チップパッケージ並びにこれらの製造方法

【課題】単位時間あたりに製造できる積層チップパッケージの個数を増やして積層チップパッケージの製造コストを低減する。

【解決手段】積層半導体基板100は、複数の半導体基板1が積層されている。各半導体基板1はスクライブラインに沿った複数のスクライブ溝部20,21が形成されている。また、各半導体基板1は半導体装置が形成され、それぞれ絶縁されている複数のデバイス領域10と、複数のデバイス領域10のそれぞれに形成されている半導体装置に接続され、かつデバイス領域10からスクライブ溝部20,21の内側に延出している複数の配線電極15とを有している。複数の配線電極15は部分配置パターンで配置され、スクライブ溝部20,21を挟んで隣り合う2つのデバイス領域10のうちのいずれか一方だけから延出している。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホールの側壁に制御性良く傾斜を形成することで、コンタクトプラグにボイドが形成されることを抑制する。

【解決手段】絶縁膜10に第1のコンタクトホール(破線部)を形成する工程と、第1のコンタクトホールの内壁を構成する絶縁膜の上方ほどエッチング量が多くなるケミカルドライエッチングを施して内壁が傾斜した第2のコンタクトホール13を形成する工程と、第2のコンタクトホール内にコンタクトプラグを形成する工程とを有する。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】実効的な低配線間容量を維持しつつ、高密着性かつ高い配線間絶縁信頼性を有する多層配線技術を提供する。

【解決手段】第一の絶縁膜は、シリコン、酸素及び炭素を含むシロキサン構造を含む少なくとも1層以上の絶縁膜であり、第一の絶縁膜内部のシロキサン構造は炭素原子数がシリコン原子数よりも多く、第一の絶縁膜と金属との界面及び第一の絶縁膜と第二の絶縁膜との界面のうち少なくとも何れか一方に、第一の絶縁膜内部よりも単位体積当たりの炭素原子数が少なく、且つ酸素原子数が多い改質層が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置

【課題】多層配線プロセスでSOGエッチバックにて平坦化を行なうプロセスにて、ヒューズ開口部に起因する水分の浸入における長期信頼性の劣化を防止する半導体装置の製造方法を提供する。

【解決手段】ヒューズ開口部からの水分侵入を防ぐためのメタル1層目のガードリングの下部まで多結晶シリコンが伸びているヒューズ形状にする。これによりヒューズの電極をとるためのメタル配線とガードリングのメタル配線の高さがそろい、SOG層がIC内部に到達することを防ぐことが可能となる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】クラックの発生を抑制できるとともに、SOG膜の剥離を抑えることが可能な半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体素子が形成された半導体基板3上に、SOG膜を含む層間絶縁膜10が形成されており、この層間絶縁膜10を介して、配線層12a〜12dが半導体素子と電気的に接続されている。さらに、一方面側がボンディング接続されるパッド部12d(第4配線層12d)と、層間絶縁膜10に配置されると共に配線層12a〜12cを接続するビアホール15a〜15cと、ビアホール15a〜15c内に埋め込まれる導電層16a、16bとを有している。そして、ビアホール15a〜15cは、パッド部12dよりも下方に設けられており、導電層16a、16bの少なくとも一部は、内部に空洞部17を有している。

(もっと読む)

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

プラズマエッチング方法及び半導体装置の製造方法

【課題】トレンチ・ビア形状のウエハ面内均一性を向上できるプラズマエッチング方法を提供する。

【解決手段】基板上の第1配線層の上に絶縁層と金属層とを形成するステップと、絶縁層内に形成される第2配線層のためのトレンチを画成する金属マスク層を金属層から形成するステップと、金属マスク層を覆う平坦化膜を形成するステップと、トレンチの底部に形成され第1及び第2配線層を接続するビアを画成するマスク層を平坦化膜から形成するステップと、マスク層で、絶縁層の厚さよりも小さい開口を形成する第1ステップと、金属マスク層で絶縁層をエッチングしてトレンチを形成し、開口を深くしてビアを形成する第2ステップとが行われる。第1及び第2ステップでは、供給されたエッチングガスの拡散の影響が支配的な位置と、供給されたエッチングガスの流れの影響が支配的な位置とに対応してエッチングガス供給条件が調整される。

(もっと読む)

半導体装置およびその製造方法

【課題】 実施形態は、層間配線抵抗が低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、基板と、前記基板上に第1の触媒金属膜と、前記第1の触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと、前記コンタクトホール底部に前記グラフェンと電気的に導通する導電膜と、導電膜上に水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した第2の触媒金属膜と、前記第2の触媒金属膜上にカーボンナノチューブとを備えることを特徴とする。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

半導体ドライプロセス後の残渣除去液及びそれを用いた残渣除去方法

【課題】本発明は、Cu及びlow-k膜にダメージを与えずに、従来のポリマー剥離液で解決し得なかったわずかな亀裂状のCu腐食の抑制が可能なドライプロセス後の残渣除去液を提供し、これを用いた半導体デバイスの製造方法を確立する。

【解決手段】ドライエッチング及び/又はアッシング後の半導体基板に存在する残渣の除去液であって、フッ素化合物を含まず、銅に配位し得る2以上の酸素原子を有する中性有機化合物及び/又はC4以上のモノアルコールのうち少なくとも1種と、水とを含むことを特徴とする残渣除去液、或いは、過塩素酸塩と水とを含むことを特徴とする残渣除去液に関する。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

エッチング液組成物およびエッチング方法

【課題】金属膜の防食性が良好であり、エッチングレートおよび選択比が高く、効率的にエッチングを行うことができるエッチング液組成物を提供する。

【解決手段】被処理基板上に形成されたシリコンを含む膜のエッチングを行う際に用いられるエッチング液組成物であって、エッチング液組成物は、含ヒドロキシ基有機化合物、含カルボニル基有機化合物、無機酸、および無機酸塩からなる群から選択される少なくとも一つと、フッ化水素酸と、フッ化アンモニウムと、有機酸とを含む。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、小型化を図ることが可能になると共に、絶縁リングで囲まれた貫通電極を狭ピッチで配置することの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】回路素子層5が形成される表面1a、及び裏面1bを有する半導体基板1と、半導体基板1を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が広くなる貫通電極7と、貫通電極7を囲むように半導体基板を貫通し、かつ半導体基板1の表面1a側から半導体基板1の裏面1b側に向かうにつれて幅が狭くなる第1の絶縁リング3と、を有し、半導体基板1の厚さ方向Aにおいて、第1の絶縁リング3の少なくとも一部と対向するように貫通電極7を配置する。

(もっと読む)

1 - 20 / 711

[ Back to top ]