Fターム[5F033RR11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | ハロゲンを含むもの(SiOFを含む) (665)

Fターム[5F033RR11]に分類される特許

1 - 20 / 665

銅を含む電極連結構造体

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

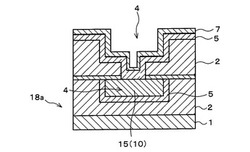

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

プラズマエッチング方法及び半導体装置の製造方法

【課題】トレンチ・ビア形状のウエハ面内均一性を向上できるプラズマエッチング方法を提供する。

【解決手段】基板上の第1配線層の上に絶縁層と金属層とを形成するステップと、絶縁層内に形成される第2配線層のためのトレンチを画成する金属マスク層を金属層から形成するステップと、金属マスク層を覆う平坦化膜を形成するステップと、トレンチの底部に形成され第1及び第2配線層を接続するビアを画成するマスク層を平坦化膜から形成するステップと、マスク層で、絶縁層の厚さよりも小さい開口を形成する第1ステップと、金属マスク層で絶縁層をエッチングしてトレンチを形成し、開口を深くしてビアを形成する第2ステップとが行われる。第1及び第2ステップでは、供給されたエッチングガスの拡散の影響が支配的な位置と、供給されたエッチングガスの流れの影響が支配的な位置とに対応してエッチングガス供給条件が調整される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の反りを抑制し、且つ、その反りの経時変化を抑制する。

【解決手段】半導体装置は、基板と、基板上に形成された多層配線層と、を有し、多層配線層は、配線と、配線を覆う層間絶縁膜と、をそれぞれ有する複数層の配線層を有する。少なくとも何れか1つの層間絶縁膜(例えば、層間絶縁膜27、30)は、第1絶縁膜41と第2絶縁膜42とを有する。第1絶縁膜41は、基板を第1方向(例えば下に凸)に反らせる応力を基板に与える。第2絶縁膜42は、第1絶縁膜41よりも表層側に形成され、第1絶縁膜41よりも吸湿性が低く、基板を第1方向に対する反対方向(例えば上に凸)に反らせる応力を基板に与える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体ドライプロセス後の残渣除去液及びそれを用いた残渣除去方法

【課題】本発明は、Cu及びlow-k膜にダメージを与えずに、従来のポリマー剥離液で解決し得なかったわずかな亀裂状のCu腐食の抑制が可能なドライプロセス後の残渣除去液を提供し、これを用いた半導体デバイスの製造方法を確立する。

【解決手段】ドライエッチング及び/又はアッシング後の半導体基板に存在する残渣の除去液であって、フッ素化合物を含まず、銅に配位し得る2以上の酸素原子を有する中性有機化合物及び/又はC4以上のモノアルコールのうち少なくとも1種と、水とを含むことを特徴とする残渣除去液、或いは、過塩素酸塩と水とを含むことを特徴とする残渣除去液に関する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ダマシン構造のCu配線を有する半導体装置の製造において熱処理工程が行われた場合の、層間絶縁膜であるCF膜からのフッ素の拡散を防止し、リーク電流の増加を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置であって、フッ素添加カーボン膜からなる層間絶縁膜と、前記層間絶縁膜に埋め込まれた銅配線と、を備え、前記層間絶縁膜と前記銅配線との間には、前記銅配線に近接するバリアメタル層と、前記層間絶縁膜に近接するフッ素バリア膜が形成されている、半導体装置が提供される。

(もっと読む)

半導体集積回路装置

【課題】銅埋め込み配線を主要な配線層とする半導体集積回路装置に於いても、通常、ワイヤボンディング特性を確保するために、最上層配線層をアルミニウム系パッド層とすることが多い。このアルミニウム系パッド層は、一般に、配線層(電源配線、信号配線等の一般相互接続配線)としても使用されている。しかし、このような一般相互接続配線は、配線長が比較的長いためアンテナ効果により、プラズマ処理時にデバイスにダメージが入り易い等のデメリットがある。

【解決手段】本願発明は、メタル多層配線系が、下層の埋め込み型多層配線層と上層の非埋め込み型アルミニウム系パッドメタル層を有する半導体集積回路装置に於いて、前記非埋め込み型アルミニウム系パッドメタル層は、実質的に電源リング配線を有しないものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子埋設用凹部上端部の肩落ちによるキャパシタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】半導体装置は、保護層80は、凹部(孔23)の上端部の周囲に設けられている。この保護層80は、保護層80と同一層に位置しており、論理回路領域に位置している多層配線層を構成する絶縁層よりも誘電率が高い材料で構成されており、機械強度に優れた部材となる。これにより、凹部(孔23)上端部の肩落ちを抑制し、キャパシタ高さのバラツキを抑制する。

(もっと読む)

半導体装置、半導体パッケージ、半導体装置の製造方法及び半導体パッケージの製造方法

【課題】電気的接続信頼性を向上させることができる半導体装置を提供する。

【解決手段】半導体チップ3は、第1主面30Aと第2主面30Bとの間を貫通する貫通孔30Xを有する半導体基板30と、半導体基板30の第2主面30Bを覆うように形成され、貫通孔30Xと対向する位置に開口部31Xが形成された絶縁層31と、絶縁膜33によって覆われた貫通孔30X及び開口部31Xに形成された貫通電極32とを有する。絶縁層31から露出される貫通電極32の上端面は、当該半導体チップ3に他の半導体チップ4が積層される際のパッドになる。また、貫通電極32の上端面は、絶縁層31の半導体基板30と接する面と反対側の面と面一になるように形成されている。

(もっと読む)

銅膜作製方法

【課題】下地層との密着性に優れた銅膜を製造する方法の提供。

【解決手段】成膜対象物上に下地層としてチタン膜を形成した後、この下地層を水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理し、次いでその上に銅膜を作製する。このように銅膜を作製した後、さらに水素ガス雰囲気中で100℃以上200℃未満の温度で熱処理を行う。

(もっと読む)

半導体装置

【課題】フリップチップ実装に用いられる半導体チップと実装基板との電気的な接続信頼性を向上させた半導体装置を提供する。

【解決手段】半導体チップ2と、半導体チップ2の主面に配置された複数の電極パッドと、複数の電極パッドの上に配置された複数のバンプ5とを有し、半導体チップ2のコーナー部において、第1のバンプと第2のバンプとが、第1のピッチで、隣接して配置され、半導体チップの中心部において、第3のバンプと第4のバンプとが、第2のピッチで、隣接して配置され、第1のピッチは、第2のピッチよりも狭い。

(もっと読む)

半導体装置、半導体装置の製造方法、及び、電子機器

【課題】基板を貼り合わせて電極接合を行う半導体素子において、電極の腐食を防ぐ半導体装置の製造方法を提供する。

【解決手段】第1接合部40と第2接合部60とが電極形成面を対向させて接合された半導体装置において、第1接合部40の絶縁層51と、絶縁層51の表面に形成された接合電極41と、絶縁層51表面に形成され、絶縁層51を介して接合電極41の周囲を囲む保護層44とを備える。さらに第2接合部60の絶縁層71と、絶縁層71の表面に形成された接合電極61と、絶縁層71表面に形成され、絶縁層71を介して接合電極61の周囲を囲む保護層64とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器

【課題】装置の信頼性や、製品の歩留まりなどを向上させる。

【解決手段】第1の開口と第2の開口との内部に金属材料を埋め込んで第1プラグと第2プラグとを設けると共に、第1プラグと第2プラグとの間を接続する接続配線を設けることで、接続導電層を形成する。そして、接続導電層において接続配線の上面を被覆するようにパッシベーション膜を形成する。このパッシベーション膜の形成工程では、高密度プラズマCVD法などのように埋め込み性に優れた成膜法で、SiO2などの絶縁膜を成膜することによって、パッシベーション膜を形成する。

(もっと読む)

アルミニウム体を備えた基体の製造方法

【課題】基体上に成膜特性(反射率、及び密着性)に優れた膜状のアルミニウム体を形成することができるアルミニウム体を備えた基体の製造方法を提供する。

【解決手段】基体をプラズマ処理するプラズマ処理工程と、プラズマ処理された基体上に、アミン化合物と水素化アルミニウムとの錯体及び有機溶媒を含有するアルミニウム体形成用組成物を塗布して、上記基体上に上記組成物からなる塗布層を形成させる塗布工程と、上記塗布層に加熱および光照射の少なくともいずれか一方を行うことにより、膜状のアルミニウム体を形成させるアルミニウム膜形成工程と、を含むアルミニウム体を備えた基体の製造方法。

(もっと読む)

1 - 20 / 665

[ Back to top ]