Fターム[5F033RR12]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419)

Fターム[5F033RR12]の下位に属するFターム

Fターム[5F033RR12]に分類される特許

1 - 20 / 141

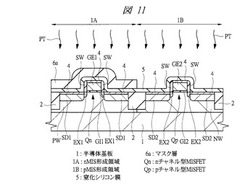

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】メモリ・ロジック混載型の半導体装置の高性能化を可能にする技術を提供する。

【解決手段】ストッパ膜17は、ストッパ膜13及び層間絶縁膜14から成る絶縁層上に形成されている。コンタクトプラグ16,65,66のそれぞれは、その上面がストッパ膜17から露出するように、ソース・ドレイン領域9,59とそれぞれ電気的に接続されてストッパ膜13、層間絶縁膜14及びストッパ膜17に設けられている。絶縁層20は、ストッパ膜17及びコンタクトプラグ16,65,66の上に設けられている。キャパシタ82の下部電極は、メモリ形成領域において、コンタクトプラグ66の上面とストッパ膜17の上面とに接触するように絶縁層20内に設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板の転移を防止しつつ、絶縁膜の埋め込み性を確保するとともに、エッチング耐性を向上させる。

【解決手段】シリコン含有無機ポリマー膜8にアルカリ金属元素またはアルカリ土類金属元素を含有させ、塗布法などの方法にてトレンチ6内に埋め込まれるようにしてシリコン含有無機ポリマー膜8をライナー膜7上に形成し、水蒸気を含む雰囲気中でシリコン含有無機ポリマー膜8の酸化処理を行うことにより、シリコン含有無機ポリマー膜8をシリコン酸化膜9に変化させる。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

絶縁膜形成方法、及び絶縁膜形成装置

【課題】成膜温度が180℃以下で形成される絶縁膜の絶縁性を高めることの可能な絶縁膜の形成方法及び該絶縁膜を形成する成膜装置を提供する。

【解決手段】

マスフローコントローラMFC1から原料タンクTKにArガスを供給することによって押し出されたZr(BH4)4ガスと、マイクロ波プラズマ源PLで励起することによって活性状態にされた酸素原子を含むガスとを、シャワープレート36に設けられた複数の孔から別々に基板S表面の空間に供給する。この際、活性状態にされた酸素原子を含むガスの供給を連続的に行う間に、Zr(BH4)4昇華ガスの供給を間欠的に複数回行ってもよい。これにより、ジルコニウムと、ホウ素と、酸素とを含む絶縁膜であるZrBO膜を基板Sの表面及び該基板Sの有する貫通孔の内面に形成する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビアに位置ずれが生じても、ビアがエアギャップにつながることを抑制できるようにする。

【解決手段】複数の配線240は例えばCu配線であり、互いに平行に延伸している。側壁絶縁膜212は、複数の配線240それぞれの側壁に形成されている。エアギャップは、複数の配線240それぞれの相互間に形成され、複数の側壁絶縁膜212の間に位置している。絶縁膜302は、複数の配線240上、複数の側壁絶縁膜212上、およびエアギャップ214上に形成されている。ビア344は絶縁膜302を貫通しており、いずれかの配線240に接続している。そして側壁絶縁膜212は、絶縁膜302がエッチングされる条件では絶縁膜302よりエッチングレートが低い材料により形成されている。

(もっと読む)

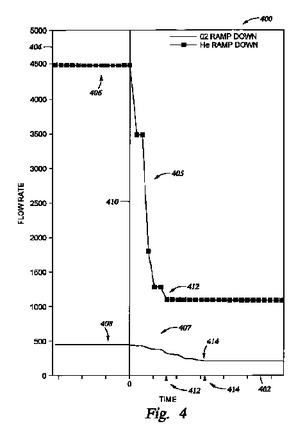

誘電体膜の材料特性を高めるための活性化学的方法

【課題】ケイ素含有誘電体材料の層の誘電率の修復

【解決手段】第1の誘電率および少なくとも1つの表面を有するケイ素含有誘電体材料の層の誘電率の修復方法であって、ケイ素含有誘電体材料の層の第1の誘電率が第2の誘電率まで増加しており、該方法は、ケイ素含有誘電体材料の層の少なくとも1つの表面と、ケイ素含有流体とを接触させるステップ、そしてケイ素含有誘電体材料の層の少なくとも1つの表面を、紫外線照射、熱、および電子ビームからなる群から選択されるエネルギー源に曝すステップ、の各ステップを含み、ケイ素含有誘電体材料の層は、ケイ素含有誘電体材料の層をエネルギー源に曝した後の第2の誘電率より低い第3の誘電率を有する、方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 膜ストレス低減を図った無機SOG膜を有した半導体装置及びその製造方法を提供する。

【解決手段】 本発明の半導体装置は、半導体基板1上に形成された下層配線3と、前記下層配線3上及び下層配線3間に形成され、不純物がイオン注入されることで圧縮応力を示す無機SOG膜5aと、前記無機SOG膜5aを含む層間絶縁膜7に形成されたコンタクトホールを介して前記下層配線に接続する上層配線とを具備することを特徴とする。

(もっと読む)

3次元集積のための裏側ダミー・プラグを含む半導体構造およびこれを製造する方法

マンガン含有低誘電率膜及びその製造方法、半導体装置の製造方法並びに成膜装置

【課題】マンガン含有材料を利用して、低誘電率膜への銅の拡散を防止する。

【解決手段】成膜装置100では、制御部70の制御に基づき、処理容器1内を真空にして、ヒーター6によりウエハWを加熱しつつ、シャワーヘッド11のガス吐出孔13a,13bからウエハWへ向けて低誘電率材料とマンガン含有材料とを含む成膜ガスを供給する。高周波電源23からシャワーヘッド11に高周波電力を供給することにより、成膜ガスを解離させ、処理容器1内に成膜ガスのプラズマを生成させる。このプラズマによって、ウエハWの表面にMnを含有するSiCOH膜を成膜する。

(もっと読む)

低誘電率誘電体を含む超小型電子構造およびその構造内の炭素分配を制御する方法

本発明の実施形態は、超小型電子構造の形成に関する。32nmの次のテクノロジーノード向けの低誘電率誘電体材料は、約2.6未満の誘電率を呈する必要がある。本発明により、全体として超小型電子構造の曲げおよび剪断強度の完全性を向上させながら、そのような低誘電率誘電体材料を使用する半導体デバイスを形成することが可能になる。  (もっと読む)

(もっと読む)

導体層の形成方法及び半導体装置の製造方法

【課題】レジスト残滓を確実に除去する。

【解決手段】基板10上の一部にレジスト20を用いて導体層19をパターニングした後、レジスト20を剥離するレジスト剥離工程と、基板10の導体層19が形成された面に対して、第一ノズル103から第一噴射圧で溶剤を噴射することによりレジスト20の残滓20bをふやかし、第二ノズル104から第一噴射圧よりも高圧の第二噴射圧で溶剤を噴射することによりレジスト20の残滓20bを物理力で除去するレジスト残滓除去工程と、を備える導体層の形成方法である。

(もっと読む)

半導体装置、及びその製造方法

【課題】配線の導通信頼性を損なうことなく、エアギャップを形成でき、配線間容量Cが低減した配線膜構造を有する半導体装置を提供することである。

【解決手段】 半導体装置の製造方法において、第1絶縁膜を形成する第1絶縁膜形成工程と、前記第1絶縁膜に配線膜を形成する配線膜形成工程と、前記配線膜が形成されてない箇所の前記第1絶縁膜にドライエッチングで溝を形成するドライエッチング工程と、前記ドライエッチング工程の後、前記溝が埋め尽くされることが無いよう、前記配線膜および前記溝上に第2絶縁膜を形成する第2絶縁膜形成工程とを具備する。

(もっと読む)

構造体および構造体を形成する方法

【課題】 サブリソグラフィ・ピッチの構造体とリソグラフィ・ピッチの構造体との相互接続を形成する。

【解決手段】 サブリソグラフィ・ピッチを有する複数の導電線をリソグラフィでパターン形成し、複数の導電線の縦方向から45度より小さい角度の線に沿って切断することができる。代わって、ホモポリマーと混合した共重合体を陥凹エリア内に入れて自己整合し、一定幅領域内にサブリソグラフィ・ピッチを有し、台形領域で隣接線間にリソグラフィ寸法を有する複数の導電線を形成することができる。さらに代わって、サブリソグラフィ・ピッチを有する第1の複数の導電線と、リソグラフィ・ピッチを有する第2の複数の導電線は、同じレベルでまたは異なるレベルで形成することができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】主にアルミニウム系通常配線を有するLSIの製造工程BEOLプロセスでは、配線の信頼性に関して、EM耐性およびSM耐性の向上が特に重要である。アルミニウム系配線に関する不良の中でも、配線メタル膜の膨張や欠けの発生は、EM耐性およびSM耐性を大きく劣化させる要因となる。

【解決手段】本願発明は、層間絶縁膜を成膜するプラズマCVDチャンバのウエハ・ステージ上に於いて、アルミニウム系配線メタル膜のパターニングの後であって層間絶縁膜の成膜前に、ウエハのデバイス面に対して、不活性ガスを主要な成分の一つとして含む雰囲気下、アルミニウム系配線メタル膜および層間絶縁膜の成膜温度よりも高いウエハ温度において、プラズマ・アニール処理を実行することにより、配線メタル層の側壁部の付着物が完全に除去され、膨張不良の原因が取り除かれ、更に、不動態化の進行、ストレス開放等により、欠け不良を抑制するものである。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

1 - 20 / 141

[ Back to top ]