Fターム[5F033RR22]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 有機材料 (4,730) | ポリイミド系樹脂 (1,337)

Fターム[5F033RR22]に分類される特許

1 - 20 / 1,337

半導体装置及びその製造方法

半導体ウェハ、半導体装置及びその製造方法

半導体ウェハ、半導体装置及びその製造方法

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

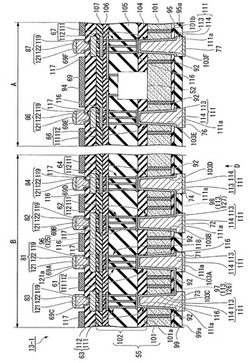

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

配線の形成方法、電子素子、および表示装置

【課題】物理的な版を必要とせず、微細な導電パターンを形成でき、パターン変更に対して柔軟に対応できる配線の形成方法を提供する。

【解決手段】本発明では、基板上に、エネルギー付与によって臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程と、前記濡れ性変化層に選択的にレーザ光を照射して、前記濡れ性変化層の臨界表面張力が高くなるように変化させた高表面エネルギー領域部を前記濡れ性変化層に形成する工程と、前記高表面エネルギー領域部に導電性インクを塗布し、前記高表面エネルギー領域部上に配線を形成する工程と、を有し、前記濡れ性変化層と前記高表面エネルギー領域部とには段差がなく、前記配線は前記高表面エネルギー領域部上に形成されていることを特徴とする配線の形成方法が提供される。

(もっと読む)

半導体装置

【課題】本明細書では、半導体装置が短絡状態で動作する場合における、半導体装置全体の短絡耐量を向上させることができる半導体装置を提供する。

【解決手段】本明細書が開示する半導体装置2は、素子領域60と、表面電極36と、熱伝導部材40と、保護膜38とを備える。素子領域60は、複数個のゲート電極22を備える。表面電極36は、素子領域60の表面に形成されている。熱伝導部材40は、表面電極36の中心部の表面側に形成され、素子領域60の熱伝導率よりも高い熱伝導率を有している。保護膜38は、表面電極36の表面側であって、中心部の周囲を取り囲む周辺部に形成されている。素子領域60は、表面電極36の中心部の裏面側に形成されるエミッタ中心領域70では、表面電極36の周辺部の裏面側に形成されるエミッタ周辺領域72と比較して、オン状態となる時間が長い。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマークに集中する応力の方向依存性を低減して、クラックを発生しにくくする。

【解決手段】基板の第1の主面に、環状の第1の溝及びドット形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

半導体集積回路装置

【課題】チップあたりの端子数の増大に伴って、フリップチップ実装が種々の形態で実施されている。しかし、バンプピッチの微細化およびバンプの鉛フリー化によって、エレクトロマイグレーション耐性の確保がますます重要となっている。

【解決手段】本願の発明は、フリップチップ型の半導体集積回路装置において、チップの第1の主面上に形成された多数のUBMパッド状の各々に設けられた半田バンプの中間部には、上下を分割する前記半田バンプとは異なる材質の金属隔壁が設けられているものである。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】第2の金属膜を形成するためのめっき液が電極と反応することを抑制することができる半導体装置と、その製造方法を提供する。

【解決手段】半導体基板12の表面の一部に形成されている表面電極14の外周縁部の表面を被覆する保護膜16を形成する。保護膜16の内周端面30に複数個の凹部32を形成する。表面電極14のうち保護膜16で被覆されていない部分の表面に第1の金属膜18を形成する。第1の金属膜18は、その一部が凹部32の間に入り込んで形成される。次いで、第1の金属膜18の表面に、第1の金属膜18と異なる金属で第2の金属膜20を形成する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

積層半導体基板、半導体基板および積層チップパッケージ並びにこれらの製造方法

【課題】単位時間あたりに製造できる積層チップパッケージの個数を増やして積層チップパッケージの製造コストを低減する。

【解決手段】積層半導体基板100は、複数の半導体基板1が積層されている。各半導体基板1はスクライブラインに沿った複数のスクライブ溝部20,21が形成されている。また、各半導体基板1は半導体装置が形成され、それぞれ絶縁されている複数のデバイス領域10と、複数のデバイス領域10のそれぞれに形成されている半導体装置に接続され、かつデバイス領域10からスクライブ溝部20,21の内側に延出している複数の配線電極15とを有している。複数の配線電極15は部分配置パターンで配置され、スクライブ溝部20,21を挟んで隣り合う2つのデバイス領域10のうちのいずれか一方だけから延出している。

(もっと読む)

半導体ウェハ、半導体装置及びその製造方法

【課題】アライメントマーク終端部への応力集中により基板にクラックが発生することを軽減する。

【解決手段】基板の第1の主面に、第1の主面に対向して見た場合に、環状の第1の溝及び終端部を有さない形状の第2の溝を形成する。第1及び第2の溝を埋め込むように絶縁膜を形成した後、基板の第1の主面にフォトレジスト膜を形成する。絶縁膜で埋め込まれた第2の溝の基板上での位置を基準として位置合わせした第1のパターンを、フォトレジスト膜に転写する。絶縁膜で埋め込まれた環状の第1の溝の内側に位置する基板に、基板を厚さ方向に貫通する貫通電極を形成する。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ異なるマスクを用いた個別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、酸化物半導体層の下に第1の電極層および第2の電極層を設けてコンタクト抵抗の低減を図る。

(もっと読む)

半導体装置の製造方法

【課題】穴部の側壁を基板の表面に対して垂直に形成するとともに、高速にシリコン層をエッチングするプラズマエッチング方法を提供する。

【解決手段】レジスト層をマスクとしてシリコン層をプラズマエッチングする方法であって、前記プラズマエッチング工程が、所定の比率で混合した堆積性ガスおよびエッチング性ガスの混合ガスを処理容器内に導入し、該混合ガス雰囲気で前記被処理基板をプラズマエッチングする第1のエッチングステップと、前記処理容器内に前記堆積性ガスを導入し、前記第1のエッチングステップによりプラズマエッチングされた被処理基板を該堆積性ガスが主体の雰囲気で堆積処理する堆積ステップ、および、前記処理容器内に前記エッチング性ガスを導入し、前記堆積ステップにより堆積処理された被処理基板を該エッチング性ガスが主体の雰囲気でプラズマエッチングする第2のエッチングステップを、複数回繰り返す。

(もっと読む)

半導体装置

【課題】高温環境下で使用することができる半導体装置を提供する。

【解決手段】第1インナー電極と第2インナー電極との積層からなるワイヤー接続領域を合金化防止溝によって第1アウター電極および第2アウター電極と分離することでワイヤーボンディング界面から成長したAu−Al合金層の進行を抑制し、半導体装置表面のパッシベーション膜のクラックを防止する。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

1 - 20 / 1,337

[ Back to top ]