Fターム[5F033SS07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の成膜方法 (10,269) | PVD(物理的気相成長法) (621)

Fターム[5F033SS07]の下位に属するFターム

Fターム[5F033SS07]に分類される特許

1 - 20 / 109

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を有する半導体装置の製造方法において、埋設導電部間のショートが起き難くすること。

【解決手段】半導体素子を有する素子領域と貫通電極が形成される貫通電極領域とを有する基板の上に第1絶縁膜を形成し、前記素子領域上の前記第1絶縁膜に凹部を形成し、前記貫通電極領域上の前記第1絶縁膜にダミー凹部を形成し、前記第1絶縁膜上、前記凹部内、および前記ダミー凹部内に第1導電材を形成し、前記第1導電材および前記第1絶縁膜の上部を研磨して、前記凹部内に導電部を形成すると共に前記ダミー凹部内にダミー導電部を形成し、前記貫通電極領域上の前記第1絶縁膜および前記貫通電極領域をエッチングして前記基板内に至る貫通電極ホールを形成した後、前記貫通電極ホール内に第2導電材を形成し、前記貫通電極ホール内に形成された第2導電材が露出するまで前記基板の裏面を研磨して、前記貫通電極を形成すること。

(もっと読む)

貫通配線基板および貫通配線基板の製造方法

【課題】貫通孔内に形成された導電層に加わる応力を抑制できるとともに、導電層からの効果的な放熱も促すことができる貫通配線基板、及びこの貫通配線基板の製造方法を提供する。

【解決手段】半導体基板11(基板)の一方の面11aに配された電極層12と、電極層12の少なくとも一部が露呈するように半導体基板11内に開けられた貫通孔20と、貫通孔20の内側面20aを覆い、電極層12の少なくとも一部が露呈するように配された第一絶縁層15と、第一絶縁層15を介して、貫通孔20の内側面20a及び電極層12の露呈部を覆うように配され、電極層12と電気的に接続された導電層5と、導電層5を覆うように配された第二絶縁層16と、を少なくとも備えてなる貫通配線基板10であって、第二絶縁層16は、導電層5の表面形状に沿って形成されていることを特徴とする。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法

【課題】ボンディングパッドおよびシールド構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体装置の正面と背面に対応する正面と背面を有する装置基板と、装置基板の正面上に形成される金属層部と、半導体装置の背面に設置され、金属層部と電気的に接続するボンディングパッドと、装置基板の背面上に設置されるシールド構造と、を含み、シールド構造とボンディングパッドは異なる厚さを有する。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

導電性ビアの製造と充填のための方法、およびそのように形成された導電性ビア

【課題】ビアホール表面上の絶縁コーティングとビアホール内に挿入される導電材料との付着性を向上する。

【解決手段】導電性ビアを形成する方法は、一つ以上のビアホールを基板内に形成するステップを含む。ビアホールは、単一マスク、保護層、ボンドパッド、もしくは、エッチングプロセスの間にフォトマスクが除去される場合にハードマスクとして機能する、基板のその他のフィーチャで形成され得る。ビアホールは、その表面に低誘電率(低K)誘電材料を含む誘電体コーティングの付着を促進するように構成されてもよい。障壁層が各ビアホールの表面の上に形成されてもよい。種材料(seed material)を含み得るベース層は、その後のビアホールの表面上の導電材料の選択的堆積を促進するように形成されてもよい。

(もっと読む)

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

【課題】公知のプロセスよりも高速であり、充てんされたビアにボイド、凹み又はキーホールを残さず、製造の費用効果が高い、改善された方法を提供する。

【解決手段】第1の表面214及び対向する第2の表面216を有する基板212を設け、基板の第1の表面に部分的にのみ前記基板の中に広がる少なくとも1つのブラインドビア218を形成する。酸化材料によって前記少なくとも1つのブラインドビアの表面をパッシベーションし、少なくとも一つのブラインドビアの酸化材料の表面に銅を含むシード材料228を、シード材料を前記少なくとも一つのブラインドビアの内部に閉じ込め、かつ、基板の前記第1の表面を露出させるように形成する。シード材料の上に導電性材料230を前記少なくとも一つのブラインドビアを充填するように無電解めっきし、少なくとも一つのブラインドビアの導電性材料を露出させるために基板の前記第2の表面に研磨平坦化を実施する。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法に関し、工程マージンを向上させる。

【解決手段】半導体素子は、半導体基板10に備えられるメインゲート20及び素子分離構造、前記素子分離構造の上部に備えられる分離パターン40及び前記分離パターンの両端に備えられるコンタクトプラグ54を含む。格納電極コンタクトと活性領域との間のフルオーバーラップを提供し、食刻工程でのオーバーレイ問題を解消し、格納電極の食刻線幅を増加させる。

(もっと読む)

半導体装置

【課題】半導体基板を貫通する基板貫通孔に埋め込まれた基板貫通電極と該半導体基板との間の絶縁膜に対してその絶縁性を高めることの可能な半導体装置を提供する。

【解決手段】第1シリコン基板11と、前記第1シリコン基板11に形成された第1多層配線層12と、前記第1シリコン基板11を貫通して前記第1多層配線層12の内部に延びる基板貫通孔Hと、前記基板貫通孔H内に埋め込まれた基板貫通電極18と、前記基板貫通孔Hの内周面と前記基板貫通電極18の外周面とに挟まれた絶縁膜17とを備え、前記絶縁膜17が、金属元素の酸化ホウ化物膜であって、前記金属元素が、アルミニウム、チタン、バナジウム、ジルコニウム、ハフニウム、ベリリウム、及びマグネシウムのいずれか一つである。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

半導体構造同士を直接結合する方法、およびこの方法を使用して形成された結合された半導体構造

【課題】半導体構造同士を直接結合する方法を提供すること。

【解決手段】本発明の実施形態は、半導体構造同士を直接結合する方法を含む。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ間の境界面に、キャップ層を提供することができる。いくつかの実施形態では、半導体構造の直接結合された金属フィーチャ内に、不純物が提供される。そのような方法を使用して、結合された半導体構造が形成される。

(もっと読む)

半導体装置、その製造方法、および半導体装置を含む半導体パッケージ

【課題】装置特性の低下を防止するとともに、半導体基板と貫通電極の短絡を防止する半導体装置を提供する。

【解決手段】第1面と、第1面と対向してトレンチが形成された第2面とを有する基板と、基板内に形成されたビアホールを充填し、ビアホールの内壁から順にビアホール絶縁膜、障壁膜、および導電性接続部を有してなる貫通ビアと、第2面上に形成されて貫通ビアの一部領域を露出する開口部を有する絶縁膜と、トレンチ内に埋め込まれ、貫通ビアと電気的に接続される再配線と、を有し、絶縁膜は導電性接続部の一部領域と重複する。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

ウエハレベルパッケージ構造およびその製造方法

【課題】切削刃の磨耗を抑制して切削刃の寿命を延ばすことが可能なウエハレベルパッケージ製造方法を提供する。

【解決手段】ウエハレベルパッケージ製造方法は、例えば、基板450の表面に、配線が形成される溝462を含む絶縁性の第1の樹脂460を形成する樹脂形成工程400と、第1の樹脂460の表面に、配線の一部となる第1の金属470を、物理気相成長によって成膜する第1の成膜工程410と、第1の金属470の表面に、配線の一部となる、第1の金属470より硬度が低い第2の金属480を、更に成膜する第2の成膜工程420と、溝462の側面において第1の金属470が成膜されていない場所または薄くなっている場所に該当する高さH0、H1に切削刃490を設置する設置工程430と、切削刃490を走査することにより、少なくとも第1の樹脂460を切削する切削工程440とを含む。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

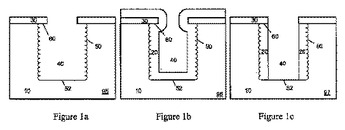

ビア及びエッチングされた構造におけるコンフォーマル絶縁層の形成方法及びパターン形成方法

マスク層の下にアンダーカット形状を形成するエッチングプロセスによって基板にビアが形成される。ビアはコンフォーマルな絶縁層で覆われ、この構造にエッチングプロセスを実施して水平面から絶縁層を取り除くと共にビアの垂直な側壁の絶縁層を残す。ビアの上部領域はエッチバックプロセスの際、アンダーカットハードマスクによって保護される。  (もっと読む)

(もっと読む)

半導体装置のパッド構造

【課題】半導体装置のパッド構造を提供する。

【解決手段】半導体装置200は、半導体基板202、相互接続構造、複数のダミーメタルビア235及びパッド構造を備える。半導体基板202は、内部に複数の微小電子素子が設けられている。相互接続構造は、半導体基板202上に設けられ、複数の金属層210a〜210iと、金属層を隔離する複数のIMD層220とを有する。金属層210a〜210iは、最上金属層210iと、最下金属層210aと、最上金属層210iと最下金属層210aとの間に設けられた少なくとも2層の金属層とを含む。複数のダミーメタルビア235は、少なくとも2層の金属層間に設けられた1層又は2層以上のIMD層220内に形成される。パッド構造は、ダミーメタルビア235の上に直接設けられている。

(もっと読む)

1 - 20 / 109

[ Back to top ]