Fターム[5F033TT03]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の構造、形状 (4,088) | 積層構造 (1,984) | 全てが有機材料 (79)

Fターム[5F033TT03]に分類される特許

1 - 20 / 79

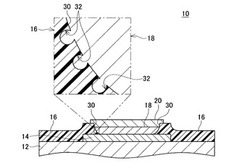

半導体装置の製造方法と半導体装置

【課題】第2の金属膜を形成するためのめっき液が電極と反応することを抑制することができる半導体装置と、その製造方法を提供する。

【解決手段】半導体基板12の表面の一部に形成されている表面電極14の外周縁部の表面を被覆する保護膜16を形成する。保護膜16の内周端面30に複数個の凹部32を形成する。表面電極14のうち保護膜16で被覆されていない部分の表面に第1の金属膜18を形成する。第1の金属膜18は、その一部が凹部32の間に入り込んで形成される。次いで、第1の金属膜18の表面に、第1の金属膜18と異なる金属で第2の金属膜20を形成する。

(もっと読む)

配線部材、および、電子素子の製造方法と、それを用いた配線部材、積層配線、電子素子、電子素子アレイ及び表示装置。

【課題】印刷法による少ない工程数のメリットを生かしつつ、より微細であり、絶縁性の低下がなく、導電部寸法精度の高い、配線部材および電子素子の製造方法を提供することを目的とする。また、配線部材、積層配線、電子素子、電子素子アレイ及び表示装置を提供することを目的とする

【解決手段】基板上にエネルギーの付与により臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程、紫外領域のレーザーを用いたレーザーアブレーション法により、濡れ性変化層に凹部を形成する工程、凹部に導電性インクを塗布して導電部を形成する工程、を含み、前記濡れ性変化層の凹部のパターン形成と同時に、前記臨界表面張力を変化させて高表面エネルギー領域のパターン形成が行われることを特徴とする配線部材の製造方法、電子素子の製造方法、及び、それにより得られた配線部材、電子素子を提供する。また、電子素子アレイ及び表示装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、保護膜の境界面での膜厚を厚くし、はんだが金属膜の下方に侵入し難い半導体装置を提供することを目的とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】電極パッドの表面の突出部に起因する不具合が発生し難い半導体装置の製造方法及び半導体装置を提供する。

【解決手段】半導体装置の製造方法は、表面の突出部に突出部、例えば、プロービング痕21が存在する電極パッド2を備える基板1上に、電極パッド2の少なくとも一部を覆う第1の絶縁膜4を形成する第1の絶縁膜形成工程と、第1の絶縁膜4の表面から突起した部分22を除去することができる処理を行う除去処理工程と、除去処理工程後に、第1の絶縁膜4上及び電極パッド2上に第2の絶縁膜5を形成する第2の絶縁膜形成工程とを有する。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

半導体装置

【課題】プロセス加工性と信頼性に優れた半導体装置を提供する。

【解決手段】必要な回路が形成された半導体表面に、エポキシ樹脂、エポキシ樹脂硬化剤及び平均一次粒子径1μm以下の有機フィラーの成分を含む樹脂組成からなる絶縁層を1層又は複数層備え、かつ同一層内及び層間接続の配線導体として銅を用いた回路3を任意の箇所に形成してなる半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】半導体素子の第1領域と接続される表面電極17、および通路12の少なくとも一部に、半導体素子の第2領域と接続される第1金属配線18を形成する。その後、はんだ29が実装されない通路12bに形成する第1保護膜25の高さが、はんだ29が実装される通路12aに形成する第1保護膜25の高さよりも高くなるように、注入器32を用いて第1保護膜25を通路12に塗布する。続いて、表面電極17および第1保護膜25の上に金属層27、28を形成してはんだ29が実装されない通路12bに形成した第1保護膜25が金属層27、28から露出するように、はんだ29が実装されない通路12bに形成した第1保護膜25の一部および金属層27、28を切削する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグを、配線のバリア層に安定して接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、バリア層を介して配線に接続されたコンタクトプラグ、第1及び第2の絶縁膜を有する。第1の絶縁膜は、配線及びバリア層の側面を覆い少なくともバリア層よりも上方で配線が延在する方向と直交する方向の幅が狭まる傾斜面を有し、バリア層の上面の一部を露出すると共に配線及びバリア層の側面を露出させないように形成された開口部を備える。第2の絶縁膜は、開口部の内側を除き第1の絶縁膜上に形成され、かつ開口部を備える。

(もっと読む)

制御された気孔を形成するための材料及び方法

【課題】基材の内部に空隙を形成するための方法を提供する。

【解決手段】基材を用意する工程;少なくとも1つの犠牲材料前駆体の堆積によって犠牲材料を堆積する工程;複合層を堆積する工程;該複合層中のポロゲン材料を除去して多孔質層を形成する工程;及び積層基材を除去媒体と接触させて前記犠牲材料を実質的に除去し、前記基材の内部に空隙を与える工程を含み、前記少なくとも1つの犠牲材料前駆体が、有機ポロゲン、シリコン、極性溶媒に可溶な金属酸化物、及びそれらの混合物からなる群より選択される方法が提供される。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子の信頼性を劣化させることなく、より比誘電率の低い絶縁膜を形成する。

【解決手段】この半導体装置の製造方法は、下地膜101に、環状シロキサンをプラズマ重合させて第一の絶縁膜102を形成する工程と、第一の絶縁膜102を形成する工程の後、連続的に、第一の絶縁膜102上に、環状シロキサンをプラズマ重合させて第二の絶縁膜103を形成する工程と、を含む。第一の絶縁膜102の成膜速度は、第二の絶縁膜103の成膜速度よりも遅い。

(もっと読む)

半導体基板、積層チップパッケージおよび半導体プレート並びにこれらの製造方法

【課題】積層チップパッケージの電気的な接続に関する信頼性を高める。

【解決手段】半導体基板はスクライブラインに沿って複数の溝部が形成されている。半導体基板は、複数の溝部のいずれか少なくとも一つに接する単位領域と、その単位領域内に一部が配置されている配線電極とを有している。そして、複数の溝部は、底部を含む溝下部よりも幅の広い幅広部が入り口に形成されている口広構造を有している。半導体基板は、幅広部が入り口の長さ方向全体に形成されていてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のバンプが十分な反発力と十分な密着性とを兼ね備えるようにし、バンプの接続性を向上させる。

【解決手段】半導体装置100は、電極パッド2と、電極パッド2を露出させる開口3aが形成された保護絶縁膜3を有する。更に、保護絶縁膜3上に形成されたバンプコア(樹脂コア4)と、バンプコア上に形成された導電層5aと、を含むバンプ(樹脂コアバンプ6)を有する。更に、導電層5aと電極パッド2とを接続する配線5bを有する。バンプコアは、互いに弾性率が異なる複数の樹脂層(例えば、第1及び第2樹脂層11、12)の積層構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の良好な半導体装置及びその製造方法を提供することにある。

【解決手段】一方の主面に於ける半導体素子領域2内に複数の機能素子が配設された半導体基板1と、半導体基板1の一方の主面上に配設され、複数の配線層3と複数の絶縁層4とを含む多層配線層2と、多層配線層2上に形成された第1の有機絶縁物層6と、第1の有機絶縁物層上に形成され、配線層に電気的に接続された他の配線層と、第1の有機絶縁物層6上に、他の配線層を覆うように形成された第2の有機絶縁物層10とを具備し、半導体素子領域を囲む半導体基板領域に、多層配線層を貫く溝が半導体素子領域を囲繞して配設されており、溝内には、前記有機絶縁物層6、有機絶縁物層10のいずれからも分離された有機絶縁物が配設されている。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜を備えた半導体装置において、膜剥がれの発生及びリークパスの形成を抑制する。

【解決手段】半導体装置は、複数の空孔を含む層間絶縁膜16を備えている。層間絶縁膜16は、単層構造の膜である。層間絶縁膜16における、下面領域に含まれる空孔の空孔径及び上面領域に含まれる空孔の空孔径は、上面領域と下面領域との間に介在する中央領域に含まれる空孔の空孔径よりも小さい。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート配線が保護膜に覆われた構造において、保護膜に発生するクラックがゲート配線に到達することを防止することにより、ゲート−エミッタ間のショート不良を防止する。

【解決手段】第1保護膜25が表面電極17およびゲート金属配線18の間に配置されると共に、ゲート金属配線18を覆っている。また、第2保護膜26が第1保護膜25の上に形成されている。この場合、第2保護膜26は、第1保護膜25のうちの少なくともはんだ29に覆われる部分の上に形成されている。これにより、はんだ29実装前に引っかき傷等によって第2保護膜26にクラック31が発生したとしても、当該クラック31の進展を第1保護膜25と第2保護膜26との境界面で阻止することができる。

(もっと読む)

1 - 20 / 79

[ Back to top ]