Fターム[5F033UU07]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | シミュレーション (64)

Fターム[5F033UU07]に分類される特許

1 - 20 / 64

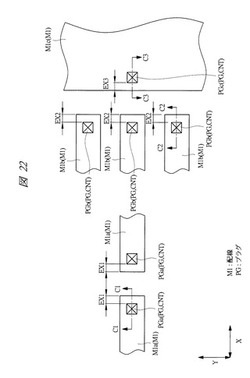

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】基板を実装する際の温度負荷によって絶縁層と下地金属層の側面との接点領域に加わる応力を緩和させ、応力に起因した絶縁層のクラックの発生を抑えるように構成された半導体装置を提供する。

【解決手段】半導体基板101の一面101aに、絶縁層102、下地金属層103、金属端子が設けられるためのランド部104を順に積層してなる半導体装置109であって、ランド部104は、絶縁層102と対向する面の中央部において、下地金属層103と接合する接合領域と、絶縁層102と対向する面において、接合領域を除いた非接合領域と、を有し、下地金属層103は、ランド部104側から絶縁層102側にかけて外向きに傾斜した側面を有していること、を特徴とする半導体装置109。

(もっと読む)

半導体装置における電流による配線破壊箇所の予測方法

【課題】半導体装置の電流による配線破壊箇所の予測方法において、解析時間を短縮する。

【解決手段】下層配線14A,14Bをそれぞれ一つの直列抵抗で、第1の下層ビア15A,第2の下層ビア15Bを1個の抵抗で、第1の上層ビア17A、第2の上層ビア18Bを1個の抵抗で、第1及び第2の上層配線16A,16Bを抵抗ブリッジ回路で、パワートランジスタTRを直列抵抗で、それぞれモデリングしてなる解析モデルをモデリング用計算機により生成する。回路シミュレータ3により、解析モデルにおけるパワートランジスタTRに電流を供給し、解析モデルにおける各抵抗に流れる電流に基づいて、第1及び第2の下層配線14A,14B、第1及び第2の上層配線16A,16Bにおける各抵抗の電流密度を計算し、各抵抗の電流密度と、配線破壊を起こす電流密度閾値とを比較器4により比較することにより、配線破壊箇所を予測する。

(もっと読む)

半導体装置およびその製造方法

【課題】絶縁膜に発生するクラックを抑制できる技術を提供する。

【解決手段】実施の形態におけるパッド構造では、単に電極層OPM1の周縁部が、平面視において、パッドPAD1の周縁部よりも内側に位置する(図8ではパッドPAD1の周縁部と絶縁膜PASに形成された開口部OP1の端部との間に位置する)ように電極層OPM1を形成するだけでなく、図8に示すように、パッドPAD1の厚さをAとし、絶縁膜PASの厚さをBとし、開口部OP1内から絶縁膜PASの端部(開口部OP1の周囲)上にはみ出す電極層OPM1のはみ出し量をCとし、電極層OPM1の厚さをDとした場合に、B≒D(図8ではB<D)を前提として、A<Bの関係を成立させることにより、B>Cの関係を成立させている。これにより、絶縁膜PASにクラックが発生することを防止できる。

(もっと読む)

素子搭載用基板、半導体モジュールおよび携帯機器

【課題】半導体素子との接続信頼性の向上が可能な突起電極を有する素子搭載用基板を提供する。

【解決手段】素子搭載用基板20は、絶縁樹脂層32と、絶縁樹脂層32の一方の主表面S1に設けられた配線層34、その配線層34と電気的に接続され、配線層34から絶縁樹脂層32側に突出している突起電極36とを備える。この突起電極36に半導体素子50が電気的に接続されて半導体モジュール10が形成される。突起電極36の頂部面には凹部が設けられている。この凹部は突起電極36の側面に設けられた開放口と連通している。

(もっと読む)

半導体装置

半導体装置が半導体基板上のゲートを含む。ゲートの1つの側壁が少なくとも1つの突出部を含んでいてもよく、ゲートの反対側壁が少なくとも1つの凹部を含んでいてもよい。接触部が、ゲート上に配置された絶縁層を通して形成されている。接触部は、ゲートの少なくとも1つの突出部に少なくとも部分的に重なっている。金属層が絶縁層上に配置されている。金属層は、ゲートの第1の側に移動した第1の構造を含む。接触部が絶縁層を通して第1の構造をゲートに電気的に連結するように、第1の構造は接触部に少なくとも部分的に重なっている。 (もっと読む)

半導体装置

【課題】デジタル領域とアナログ領域とが混載された半導体装置におけるデジタル領域からアナログ領域へのノイズ伝搬を効果的に抑制する。

【解決手段】デジタル領域120とアナログ領域130とが混載された半導体装置100は、平面視でデジタル領域120およびアナログ領域130の外周を取り囲む環状のシールリング140と、シールリング140で囲まれた領域内で、デジタル領域120とアナログ領域130との間に設けられ、アナログ領域130をデジタル領域120から隔離するとともに、シールリング140に電気的に接続されたガードリング150と、ガードリング150と当該ガードリング近傍で電気的に接続された電極パッド160aとを含む。電極パッド160aは、外部の接地端子(180a)に接続されて接地電位とされている。

(もっと読む)

半導体集積回路

【課題】配線の幅とピッチが変化する部分の欠陥に対するマージンを十分に確保することが可能な半導体集積回路を提供する。

【解決手段】第1、第2の配線11,12は、配線の幅と配線間のスペースの幅が等しい。第3の配線13は、第1の配線11の一端に接続され、幅が第1の配線11の幅とスペースの幅に等しく、第2の配線12の側部に接続されている。第2の配線12は一部にギャップGを有している。

(もっと読む)

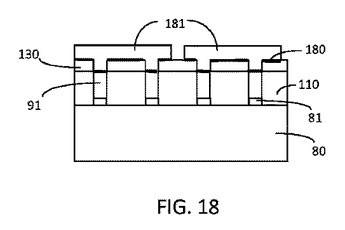

金属/有機誘電体界面でのクラックの低減

有機誘電体材料(110)中に埋め込まれた第2構造(91)への金属相互接続(181)を提供する方法であって、有機誘電体材料(110)中に埋め込まれた、例えば金属ピラー(91)のような第2構造を有する第1構造を得る工程と、少なくとも第1構造のいくつかの位置で、有機誘電体材料(110)の上に硬い層(130)を提供する工程であって、硬い層(130)は有機誘電体材料(110)の剛性より高い剛性を有する工程とを含む方法。この方法は、第1構造(91)と有機誘電体材料(110)との間の界面でクラックの無い相互接続構造を提供する。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】表面電極にはんだ接合層を有する半導体装置において、その製造工程でウェハの反りやはんだ接合層のクラックが発生することを抑制する。

【解決手段】表面電極は、半導体基板に接する第1層として250℃以下の基板温度でスパッタ法によってAl−Si層またはAl−Si−Cu層を形成し、その表面に積層する第2層として400℃以上の基板温度でスパッタ法によってAl層またはAl−Cu層を形成し、その表面側に、はんだ接合層、はんだ層を形成することによって、製造する。

250℃以下の基板温度で第1層を形成するため、シリコンノジュールの発生を防止することができ、第2層を400℃以上の基板温度で形成するため、第2層の平坦性を確保でき、ウェハの反りやはんだ接合層のクラック発生を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置、半導体装置の製造プログラム、マスクデータの生成プログラム

【課題】パターン上の被平坦化膜を平坦化する際に所定以上の段差が発生する箇所を迅速かつ的確に予測し、短時間でレイアウト修正を行うこと。

【解決手段】本発明は、製造対象となる回路の物理レイアウトデータを計算部11に読み込み、パターン幅を予め決められた量だけ変形する計算を行う工程と、計算部11から出力されるパターン幅を変形した後の物理レイアウトを解析部12に読み込み、注目範囲および注目範囲の周辺範囲のパターンの密度、パターン幅、周辺長のうち少なくとも1つを用いて定量的な計算により、パターン上の被平坦化膜を平坦化処理した際に所定以上の段差として残ると予測されるパターンを解析する工程と、解析部12から出力される段差として残ると予測されるパターンのデータを修正部13に読み込み、所定以上の段差が残らないレイアウトもしくは製造条件へ修正する工程とを有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【目的】プロービング試験での導電パッド下に配置された金属配線上の絶縁膜のクラック発生を抑制することが可能な半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、導電パッドと、前記導電パッド上に配置され、前記導電パッドの一部が露出するように開口領域が形成された第1の絶縁膜と、前記導電パッドの下方に配置された第2の絶縁膜と、銅(Cu)を用いた配線を有し、前記第2の絶縁膜を介して前記導電パッドの下方に配置され、前記開口領域と重なる領域での最上層における前記配線の最大配線幅w(nm)と前記配線の被覆率R(%)とがある条件を満たすように配置された少なくとも1層の配線層と、を備えたことを特徴とする。

(もっと読む)

金属相互接続線を形成するための方法

【課題】金属相互接続線の形成方法を提供する。

【解決手段】基板にトレンチを画定するエッチング・ステップと、金属の電着によって前記トレンチを充填するステップとを含み、金属の結晶粒で充填された前記トレンチの上に金属侵入層を形成するステップを含み、さらに、トレンチに沿った結晶粒方位の第1の方向と、トレンチに垂直な方向での結晶粒方位の第2の方向とを決定するステップと、前記金属の結晶格子内でのイオン・チャネリングの第3の方向を決定するステップと、前記金属侵入層内でのイオン注入ビームの向きDi1の少なくとも1つの方向を決定するステップと、イオン注入ビームの向きDi1の1つに応じて、侵入層にイオン・ビームによってイオン注入するステップと、を含む。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】多層配線構造の半導体装置のパッケージ工程や環境試験において、膜剥れが起き難い技術を提供する。

【解決手段】絶縁層中に配線層が構成された下層配線層、前記下層配線層上に設けられた層間絶縁層、前記層間絶縁層の上に設けられた絶縁層中に配線層が構成された上層配線層、及び前記層間絶縁層に構成された前記下層配線層の配線層と前記上層配線層の配線層とを電気的に接続する為の接続層とを具備する半導体装置において、

前記層間絶縁層A7に、該層間絶縁層A7の上層および/または下層に繋がる埋設層A15が構成され、前記埋設層A15および接続層A12を有する層間絶縁層A7の平均弾性率が10GPa以上であるよう構成されてなる半導体装置。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バンプの配列に疎密差があったときに発生する応力を緩和できる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】電極端子群を備える配線基板と、バンプ3群が形成されたバンプ形成面7を備え、バンプ3群が前記電極端子群と対向するように前記配線基板上に実装された半導体チップとを具備し、バンプ形成面7は、バンプ3が配置された領域の面積密度が第1密度である第1領域9と、バンプ3が配置された領域の面積密度が前記第1密度よりも小さい第2密度である第2領域10と、第1領域9と第2領域10との境界部分に設けられた第3領域11とを備え、第3領域11は、バンプ3が配置された領域の面積密度が、前記第2密度よりも大きく、前記第1密度よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】パターンの異なる複数のマスクの情報を考慮したプロセス制御が可能な半導体装置の製造方法を提供する。

【解決手段】次に処理を施す半導体ウェーハを選択し、処理装置の装置情報および選択された半導体ウェーハと同種の半導体ウェーハの処理結果に基づいて、半導体ウェーハを処理する第1処理条件を算出するステップと、第1処理条件に、半導体ウェーハにパターンを形成したマスクに対して予め定められた補正値を加算し、第2処理条件を算出するステップと、第2処理条件に従って、半導体ウェーハを処理するステップと、半導体ウェーハの処理結果を求め、処理結果を平均した第1平均値を求めるステップと、第1平均値と、第1平均値の履歴を平均した第2平均値との差を示すマスク誤差を求めるステップと、マスク誤差のマスク間バラツキが小さくなるように、処理時間と処理結果との関係から補正値を修正するステップとを具備する。

(もっと読む)

メッキ厚算出プログラム、メッキ厚算出装置およびメッキ厚算出方法

【課題】最適なメッキ厚を短時間で算出することを課題とする。

【解決手段】メッキ処理、研磨処理、過研磨処理の順に実行される半導体集積回路の製造処理の中で、過研磨処理により削り取られる導電体の削取導電体厚を過研磨処理時の研磨時間および研磨速度を用いて算出し、研磨処理後の基板上の配線溝以外の箇所に残存することが予想される残存導電体厚が、削取導電体厚以下となるまで、メッキ処理によって基板上にメッキされる導電体のメッキ厚を変更して、残存導電体厚を得るためにメッキ処理から前記研磨処理に至るシミュレーションを繰り返し実行する。

(もっと読む)

パターンレイアウトの修正方法

【課題】プロセスパラメータのばらつきが生じても仕様に合致した素子の製造を可能にするパターンレイアウトの修正方法を提供する。

【解決手段】設計レイアウトに対応するパターンを基板上に形成するためのプロセスパラメータのばらつきを反映させた複数の条件でプロセスシミュレーションを実行することにより、前記パターンの複数の仕上がりパターンを予測し(ステップS4)、得られた複数の仕上がりパターンの寸法を算出し(ステップS5)、算出された寸法から所定の統計量を算出し(ステップS6)、該統計量と予め設定された仕様とを比較し(ステップS7)、仕様を満たさない場合に(ステップS8)修正量を算出し(ステップS9)、算出された前記修正量に基づいて前記設計レイアウトを修正する(ステップS10)。

(もっと読む)

1 - 20 / 64

[ Back to top ]