Fターム[5F033VV08]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 受動素子 (1,084)

Fターム[5F033VV08]の下位に属するFターム

Fターム[5F033VV08]に分類される特許

1 - 20 / 204

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

配線構造およびその製造方法

【課題】複雑な配線構造であっても、電極パターン同士を簡単な構造で接続できると共に、配線パターンの強度をも確保できるような配線構造、およびこうした配線構造を製造するための有用な方法を提供する。

【解決手段】本発明の配線構造は、基板上に形成された少なくとも第1の配線パターンと第2の配線パターンを有する配線構造であって、前記第1の配線パターンと第2の配線パターンとの間は、金属ワイヤーによる空中配線部によって接続されると共に、少なくとも金属ワイヤー表面には、金属ワイヤーと同じ若しくは異なる素材からなる金属めっきが施されたものである。

(もっと読む)

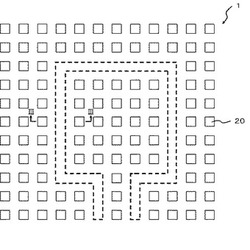

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】インダクタンス値を広範囲に可変可能なインダクタを備える半導体装置を提供する。

【解決手段】半導体装置は、多層配線層と、多層配線層を用いて形成され、巻軸が、多層配線層に対して平行である複数のソレノイド型インダクタと、少なくても1以上のソレノイド型インダクタと接続され、ソレノイド型インダクタの状態を活性化、又は、非活性化する制御回路と、を含んで構成される可変インダクタを備えている。

(もっと読む)

半導体装置

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

半導体装置

【課題】複数のスパイラルを直列に接続してインダクタを形成する場合において、スパイラルを大面積化することなく、スパイラルの巻線を長くする。

【解決手段】インダクタ10は、第1スパイラル100及び第2スパイラル200を有している。第1スパイラル100は、インダクタ10の巻軸と平行な第1の方向から見た場合、中心から外側に向かって巻かれている。第2スパイラル200は、第1の方向から見た場合、外側から中心に向かって、第1スパイラル100と同一の向きに巻かれている。第1スパイラル100及び第2スパイラル200は、外側の端部同士、または中心側の端部同士が、外側接続部材300又は中心側接続部材400を介して接続されている。第2スパイラル200は、第1スパイラル100を、巻軸を回転中心として右回りに90°回転させてから、巻軸に直交する平面に含まれる水平線を基準に鏡映させ、かつ縦横比を変更した形状である。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

電力分配合成器及び電力増幅器

【課題】入力の整合回路における損失の低減、並びに、回路の簡略化及び小型化が可能な電力分配合成器を提供する。

【解決手段】入力信号が入力される1次巻線としての環状の第1金属配線、及び、2次巻線としての複数の第2金属配線を有し、入力インピーダンスの整合をとるとともに、入力信号を複数の分配信号に分配する入力側トランスフォーマ120と、出力信号が出力される2次巻線としての環状の第3金属配線、及び、1次巻線としての複数の第4金属配線を有し、複数の分配信号を合成することで出力信号を出力するとともに、出力インピーダンスの整合をとる出力側トランスフォーマ130とを備え、入力側トランスフォーマ120が有する金属配線と出力側トランスフォーマ130が有する金属配線とは、互いに異なる金属配線層を用いて構成され、かつ、平面視した場合に交差している。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

配線層の形成方法及び半導体装置の製造方法

【課題】配線層の表面の平坦度を高めることができ且つ配線間隔が広い領域において磁界を変動させる構成を無くした配線層の形成方法及び半導体装置の製造方法を提供する。

【解決手段】配線層の形成方法は、下側部材上に配線パターン102を形成する工程と、その上に絶縁材料層103,106を形成する工程と、配線パターンの間に形成された絶縁材料層の一部を、絶縁膜ブロック111として残すと共に、絶縁膜ブロック111の高さを、絶縁膜ブロック以外の絶縁材料層の高さより高くなるように、絶縁材料層をエッチング処理する工程と、絶縁膜ブロックを含む絶縁材料層を研磨して、表面が平坦化された層間膜を形成する工程とを有する。半導体装置の製造方法は、半導体基板と配線層とを有し、上記配線層の形成方法を用いて配線層の少なくとも1つを製造する。

(もっと読む)

コア付きインダクタ素子およびその製造方法

【課題】半導体基板上に形成するインダクタのインダクタンスを大きくすること。

【解決手段】半導体基板上に形成された少なくとも1層からなるコイル配線のコイル中央孔に別基板に形成されたコアを挿入する。コアをコイル中央孔に固定した後、別基板は分離する。コアは別基板に接合材を介してコア材(磁性体)の薄板を付着させて、パターニングする。半導体基板上に形成されたコイル中央孔は流動性接着剤が入っていて、コアを挿入した後に流動性接着剤が硬化してコアが固定される。コアが固定された後に接合剤の接着力を低下させて別基板を分離する。コア材はバルクと同じ高透磁率を有するので、非常に大きなインダクタンスを持つインダクタを形成できる。

(もっと読む)

浅いトレンチ分離および基板貫通ビアの集積回路設計への統合

【課題】浅いトレンチ分離および基板貫通ビアの集積回路設計への統合を提供すること。

【解決手段】ICを製造する方法は、第1の側、および第2の対向する側を有する基板を用意すること、基板の第1の側にSTI開口を形成すること、および基板の第1の側に部分的TSV開口を形成すること、および部分的TSV開口を延長することを含む。延長された部分的TSV開口は、STI開口より基板内への深さが深い。方法はまた、STI開口を第1の固体材料で充填すること、および延長された部分的TSV開口を第2の固体材料で充填することを含む。STI開口、部分的TSV開口、または延長された部分的TSV開口のいずれも、基板の第2の側の外面を貫通しない。少なくとも、STI開口および部分的TSV開口は同時に形成され、またはSTI開口および延長された部分的TSV開口は同時に充填される。

(もっと読む)

半導体装置及び電源装置

【課題】半導体装置において、抵抗が増大して変換効率が低下してしまうのを防止する。

【解決手段】半導体装置を、基板2上に形成されたGaN系半導体積層構造3を有する第1トランジスタQ1と、GaN系半導体積層構造を有する第2トランジスタQ2とを備え、第1トランジスタが、複数の第1フィンガ8AXを有する第1ゲート電極8Aと、複数の第1ドレイン電極9Aと、複数の第1ソース電極10Aとを備え、第2トランジスタが、複数の第2フィンガ8BXを有する第2ゲート電極8Bと、複数の第2ドレイン電極9Bと、複数の第2ソース電極10Bとを備え、複数の第1ドレイン電極の上方又は下方に接続されたドレインパッド15と、複数の第2ソース電極の上方又は下方に接続されたソースパッド25と、複数の第1ソース電極及び複数の第2ドレイン電極に接続された共通パッド35とを備えるものとする。

(もっと読む)

半導体装置、電子装置、及び半導体装置の製造方法

【課題】第1インダクタと第2インダクタを構成する金属材料のマイグレーションに起因して第1インダクタと第2インダクタの絶縁が確保できなくなることを、抑制する。

【解決手段】半導体チップ100は配線基板200の第1面上に実装されており、多層配線層を有している。第1インダクタ112は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は多層配線層に形成されており、巻き軸方向が配線基板200と水平方向を向いている。第2インダクタ122は第1インダクタ112に対向している。封止樹脂400は、配線基板200の少なくとも第1面と、半導体チップ100とを封止している。溝500は、封止樹脂400と多層配線層の界面のうち、少なくとも第1インダクタ112と第2インダクタ122の間に位置している部分の全域に形成されている。

(もっと読む)

ヒータ配線付き半導体チップ

【課題】半導体チップの高信頼実装技術を提供。

【解決手段】半導体チップ4は、基板100と、前記基板の一方の面に形成されたデバイス層80と、電磁波の輻射により発熱するヒータ配線302と、前記デバイス層と電気的に接続される電極103とを備えることを特徴とする。半導体チップ4を実装基板に実装する際には、ヒータとしての金属配線膜302を発熱させることにより、固着材料を溶かして半導体チップを実装基板と接続させる。

(もっと読む)

半導体装置及び製造方法

【課題】少ない層間接続プロセス工程数で、コンタクト部分の面積を小さくすることのできる半導体装置及び製造方法を提供する。

【解決手段】多層導体配線10は、スルーホール15は、導体13の一部は、ひさし部13Cとしてスルーホール15の内側に露出する。そして、スルーホール15のスルーホール用孔の内側に埋め込まれた埋め込み金属16とひさし部13Cとで、側面コンタクト構造を形成することができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ビア深さのバラツキを抑制することができる半導体装置の構造およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に、SiおよびCを含むキャップ絶縁膜を形成する工程と、キャップ絶縁膜上に、キャップ絶縁膜と比較して、シリコン原子数に対する炭素原子数の組成比が高い、有機シリカ膜を形成する工程と、不活性ガス、Nを含むガス、フッ化炭素ガスおよび酸化剤ガスを含む混合ガスを用いたプラズマ処理により、有機シリカ膜に、異なる開口径を有する2以上の凹部を形成する工程と、を含む。

(もっと読む)

1 - 20 / 204

[ Back to top ]