Fターム[5F033VV12]の内容

半導体集積回路装置の内部配線 (234,551) | 配線の用途 (10,506) | 検査、試験 (365)

Fターム[5F033VV12]に分類される特許

1 - 20 / 365

半導体チップ及びその抵抗測定方法、並びに半導体装置

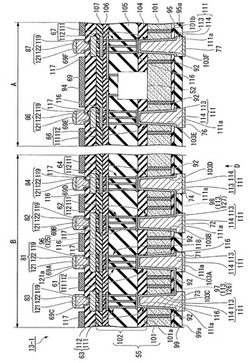

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

半導体装置

【課題】

実施形態は、解析が簡便な半導体装置を提供する。

【解決手段】

本実施形態の半導体装置は、内部信号を伝送可能な第1配線101と、第1配線101

と電気的に接続された測定電極100と、測定電極100と隣接するように配置され、内

部信号を計測するときに接地電位VSSが印加され、内部信号を計測する以外のときに所

望の電圧が印加されたダミー電極102,103とを備える。

例えば、測定電極100は、環状に形成されており、ダミー電極は、第1電極102と

第2電極103とを有し、第1電極102は、測定電極100の内側に形成された空間に

隣接するように配置され、第2電極103は、測定電極100の外側に隣接するように配

置される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】シールリングの内側領域生じたクラックを低コストで検出することができる半導体装置を提供する。

【解決手段】図2に示すように、本実施形態に係る半導体装置は、多層配線層と、内部回路領域3と、多層配線層に形成され、内部回路領域3を囲うシールリング220と、平面視で内部回路領域3とシールリング220とに挟まれた領域に設けられているTEG200と、を含んでいる。TEG200は、多層配線層の少なくとも2層それぞれに設けられ、互いに接続する導体パターン7と、P型ウェル13と、N型ウェル14とによって構成されている。P型ウェル13とN型ウェル14は、平面視で交互に互いに接続された状態で配置されており、P型ウェル13とN型ウェル14のいずれか一つに導体パターン7が接続されている。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

半導体装置

【課題】半導体装置の最上層の保護膜のクラックを防いで、半導体装置の信頼性の向上を図ることのできる技術を提供する。

【解決手段】ボンディングパッドBP1を長方形状とし、ボンディングパッドBP1のワイヤボンディング領域BP1wでの保護膜5の重なり幅を、ボンディングパッドBP1のプローブ領域BP1pでの保護膜5の重なり幅よりも広くなるように、ボンディングパッドBP1上の保護膜5に開口部6を形成する。

(もっと読む)

貫通配線の検査方法、貫通配線基板の製造方法

【課題】1つの貫通配線のみの抵抗を測定できる貫通配線の検査方法、及び該貫通配線の検査方法を行う工程を含む貫通配線基板の製造方法の提供。

【解決手段】基板1の一方の面1aに配された導電部2と、基板1を貫通し、導電部2と接続される第一貫通配線3、第二貫通配線4および第三貫通配線5とを少なくとも備えた貫通配線基板10を用い、基板1の他方の面1b側から第一貫通配線3及び第二貫通配線4に、定電流源6の一組の端子6a,6bを電気的に接続して、第一貫通配線3、導電部2、第二貫通配線4の経路に電流を流すと同時に、基板1の他方の面1b側から第一貫通配線3及び第三貫通配線5に、電圧計7の一組の端子7a,7bを電気的に接続して、第一貫通配線3における電圧降下を測定することを特徴とする貫通配線の検査方法。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】溝配線に生じるディッシングやエロージョンが配線構造に及ぼす影響を簡便に評価できるような半導体装置を提供する。

【解決手段】TEG200は、多層配線層中に設けられている。また、多層配線層中の第1絶縁膜に埋め込まれた下層溝配線1を備えている。TEG200は、第1絶縁膜80(図示せず)の表層に埋め込まれた下層導体パターン1と、第1絶縁膜80上及び下層導体パターン1上に形成された第2絶縁膜20と、それぞれが同一の下層導体パターン1に対向する複数の上層導体パターン10と、を有している。なお、上層導体パターン10は、第2絶縁膜20の表層に埋め込まれていても良いし、第2絶縁膜20上に形成されていても良い。

(もっと読む)

半導体装置

【課題】フリップチップ実装に用いられる半導体チップと実装基板との電気的な接続信頼性を向上させた半導体装置を提供する。

【解決手段】半導体チップ2と、半導体チップ2の主面に配置された複数の電極パッドと、複数の電極パッドの上に配置された複数のバンプ5とを有し、半導体チップ2のコーナー部において、第1のバンプと第2のバンプとが、第1のピッチで、隣接して配置され、半導体チップの中心部において、第3のバンプと第4のバンプとが、第2のピッチで、隣接して配置され、第1のピッチは、第2のピッチよりも狭い。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体チップ及びその製造方法、並びに半導体パッケージ

【課題】再配線形成前のウエハテストを適切に実施する。

【解決手段】半導体チップ1は、周辺電極パッド30内又はV/G配線20において周辺電極パッド30に相対的に近い位置にある第1の再配線接続部61と、V/G配線20において周辺電極パッド30から相対的に遠い位置にあり、再配線60の形成前における電位が第1の再配線接続部61よりも小さい第2の再配線接続部62とが、再配線60により接続されたものである。半導体チップ1は、第2の再配線接続部62、V/G配線20上の第2の再配線接続部62の近傍で再配線60の形成前における電位が第1の再配線接続部61よりも小さい部分、又は、V/G配線20から第2の再配線接続部62の近傍に引き出され、再配線60の形成前における電位が第1の再配線接続部61よりも小さい導電部に、ウエハテスト用の検査部80を備えている。

(もっと読む)

半導体装置

【課題】複数の半導体チップが積層された構造を有する半導体装置において、パンプ電極BP_0に接触せずに、かつ、貫通電極TSV_0の負荷容量を増やさずにテストできる半導体装置10を提供する。

【解決手段】積層された複数の半導体チップ21〜24のそれぞれが、バンプ電極BP_0と、テストパッドPAD_0と、テストパッドから供給される信号を受け取りバンプ電極に供給するテストバッファTD_0と、テストバッファの活性状態と非活性状態とを制御する制御信号を供給するバッファ制御部BCとを含む。

(もっと読む)

TEG構造、及び層間剥離箇所探索方法

【課題】配線層とビア層との剥離箇所を簡単に特定できる技術を提供する。

【解決手段】第1層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、第2層配線層のパターンの導体部は、所定の方向Xに沿って、複数本、点線状に設けられた導体部と、前記方向Xに交差する所定の方向Yに沿って、複数本、点線状に設けられた導体部とを具備し、前記方向X(方向Y)に沿って設けられた第1層配線層と第2層配線層とは、平面視において、互いに、食い違うように、かつ、全体で、一つの連続した線が描かれるように設けられてなり、第1層配線層と第2層配線層とは、両方向ともに平面視において共通する或る位置において、電気的に接続し一つのラインに沿った一つの導通ラインが構成されている。

(もっと読む)

超音波スキャンに基づくシリコン貫通配線(TSV)におけるボイドの存在の推定

【課題】 3次元集積化構造中の不良を超音波スキャンによって検出することであって、シリコンウエハなどのボードに配列されているシリコン貫通配線(TSV)においてプロセス中に発生してしまう可能性のあるボイドの存在を非破壊的に検出すること。

【解決手段】 ボード面にわたって超音波スキャンをすると、(はんだ)バンプ等が物理的な遮蔽物として超音波を散乱させてしまい、超音波スキャンによる測定を妨げてしまう。そこで、これら複数のTSVの中から、テスト要素グループ(TEG)に属する単数または複数のTSVを選び出すにあたって、物理的な遮蔽物を少なく存在するように選び出す。

(もっと読む)

1 - 20 / 365

[ Back to top ]