Fターム[5F033WW08]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 電圧、電流 (63)

Fターム[5F033WW08]に分類される特許

1 - 20 / 63

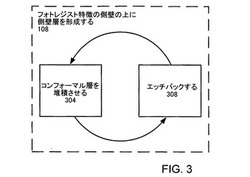

ラインエッジ粗さを低減させた特徴のエッチング

【課題】ラインエッジ粗さを低減させて特徴をエッチングする

【解決手段】ラインエッジ粗さを低減させて層内に特徴を形成するための方法が提供される。層の上に、フォトレジスト層が形成される。フォトレジスト層は、フォトレジスト側壁をともなうフォトレジスト特徴を形成するために、パターン形成される。複数のサイクルを実施することによって、フォトレジスト特徴の側壁の上に、厚さ100nm未満の側壁層が形成される。各サイクルは、単分子層から20nmまでの厚さを有する層をフォトレジスト層上に堆積させることを含む。フォトレジスト特徴を通して、層内に特徴がエッチングされる。フォトレジスト層および側壁層は、剥ぎ取られる。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置の製造方法

【課題】コンタクトホール内に良好にAl膜が埋設されたコンタクトプラグを有する半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板の層間絶縁膜内にコンタクトホールを形成する工程と、基板を加熱した状態でコンタクトプラグを形成する工程を有する。コンタクトプラグを形成する工程では、スパッタ装置のチャンバー内のステージ上に、チャックを介して基板を保持し、チャックに印加するESC電圧を第一の電圧、第二の電圧、第三の電圧と、この順に3段階のステップ状に増加させる。チャンバー内のターゲットに対して第一のターゲット電力を印加してコンタクトホール内に第一のAl膜を成膜する。次に、チャンバー内のターゲットに対して第一のターゲット電力よりも高い第二のターゲット電力を印加して第一のAl膜上に第二のAl膜を成膜する。

(もっと読む)

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

固定された導電性ビアおよびその製造方法

【課題】導電性ビアおよびそれを形成する方法に関する。

【解決手段】導電性ビアが、導電性接触構造と該導電性接触構造上に配置された誘電体層の突出部との間に配置された部分を含む。1つの実施形態において、突出部は、導電性接触構造上にアンダーカット層を形成し、次に、該導電性接触構造およびアンダーカット層上に誘電体層を形成することによって形成される。誘電体層に空洞を形成し、誘電体層の突出部を形成するようにアンダーカット層の材料が該空洞を通して除去される。導電性ビアの導電性材料は次に、突出部の下および空洞に形成される。

(もっと読む)

半導体装置の製造方法

【課題】めっき膜厚の制御を精度よく行う。

【解決手段】半導体基板上に形成された絶縁膜に設けられた複数の凹部をめっき処理により導電性材料で埋め込むめっき工程を含む半導体装置の製造方法において、めっき工程は、複数の凹部のうち所定幅以下の微細な凹部が導電性材料で埋め込まれる際に、所定の第1の基準電流密度を半導体基板全面における各複数の凹部の側壁の面積を含む第1の表面積S1と各複数の凹部の側壁の面積を含まない第2の表面積S2との表面積比Sr=S1/S2に基づき補正した第1の電流密度でめっき処理を行う工程(S104)を含む。

(もっと読む)

残存フォトレジスト及び残留側壁パッシベーションを除去する、その場でのポストエッチング工程

【課題】金属エッチングと、残存フォトレジスト及び残留側壁パッシベーションの剥離のための改良された技術を提供する。

【解決手段】単一のエッチングチャンバ内で、金属エッチングと、エッチングマスク剥離と、残留側壁パッシベーションの除去とを実行する方法。ウエハは、エッチングチャンバ内に配置される。ウエハ上で、金属エッチングが実行される。酸素とアルゴンとの混合物等の剥離ガスが、エッチングチャンバに提供され、酸素プラズマを形成するために励起される。酸素プラズマは、エッチングマスクをウエハから剥離させ、残留側壁パッシベーションを除去する。酸素プラズマは、更に、エッチングチャンバをクリーニングする。

(もっと読む)

高耐圧配線、配線設計装置および方法

【課題】層間絶縁膜を厚くすることなく、放電耐圧を向上させ、デバイスの特性の安定化や性能の向上を図る。

【解決手段】高耐圧配線は、Si基板101上に形成された配線層103と、絶縁膜104と、上層配線105,106と、絶縁膜104に形成された溝107とを有する。配線層103上の絶縁膜104の厚さTは、上層配線105と106間の距離dよりも小さく、溝の幅Wは、距離dよりも小さい。絶縁膜104の厚さTは、配線層103と上層配線105,106との間に与えられる最大の電位差Vmaxよりも絶縁膜104の耐圧が大きくなるように設定され、絶縁膜104の露出量Xは、溝の幅Wと距離dとが等しいときの絶縁膜104に沿った沿面放電開始電圧をV0(V0=b×lnT+c、b,cは定数)としたとき、Vmax<aX+V0(aは定数)となるように設定される。

(もっと読む)

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

電子部品素子

【課題】金属膜の酸化を防止し、さらに金属膜の酸化を防止するだけでなく、酸化防止を行うことで新たに発生した不具合(腐食)も防止する。

【解決手段】

電子部品素子1では、基板2上に少なくとも3層からなる金属膜群5が形成されている。この金属膜群5は、少なくとも、金属膜51と、金属膜51を保護する保護膜52と、金属膜51と保護膜52との電位差を無くす調整膜53とから構成されている。この電子部品素子1では、基板2上に、金属膜51、調整膜53、および保護膜52の順に積層されている。

(もっと読む)

集積回路のための電気的に切断される金属ヒューズの構造体及びその形成方法

【課題】 プログラミングを達成するために、過剰な電圧及び電流を用いることなく、電気的に切断される金属ヒューズ構造体を提供する。

【解決手段】 集積回路デバイスのためのヒューズ構造体が、絶縁層内に定められた細長い金属相互接続層(106)と、金属相互接続層の上面の一部分上にのみ形成された金属キャップ層(108)と、金属キャップ層(108)及び金属キャップ層(108)が上に形成されていない金属相互接続層の残りの部分の両方の上に形成された誘電体キャップ層(112)とを含み、金属キャップ層(108)が上に形成されていない金属相互接続層の残りの部分は、エレクトロマイグレーション損傷メカニズムを受けやすく、細長い金属相互接続層(106)を通して電流を流すことによって、ヒューズ構造体のプログラミングが容易になる。

(もっと読む)

MOS型半導体装置

【目的】耐放射線特性の改善と高耐圧化が図れるMOS型半導体装置を提供する。

【解決手段】LOCOS膜18上に窒化膜18を形成し、窒化膜14上にPBSG膜10を形成する。窒化膜14の屈折率を2.0〜2.1とし、膜厚を0.1μm〜0.5μmとすることで半絶縁性薄膜にする。γ線でLOCOS膜18内に発生した電子―正孔対のうち移動度が小さい正孔31を窒化膜14を通してソース電極12に逃がし、LOCOS膜18にできる正の固定電荷33の蓄積量を抑制する。このように3層構造とすることで耐放射線特性の改善と高耐圧化が図れる。

(もっと読む)

アモルファススピンオングラス膜の形成方法

【課題】基板の温度を低温に保ってSOG膜をキュア処理することができ、かつキュア処理時の膜のクラックの発生を低減させることが可能なSOG膜の形成方法を提供する。

【解決手段】シリコン及び/又はシリコン化合物と有機溶媒を含有するスピンオングラス材料を基板に塗布した後に、酸素を主成分とするガスにより形成されたプラズマ中で結晶化が生じない条件下で、前記スピンオングラス材料塗膜を高密度化することによりアモルファススピンオングラス膜を形成する。

(もっと読む)

スルーシリコンビア(TSV)内にチップ−チップ間、チップ−ウェハー間及びウェハー−ウェハー間の銅インターコネクトを電着するプロセス

シリコン基板内のビア内に高純度の銅を電着し、スルーシリコンビア(TSV)を形成するプロセスである。本プロセスは、電解銅めっきシステム内の電解槽内にシリコン基板を浸漬するステップと、高純度の銅を電着してTSVを形成するのに十分な時間の間、電圧を印加するステップとを含み、電解槽が酸、銅イオンの発生源、第一鉄イオン及び/又は第二鉄イオンの発生源、及び析出した銅の物理−機械的特性を制御するための少なくとも1つの添加剤とを含み、銅金属の発生源からの銅イオンを溶解することによって電着されることになる付加的な銅イオンを提供するために、前記槽内でFe2+/Fe3+レドックス系が、確立される。 (もっと読む)

高圧ベベルエッチング処理

半導体基板が半導体基板支持部上に支持されたベベルエッチング装置内において、プラズマによる半導体基板のベベルエッジエッチングを行う際にアーク放電を防止する方法は、3〜100Torrの圧力までベベルエッチング装置を排気した状態で、ウェーハにおいて見られるRF電圧を、アーク放電が回避される十分に低い値に維持しつつ、ベベルエッチング装置においてプラズマによる半導体基板のベベルエッジエッチングを行うステップを備える。 (もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

基板処理装置および基板処理方法

【課題】多種多様な基板に対して適切なドーズ量で、しかも均一に電子ビームを照射して短時間で良好な基板処理を行うことができる基板処理装置および基板処理方法を提供する。

【解決手段】電子ビーム発生ユニット40A,40Bの出射窓40gから電子ビームEBがスキャン方向(第1方向)Yに走査されながら基板表面に照射されるとともに、当該基板Wが水平移動方向(第2方向)Xに移動して基板表面Wfに対して電子ビームEBが2次元的に照射される。ここで、出射窓40gと基板Wとの距離Dについては、基板Wに対応した値に調整される。また、基板Wの移動速度、電子銃40bに与える電流および電子銃40bに与える加速電圧についても、基板Wに応じた値に調整される。このように距離D、移動速度および電流値が基板Wに対応して調整された状態で電子ビーム照射が基板W上の層間絶縁膜Fに対して行われる。

(もっと読む)

集積回路デバイスのヒューズ構造

【課題】 集積回路デバイスのヒューズ構造を提供する。

【解決手段】 本発明のヒューズ構造は、半導体基板の一部の上に配置された金属含有導電性材料のストリップを含み、ストリップは、第1方向に沿って延伸し、均一な線幅を有する。誘電体層は、導電層を覆う。誘電体層内は、第1ビアと第2ビアを有し、第1インターコネクトと第2インターコネクトをそれぞれ含む。第1インターコネクトは、ストリップ上の第1位置と物理的且つ電気的に接触しており、第2インターコネクトは、ストリップ上の第2位置と物理的且つ電気的に接触している。導電ストリップ上の第1と第2位置は、シリコンを含まない。誘電体層の上方は、第1インターコネクトに電気的に接続された第1配線構造と、第2インターコネクトに電気的に接続された第2配線構造である。

(もっと読む)

半導体加工方法

【課題】high−k膜/メタルゲート構造を有する半導体素子のドライエッチングにおいて、メタルゲート部分を垂直にエッチングする。

【解決手段】減圧処理室204と、該減圧処理室に処理ガスを供給するガス供給手段と、前記減圧処理室内に、半導体基板を載置して保持する試料台205と、前記減圧処理室に供給された処理ガスに高周波エネルギを供給してプラズマを生成するプラズマ生成手段を備え、生成したプラズマにより前記半導体基板にプラズマエッチング処理を施す半導体加工方法において、前記試料台上に、HfあるいはZrを含む高誘電率絶縁膜、TiあるいはTaを含む仕事関数制御金属導体膜、およびレジストを順次形成した半導体基板206を載置し、前記レジストを用いて前記導体膜をエッチング加工するに際して、前記試料台にオンオフ変調された基板バイアス電圧を印加する。

(もっと読む)

1 - 20 / 63

[ Back to top ]