Fターム[5F033XX00]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696)

Fターム[5F033XX00]の下位に属するFターム

平坦化 (793)

段差被覆性改善、段切れ防止 (570)

微細化 (1,181)

エレクトロマイグレーション防止 (477)

ストレスマイグレーション防止 (204)

オーミック性向上 (46)

低抵抗化 (1,713)

低融点化 (3)

密着性改善 (1,147)

エッチングマスクのずれ対策 (331)

ヒロック防止 (130)

クラック防止、歪み防止 (509)

腐食防止 (505)

応力の利用、応力の低減 (758)

酸化防止 (315)

残さの除去 (252)

放熱 (140)

基板と配線又は配線間の干渉防止 (1,198)

信号の遅延防止、伝達の同時化 (255)

拡散、突き抜け防止 (992)

短絡防止 (613)

遮光 (95)

製造工程の簡略化 (781)

製造コストの低下 (762)

成膜時の膜厚の制御 (46)

配線修理 (121)

検査、試験 (367)

Fターム[5F033XX00]に分類される特許

1 - 20 / 1,392

半導体装置の製造方法及び半導体装置

Cu層形成方法及び半導体装置の製造方法

リフロー法及び半導体装置の製造方法

半導体装置

半導体装置およびその製造方法

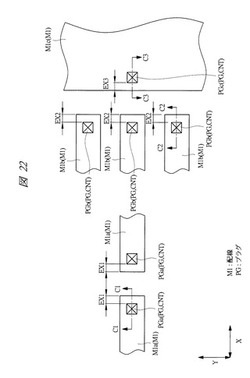

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

半導体製造装置及び半導体製造方法

【課題】エッチング工程を行う際の窒化膜のエッチング選択比を向上できる半導体製造装置及び方法が提供される。

【解決手段】本発明による半導体製造装置は工程チャンバーの外部で供給されるジフルオロメタンCH2F2、窒素N2、及び酸素O2ガスからプラズマを発生させ、発生されたプラズマを工程チャンバー内へ供給する。プラズマが工程チャンバーへ供給される途中に三フッ化窒素NF3が供給される。このような装置構造及びソースガスを利用してシリコン窒化膜をエッチングすると、他の種類の膜に対するシリコン窒化膜のエッチング選択比を大きく増加させることができる。

(もっと読む)

半導体装置

【課題】基板電位を安定化させることができる半導体装置を提供する。

【解決手段】半導体装置に含まれるFET素子1は、N角形をなす外周端部30pと貫通孔を形作る内周端部30iとを有する環状のゲート電極30を備える。またFET素子1は、貫通孔の直下方に形成された内側不純物拡散領域21と、ゲート電極30のN角形の辺の外側に形成された外側不純物拡散領域22A〜22Dと、ゲート電極30の頂点の外側に形成されたバックゲート領域23A〜23Dとを備える。バックゲート領域23A〜23Dは、ゲート電極30のN角形の辺のうちゲート電極30の頂点をなす2辺の延長線Ex,Eyの少なくとも一方を跨るように形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線倒れを防止することが可能な半導体装置の製造方法を提供する。

【解決手段】一の実施形態による半導体装置の製造方法では、半導体基板上に、第1の絶縁膜、第2の絶縁膜、および犠牲膜を順に形成し、前記犠牲膜と前記第2の絶縁膜から複数の芯材を形成する。さらに、前記方法では、各々の前記芯材の側面に、前記芯材に接する第1側面と、前記第1側面の反対側に位置する第2側面とを有する第1配線と、前記芯材に接する第3側面と、前記第3側面の反対側に位置する第4側面とを有する第2配線を形成する。さらに、前記方法では、前記第1および第2配線の形成後に、前記第2の絶縁膜が残存するように前記犠牲膜を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】工程数を増加させることなく、エアギャップを有する半導体装置の機械的強度を向上する。

【解決手段】半導体装置に必要な導電材料、例えばビアアレイの外郭のビアを接続して環状ビア1Rとして絶縁膜2を囲み、エアギャップ形成時に導電材料に囲まれた絶縁膜2は残り非エアギャップ領域4となり、その他の部分は絶縁膜2が除去されてエアギャップ領域3となる。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体装置、及びその製造方法

【課題】TSV付き半導体装置において、貫通孔側面すべてにバリア及びシード層を成膜しないことで、空隙の発生を防止する。

【解決手段】

第1の溝部、及び前記第1の溝部より水平断面積が小さい第2の溝部からなる凸状溝部を画成し、且つ、前記第1及び第2の溝部により両端を開口する貫通ビアホールが形成される半導体基板と、前記第1の溝部の内面から、前記第2の溝部の側面の一部まで被覆して、前記貫通ビアホールの側面に隆起するバリア層およびシード層と、前記シード層の表面上、及び、前記シード層で被覆されていない前記第2の溝部内部に形成されて、前記半導体基板の両表面から露出する電極と、を備える半導体装置が提供される。

(もっと読む)

半導体装置の製造方法

【課題】膜パターンの倒れを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態の半導体装置の製造方法は、基板上に低ガラス転移温度材料膜と高ガラス転移温度材料膜との積層膜を形成する工程と、前記積層膜上に加熱下で上層膜を形成する工程と、前記上層膜をパターニングする工程と、前記上層膜をマスクとして前記積層膜をパターニングする工程と、前記上層膜をウェットエッチング処理により除去する工程と、を備えた。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

ウェーハ薄膜加工制御方法

【課題】ウェーハ内部のビア底部からウェーハ研削面までの残存寸法に基づいて薄膜化加工を行うウェーハ薄膜加工制御方法を提供する。

【解決手段】ウェーハに予め貫通電極用のビアを形成後、ウェーハの研削面を上にして加工装置のチャックテーブル上にウェーハを保持し、ウェーハの研削面にグラインディングホイールを押し当てて研削加工を行う。この研削加工では、NCIGにより、ウェーハ全体の膜厚を測定して膜厚データを取得すると共に、ビア底部からウェーハ研削面までの寸法を測定して残存寸法データを取得する。仕上げ研削加工時において、ビア底部からウェーハ研削面までの残存寸法データを、ウェーハ全体の膜厚データを参照して導出することで、ビアの底部直前まで研削加工を行うことができる。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

パターン構造体の製造方法

【課題】基材上にパターンを低温かつ低コストで形成することができると共に、リフトオフを容易にできるパターン構造体の製造方法を提供する。

【解決手段】実施形態に係るパターン構造体の製造方法では、基材10上に、インクジェット法によりリフトオフ材12を形成する。次に、基材10及びリフトオフ材12上に、原子層堆積法により機能膜14を形成する。次に、リフトオフ法によりリフトオフ材12を除去することによって、基材10上に、機能膜14からパターン14aを形成する。リフトオフ材12は、樹脂と溶媒とを含むインクを基材10上に塗布した後、溶媒を除去することによって形成される。溶媒は、樹脂に対する第1溶解性を有する第1溶媒と、第1溶解性よりも低い第2溶解性を有する第2溶媒とを含む。第1溶媒は第2溶媒に相溶する。

(もっと読む)

1 - 20 / 1,392

[ Back to top ]