Fターム[5F033XX32]の内容

半導体集積回路装置の内部配線 (234,551) | 目的、効果 (15,696) | 遮光 (95)

Fターム[5F033XX32]に分類される特許

1 - 20 / 95

感光性樹脂組成物、感光性フィルム及び電子部品

【課題】赤外線の吸収が可能であり、厚膜においてもパターン形成することが可能であり、低温硬化が可能である感光性樹脂組成物、フィルム及び電子部品を提供する。

【解決手段】(A)少なくとも1つのエチレン性不飽和基を有する光重合性化合物、(B)光重合開始剤、及び(C)カーボンフィラーを含む感光性樹脂組成物であって、前記(A)少なくとも1つのエチレン性不飽和基を有する光重合性化合物が、アクリレート化合物及び/又はメタクリレート化合物を含む感光性樹脂組成物。この感光性樹脂組成物をフィルム状に成形してなる感光性フィルム。絶縁膜と、前記絶縁膜の内部に配設された配線とを有した配線層を含む電子部材であって、前記絶縁膜の少なくとも一部が上記の感光性樹脂組成物又は感光性フィルムを用いて形成されたものである電子部品。

(もっと読む)

固体撮像装置、固体撮像装置の製造方法、および電子機器

【課題】裏面照射型の固体撮像装置において、受光面と遮光膜との距離を小さくすることにより、光電変換部での受光特性の向上を図る。

【解決手段】光電変換部が配列形成された画素領域を有するセンサ基板と、センサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、画素領域における受光面上に設けられた遮光膜と、遮光膜を覆って設けられた保護絶縁膜と、画素領域の外側の周辺領域において、保護絶縁膜からセンサ基板にかけて埋め込まれ駆動回路に接続された複数の貫通ビアを備えた固体撮像装置。

(もっと読む)

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

ボンディングパッドを有する半導体デバイス及びその製造方法

【課題】 ボンディングパッドを有する半導体デバイス及びその製造方法を提供する。

【解決手段】 表面側及び裏面側を有するデバイス基板、前記デバイス基板の前記表面側に配置され、n層数の金属層を有する相互接続構造、及び前記相互接続構造を通過して延伸し、前記n層数の金属層の前記第n番目の金属層に直接接触するボンディングパッドを含む半導体デバイス。半導体デバイスは、前記デバイス基板の前記裏面側に配置された遮蔽構造、及び、前記デバイス基板の前記表面側に配置され、前記デバイス基板の前記裏面側から前記放射線検出領域に向けて投射された放射線を検出することができる放射線検出領域をさらに備える。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体基体同士が張り合わされた構成を有する半導体装において、接合精度の向上を可能とする。

【解決手段】第1半導体基体31と、第2半導体基体45とを備え、第1半導体基体31の第1主面31A側と、第2半導体基体45の第1主面45A側が接合されている。そして、第1半導体基体31の第1主面31A側、第2半導体基体45の第1主面45A側、第1半導体基体31の第2主面31B側、及び、第2半導体基体45の第2主面45B側から選ばれる少なくとも1つ以上に形成されている反り補正層13,14を備える半導体装置79を構成する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

光電変換装置およびその製造方法

【課題】 配線材料の層間絶縁膜への拡散を抑制する拡散抑制膜による多層配線構造を設けた光電変換装置において、工程を増加させることなく、受光効率を高める。

【解決手段】 本発明は、半導体基板に配された光電変換素子と、前記半導体基板上に層間絶縁膜を介して複数の配線層が配された多層配線構造を有する光電変換装置であって、最上配線層の上部に、前記最上配線層を構成する材料の拡散を抑制する拡散抑制膜が配され、前記拡散抑制膜は、前記最上配線層及び前記層間絶縁膜の前記光電変換素子に対応する領域を覆って配されており、前記拡散抑制膜の前記光電変換素子に対応する領域にレンズが配されていることを特徴とする。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

反射型液晶表示装置及びその製造方法

【課題】反射型液晶表示装置において、回路素子へ到達する入射光の量を低減するための技術を提供する。

【解決手段】回路素子に電気的に接続された、第1金属層112の上に、開口部127及び第1スルーホール126を有するようにパターニングされた第1絶縁層113を形成し、第1絶縁層に、開口部127に埋め込まれた金属部114及び第1スルーホール126に埋め込まれた第1プラグ115を形成した後、第2絶縁層116を形成する。第2絶縁層116の上に、開口部を有するようにパターニングされた第2金属層117を形成し、第2金属層の上に第3絶縁層119を形成した後、第2金属層117の開口部を通り且つ第1プラグ115の上面を露出させる第2スルーホール120を、第2絶縁層116及び第3絶縁層119に形成し、第2スルーホール120に埋め込まれた第2プラグ121と、第2プラグに接続された反射電極122とを形成する。

(もっと読む)

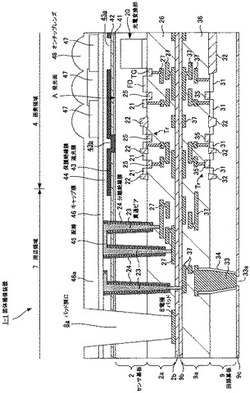

固体撮像装置

【課題】 新たな工程を追加することなく、遮光膜の面積占有率の差を軽減して平坦化膜の均一性を改善することができる固体撮像装置を提供する。

【解決手段】 半導体基板に形成されたフォトダイオードを有する複数の画素が配置された有効画素部と、前記有効画素部の周辺部とを含む固体撮像装置で、前記半導体基板の上方に配置された複数の金属配線層と、前記複数の金属配線層のうち最上に配されたパターニングされた金属配線層を覆う平坦化膜とを備え、前記有効画素部では、前記複数の金属配線層は前記フォトダイオードに光を入射させるための開口部を有し、前記周辺部では、前記複数の金属配線層の最上層に開口部が設けられ、前記最上層と前記半導体基板との間の少なくとも1つの金属配線層が前記最上層の開口部を通して入射する光を遮るパターンを有する。

(もっと読む)

結晶化シリコン層の製造方法、半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置

【課題】金属原子が内部に拡散、侵入せず、かつ、結晶化方位や粒径を制御することのできる結晶化シリコン層の製造方法、かかる方法を利用した半導体装置の製造方法、電気光学装置の製造方法、半導体装置、電気光学装置および投射型表示装置を提供すること。

【解決手段】結晶化シリコン層を形成するにあたって、基板本体10d上に金属触媒層8および第1非結晶シリコン層4xを形成した後、熱処理を行ない、第1非結晶シリコン層4xと金属触媒層8との間での相互拡散により、第1非結晶シリコン層4xと金属触媒層8とを入れ替える。その際、第1非結晶シリコン層4xは、多結晶シリコン層4yに変化する。金属触媒層8を除去した後、開口部15aを備えた絶縁層15、および第2非結晶シリコン層1xを形成した状態で熱処理を行ない、第2非結晶シリコン層1xを、開口部15aの底部で多結晶シリコン層4yと接している部分を起点にして結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】複数の顧客による各々異なるLSIが共同で作製された基板を、守秘性が得られた状態で各々の顧客に提供できるようにする。

【解決手段】特定の顧客への提供対象とするLSIチップ領域331以外の領域が開放した開口部307aを備えるマスクパターン307を形成する。次に、マスクパターン307をマスクとし、開口部307に露出しているLSIチップ領域332をエッチング除去し、ブラインド領域301aを形成する。ブラインド領域301aの形成では、第1配線層302,第2配線層303,および第3配線層304を除去し、これらの下層の一部までを除去する。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、及び電子機器

【課題】積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。また、固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】第1の半導体ウェハ31と、第2の半導体ウェハ45とを、基板間配線68で接続する構成とする。基板間配線は、第1の半導体ウェハ31表面の第1の多層配線層に形成される接続孔66と、第2の半導体ウェハ45表面の第2の多層配線層に形成された貫通接続孔65とに、導電材料が埋め込まれて形成されている。そして、貫通接続孔65は接続孔66の直径よりも大きく形成されている。これにより、貫通接続孔65の構内に導電材料を埋め込む際のボイドの発生を防ぐ。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】寄生容量を低減し、高性能化を図った固体撮像装置等の半導体装置とその製造方法、前記固体撮像装置を備えたカメラ等の電子機器を提供するものである。

【解決手段】本発明の半導体装置は、2つ以上の半導体チプ部22,26が貼り合わされた積層半導体チップ27を有する。積層半導体チップ27では、少なくとも第1の半導体チップ部22に画素アレイ23と多層配線層41が形成され、第2の半導体チップ部26にロジック回路25と多層配線層55が形成される。第1の半導体チップ部22には、一部の半導体部分が全て除去された半導体除去領域52が形成され、半導体除去領域52内に第1の半導体チップ部22と第2の半導体チップ部26との間を接続する複数の接続配線67が形成される。この半導体装置は、裏面照射型の固体撮像装置として構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 層間絶縁膜内の水分などによるバリアメタルの腐食を防止し、銅配線の信頼性の低下及び抵抗値の上昇を抑制し得る半導体装置、及びその製造方法を提供する。

【解決手段】 メチル基を含有する層間絶縁膜32内に配線溝37を形成する。配線溝37が形成された絶縁膜32に紫外線又は電子線を照射した後に、メチル基を有するガスを用いて絶縁膜の露出面を疎水化する。配線溝37の疎水化された内面に沿ってバリアメタル層41を形成し、該バリアメタル層41を介して配線溝37を銅配線43で充填する。一実施形態において、配線溝37はメタルハードマスク47を用いて絶縁膜32をエッチングすることにより形成され、絶縁膜32への紫外線又は電子線の照射は、メタルハードマスク47を残存させた状態で行われる。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】絶縁表面上に第1配線と、前記第1配線を覆う第1層間絶縁膜と、前記第1層間絶縁膜上の一部に接して第2層間絶縁膜と、前記第1層間絶縁膜及び前記第2層間絶縁膜上に第2配線とを有し、前記第1配線と前記第2配線とが重なっている領域には、前記第1層間絶縁膜と前記第2層間絶縁膜とが積層された半導体装置である。第1配線と第2配線間に層間絶縁膜が積層されていることで寄生容量の低減が可能となる。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】積層される半導体ウェハにより、量産性向上、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。

【解決手段】半製品状態の回路を備えた半導体ウェハ31,45を複数積層して貼り合わせ、複数の半導体ウェハ31,45からなる積層体を形成し、積層体のうち、上層の半導体ウェハ31の半導体層を薄肉化する。また、上層の半導体ウェハ31側から最下層の半導体ウェハ45に形成された配線に達する貫通開口部77を形成し、最下層の半導体ウェハ45に形成された配線を露出させることにより電極パッド部78を形成する。これにより、貫通開口部77は、半導体ウェハ31,45の脆弱な接合面を貫通して形成され、電極パッド部78は、脆弱な接合面よりも下層の半導体ウェハ45の配線において形成される。これにより、電極パッド部78における外部配線との配線時に、脆弱な接合面に係る応力を低減することができる。

(もっと読む)

半導体装置

【課題】多層配線間で形成される寄生容量を低減することを目的の一とする。

【解決手段】画素、メモリ部、又はCMOS回路等に配置されたトランジスタのチャネル形成領域213、214と重なる第1の配線(ゲート電極)の一部または全部と第2の配線(ソース線またはドレイン線)154、157とを重ねる。また、ゲート電極と第2配線154、157の間には第1の層間絶縁膜149及び第2の層間絶縁膜150cを設け、寄生容量を低減した半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】誘電率の比較的低い誘電体膜に、累積的に紫外線を含む光が照射されることに起因する不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜5上にLow−k膜9が形成される。次に、Low−k膜9に、所定のランプから発せられる紫外線を含む光が照射される。次に、Low−k膜9の開口部9a内にTiO2からなるバリア膜11と銅配線13が形成される。Low−k膜9上にSiCN膜15およびSiON膜17が形成される。次に、SiON膜17の上にLow−k膜19が形成される。そのLow−k膜19に、所定のランプから発せられる紫外線を含む光が照射される。

(もっと読む)

半導体装置の製造方法

【課題】露光によるフォトレジスト膜のパターニングに際し、下地層からの反射光を抑制することができ、かつ、製造コストが抑えられる半導体装置の製造方法を提供する。

【解決手段】半導体基板2上の第1層間絶縁膜3に第1導電層7を形成する工程と、第1導電層7上にストッパー膜8を形成する工程と、ストッパー膜8上にビアホール14が形成された第2層間絶縁膜9を形成する工程と、染料が含有されているフォトレジスト膜を、前記ビアホール内に埋め込むとともに、第2層間絶縁膜9上に形成する工程と、フォトレジスト膜に配線パターンを形成する工程と、配線パターンが形成されたフォトレジスト膜をマスクとして、第2層間絶縁膜9をエッチングして、第2溝部18を形成する工程と、ビアホール14内及び第2溝部18内に第2導電層20を形成する工程と、を備えることを特徴とする。

(もっと読む)

1 - 20 / 95

[ Back to top ]