Fターム[5F038AC01]の内容

Fターム[5F038AC01]の下位に属するFターム

電極領域又は電極部分 (2,206)

PN分離、素子分離、寄生容量 (79)

素子積層 (300)

溝、凹凸(溝堀型等) (232)

Fターム[5F038AC01]に分類される特許

1 - 7 / 7

半導体装置

【課題】パッシブ型RFタグは、小型軽量化が可能であるという利点を有している。しかし、駆動電力には限りがある。最大通信距離や同時認識数を増やすためには、半導体装置内での消費電力の効率化、低消費電力化が求められる。

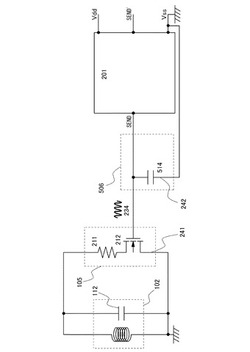

【解決手段】本発明の一態様の半導体装置は、アンテナ回路と、前記アンテナ回路と電気的に接続されている変調回路と、前記変調回路と電気的に接続されているフィルタ回路と、前記フィルタ回路と電気的に接続されている論理回路とを有し、前記変調回路は第1の抵抗とトランジスタを有し、前記フィルタ回路は容量を有し、前記第1の抵抗の一方の端子は、前記トランジスタのソース又はドレインの一方と電気的に接続し、前記第1の抵抗の他方の端子は、前記アンテナ回路と電気的に接続し、前記トランジスタのゲートは、前記容量の一方の端子及び論理回路と電気的に接続する。

(もっと読む)

半導体集積回路のレイアウト設計装置、レイアウト設計方法及びレイアウト設計プログラム並びに半導体集積回路装置の製造方法

【課題】半導体集積回路の設計TATの増大を防止する。

【解決手段】レイアウト設計装置は、パッケージに起因して半導体チップに加わるパッケージ応力の応力値の分布を示す応力分布データを読み込む応力分布データ読込み手段3と、半導体チップのチップレイアウトデータから素子レイアウトデータを抽出する素子レイアウトデータ獲得手段7と、半導体チップに搭載される各素子について応力値と素子の特性変動の関係を示した検量線データを保持する検量線データ保持部9と、応力分布データ、素子レイアウトデータ及び検量線データに基づいて各素子についてパッケージ応力による素子特性変動を算出する素子特性変動計算手段11と、素子特性変動を打ち消すように素子レイアウトデータを補正する素子レイアウト補正手段13と、補正後素子レイアウトデータを用いてチップレイアウトデータを補正するチップレイアウト補正手段と、を備えている。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

能動および受動デバイスをチップ内に配置する方法

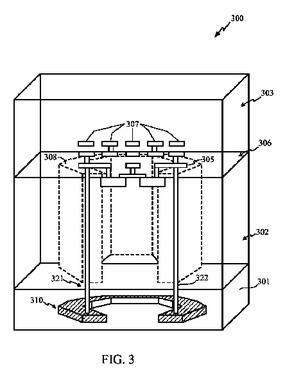

半導体ダイ(300)は、第1および第2の面をもつ半導体基板層(302)と、半導体基板層の第2の面に隣接する金属層と、半導体基板層の第1の面上の活性層(306)内の1つまたは複数の能動デバイス(305)と、活性層と電気的に接続される金属層内の受動デバイス(310)とを含む。受動デバイスは、シリコン貫通ビア(TSV)(321、322)によって、活性層に電気的に結合することができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】半導体装置において、少ないチップ部品で給電系の広帯域低インピーダンス化を実現することができる技術を提供する。

【解決手段】メモリLSI3の動作に応じて、メモリLSI3の給電系に接続された容量値可変のデカップリングコンデンサ部品5の容量値を動的に制御することにより、少ないチップ部品でメモリLSI3の給電系の広帯域低インピーダンス化を実現する。

(もっと読む)

薄膜コンデンサ及びその製造方法

【課題】 リーク特性の悪化による信頼性の低下を防ぎ、製造歩留まりの向上を図ることができる薄膜コンデンサを提供する。

【解決手段】 誘電体層14及び上部電極16に、上部電極16の中心部から端部に向かうテーパ24が形成されている。テーパ24の傾斜角度αは、40°以下,好ましくは30°以下,更に好ましくは23°以下に設定される。このように、MIM構造の端面にテーパ24を形成することで、端部における面積が1.5倍ないし2倍以上になるため、電界の集中が緩和され、電圧破壊による故障が低減されるようになって、信頼性や製造歩留まりが改善されるようになる。

(もっと読む)

容量素子、半導体装置及び半導体装置のパッド電極の端子容量設定方法

【課題】 実効入力抵抗を増大させず良好なスペース効率を保ち、かつ、きめ細かい端子容量の調整を実現可能なパッド電極構造を有する半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体基板上に形成されたパッド電極10と、パッド電極10の近傍に配置されパッド電極10と絶縁されつつ外部固定電位と接続された周囲配線部11と、パッド電極10における外縁付近の開口部に導電材料を埋め込んで下方に延伸形成されパッド電極と電気的に接続された第1のビア12と、周囲配線部11の開口部に導電材料を埋め込んで下方に延伸形成され周囲配線部と電気的に接続された第2のビア13とを備え、第1のビア12と第2のビア13は、互いの側面間に容量を形成するように対向配置されて構成されている。

(もっと読む)

1 - 7 / 7

[ Back to top ]