Fターム[5F038AC05]の内容

半導体集積回路 (75,215) | キャパシタ (4,915) | 構造 (2,824) | 電極領域又は電極部分 (2,206) | 多結晶電極、金属電極 (1,364)

Fターム[5F038AC05]に分類される特許

1 - 20 / 1,364

ESD保護回路およびこれを備えた半導体装置

三次元配置部品を有する化合物半導体集積回路

半導体装置

容量素子

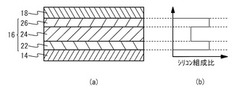

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体可変容量素子

【課題】PN接合構造の可変容量素子は、逆電圧を印可するため、少なからぬリーク電流を生じる。リーク電流の小さい理想的な半導体可変容量素子を提供する。

【解決手段】P型半導体層1とN型半導体層2よりなる積層体と電極との間に絶縁層3を設けることにより、リーク電流の流れない半導体可変容量素子が可能となった。また、電極への逆方向バイアス電圧の印加により、低周波において、印加された逆方向バイアス電圧に比例する可変容量を生じる。

(もっと読む)

高周波スイッチ

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

集積電子構成要素を有する半導体発光装置

【課題】集積電子構成要素を含む半導体発光装置を提供する。

【解決手段】シリコンダイオード、抵抗体162、コンデンサ164、及び誘導子のような1つ又はそれよりも多くの回路要素が、半導体発光装置の半導体構造110と装置を外部構造に接続するのに使用される接続層との間に配置される。半導体構造に対するn接点114は、複数のバイアにわたって分散され、これは、1つ又はそれよりも多くの誘電体層によってp接点112から隔離されている。回路要素は、接点−誘電体層−接続層のスタックに形成される。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

コンデンサ

【課題】小型でかつ高い静電容量を得られ、さらに絶縁性能の高い薄膜誘電体を用いたコンデンサを提供する。

【解決手段】薄膜コンデンサは無機物層と、自己組織化によって形成した有機物層とを積層した厚み10nm以下の誘電体膜と、前記誘電体膜の表面に形成された電極膜とを有する。電極膜はアルミを蒸着法によって、誘電体膜はアルミ蒸着膜を酸素プラズマ処理によって酸化膜を形成した表面に有機膜を付与して、形成することができる。これらを繰り返し積層、さらに巻回することが望ましい。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

シリコン装置

【課題】強誘電体層中の金属原子がシリコン層に拡散することを抑制または防止して、小型化および特性の向上を図ることができる構造のシリコン装置を提供する。

【解決手段】シリコン装置としてのインクジェットプリンタヘッド1は、シリコン基板2と、シリコン基板2上に形成された酸化シリコン層5Bと、酸化シリコン層5B上に形成された拡散防止膜70と、拡散防止膜70上に設けられた圧電素子6とを含む。シリコン基板2にはインク溜まりとしての加圧室62が形成されており、その天面部の薄いシリコン層5Aと酸化シリコン層5Bとが振動膜5を構成している。圧電素子6は、拡散防止膜70に接する下部電極7と、下部電極7上に設けられた圧電体層8と、圧電体層8上に設けられた上部電極9とを含む。拡散防止膜70は、圧電体層8中の金属原子の拡散を防ぐ。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

1 - 20 / 1,364

[ Back to top ]