Fターム[5F038AC14]の内容

Fターム[5F038AC14]の下位に属するFターム

Fターム[5F038AC14]に分類される特許

1 - 20 / 295

ESD保護回路およびこれを備えた半導体装置

半導体装置

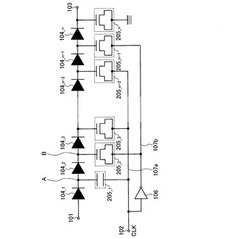

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

半導体装置

【課題】半導体基板上においてキャパシタが占める面積の増大を抑えつつ、キャパシタ全体の容量を増やすことを可能とした半導体装置を提供する。

【解決手段】P型のシリコン基板1と、シリコン基板1に設けられたN−領域11と、N−領域11上に設けられた第1の誘電体膜15と、第1の誘電体膜15上に設けられた第1の電極17と、第1の電極17の上面に設けられた第2の誘電体膜19と、第1の電極17の側面に設けられた第3の誘電体膜21と、P型のシリコン基板1のうちのN−領域11に隣接する隣接領域5上に設けられた第4の誘電体膜23と、第2の誘電体膜19と第3の誘電体膜21及び第4の誘電体膜23を覆うようにシリコン基板1の上方に設けられた第2の電極24と、を有する。

(もっと読む)

MIMキャパシタとその製造方法、並びに半導体装置

【課題】堆積界面のない誘電体膜を有するMIMキャパシタとその製造方法、並びにそのようなMIMキャパシタを備えた半導体装置を提供する。

【解決手段】MIMキャパシタは、半導体基板と、該半導体基板の上方に形成された下部電極16と、該下部電極の上に形成された誘電体膜18と、該誘電体膜の上に該下部電極と重なるように形成された上部電極20と、を備える。そして、該下部電極の上面と側面は、該下部電極の中央部分の厚さよりも大きい曲率半径を持つ第1曲面で、角部が形成されないように接続され、該下部電極は、該下部電極の側面に該下部電極の中央部分の厚さよりも大きい曲率半径を持つ第2曲面を形成することにより、該下部電極の外周に向かうほど薄く形成されている。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

容量素子および半導体装置

【課題】容量素子のQ値(Quality Factor)特性を向上する。

【解決手段】容量素子は、互いに対向する一対の電極EL10、EL20と、一対の電極の一方の電極に設けられ、一方の電極の両端部から間隔を置いて配置された第1端子部とTE10、一対の電極の他方の電極に設けられ、他方の電極の両端部から間隔を置いて配置された第2端子部とTE20を有している。

(もっと読む)

低電圧デバイス保護付き高電圧複合半導体デバイス

【課題】低電圧デバイス保護付き高電圧複合半導体デバイスを提供する。

【解決手段】電圧保護されたデバイスを含複合半導体デバイスの1つの好適な実現では、ノーマリオフ複合半導体デバイス300が、第1出力キャパシタンス318を有するノーマリオンIII-窒化物パワートランジスタ310と、このノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイス320を具えて、このノーマリオフ複合半導体デバイスを形成し、このLVデバイスは第2出力キャパシタンス348を有する。第1出力キャパシタンス対第2出力キャパシタンスの比率を、ノーマリオンIII-窒化物パワートランジスタのドレイン電圧対LVデバイスの降伏電圧の比率に基づいて設定して、LVデバイスの電圧保護を行う。

(もっと読む)

可変容量回路およびシステム

【課題】 電気信号の電圧振幅が大きいときにも、可変容量回路に形成されるトランジスタの寄生ダイオードがオンすることを防止し、電気信号の波形が歪むことを防止する。

【解決手段】 可変容量回路は、電気信号が伝達されるノードに一端が接続される容量素子と、容量素子の他端と第1電源線との間に配置される第1トランジスタと、他端と第2電源線との間に直列に配置される抵抗素子および第1トランジスタと極性が逆の第2トランジスタとを含んでいる。第1トランジスタはゲートで第1制御信号を受け、第1モード中にオンし、第2モード中にオフする。第2トランジスタは、ゲートで第2制御信号を受け、第1モード中にオフし、第2モード中にオンする。これにより、容量素子の他端の中心電圧は、第1トランジスタのオフ中に第2電源線の電圧に設定され、第2トランジスタのオフ中に第1電源線の電圧に設定される。

(もっと読む)

半導体装置およびその製造方法

【課題】基板裏面側にグラウンドプレーンと信号配線との絶縁構造を構成しなくてもすみ、かつ、寄生インダクタンスをゼロに近づけられるようにする。

【解決手段】外側導体2aと中心導体2cとの間に誘電体2bを配置し、外側導体2aを下面配線層6に直接接触させると共に、誘電体2bを中心導体2cの先端に残す。これにより、中心導体2cと外側導体2aとの間の誘電体2bを通じてノイズが流れる。よって、キャパシタ構造部2と下面配線層6との間の寄生インダクタンス成分や寄生抵抗成分をゼロに近づけられ、キャパシタ構造部2でフィルタリングされたノイズをより除去できる。また、中心導体2cが誘電体2bを貫通していないため、中心導体2cと接続するための配線層をシリコン基板1の裏面側に形成しなくても済む。このため、シリコン基板1の裏面側にはグラウンドプレーンとなる下面配線層6のみ形成すれば良く、多層配線等の複雑な工程が不要となる。

(もっと読む)

半導体装置

【課題】容量素子を備え、電気的特性の安定化が可能な半導体装置を提供する。

【解決手段】半導体基体1上の配線層に形成されている配線と絶縁層とからなる容量素子10を備える。そして、容量素子10の形成領域内の半導体基体11上に形成されている導体パターンと、導体パターンの電位を固定するための電位固定端子28とを備える半導体装置を構成する。

(もっと読む)

半導体装置

【課題】配線層の空きスペースを利用して電源補償容量を形成する。

【解決手段】Y方向に配列された複数のメモリマットMATと、Y方向に隣接するメモリマットMAT間にそれぞれ配置されたセンス領域SAと、カラム選択信号を生成するカラムデコーダ13と、複数のメモリマットMAT上をY方向に延在し、カラム選択信号をカラムデコーダ13から複数のセンス領域SAに供給するカラム選択線YSと、カラムデコーダ13からみて最も遠いメモリマットMATa上に設けられた電源補償容量30とを備える。電源補償容量30は、容量電極として機能する電源配線VL1,VL2を含み、その少なくとも一方がカラム選択線YSと同じ配線層に形成されている。本発明によれば、カラム選択線YSを形成する必要のないメモリマットMATa上に電源補償容量30を設けていることから、チップ面積を縮小することが可能となる。

(もっと読む)

1 - 20 / 295

[ Back to top ]