Fターム[5F038AC15]の内容

Fターム[5F038AC15]に分類される特許

1 - 20 / 762

三次元配置部品を有する化合物半導体集積回路

容量素子

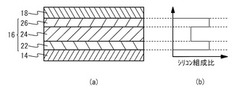

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

シリコン装置

【課題】強誘電体層中の金属原子がシリコン層に拡散することを抑制または防止して、小型化および特性の向上を図ることができる構造のシリコン装置を提供する。

【解決手段】シリコン装置としてのインクジェットプリンタヘッド1は、シリコン基板2と、シリコン基板2上に形成された酸化シリコン層5Bと、酸化シリコン層5B上に形成された拡散防止膜70と、拡散防止膜70上に設けられた圧電素子6とを含む。シリコン基板2にはインク溜まりとしての加圧室62が形成されており、その天面部の薄いシリコン層5Aと酸化シリコン層5Bとが振動膜5を構成している。圧電素子6は、拡散防止膜70に接する下部電極7と、下部電極7上に設けられた圧電体層8と、圧電体層8上に設けられた上部電極9とを含む。拡散防止膜70は、圧電体層8中の金属原子の拡散を防ぐ。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

キャパシタ及びその製造方法

【課題】少ない工程数で生産性良く、アルミ酸化膜を誘電膜とする容量の大きいキャパシタを製造する。

【解決手段】キャパシタ1の製造方法は、Alを含む第1電極30を形成する工程と、第1電極30を覆う層間絶縁膜40を形成する工程と、層間絶縁膜40において第1電極30上の少なくとも一部に開口部41を形成して、第1電極30の表面の少なくとも一部を露出させる工程と、開口部41内の第1電極30の露出部30Aをアノードとして陽極酸化を実施して、酸化膜31を形成する工程と、開口部41内にプラグ60を形成する工程と、プラグ60上に第2電極71を形成する工程とを有する。

(もっと読む)

硬化性組成物および該組成物を用いた絶縁膜

【課題】本発明の目的は、特定の構造を有するポリシロキサン化合物を含有する高誘電率でありかつ絶縁性に優れた薄膜となる硬化性組成物に関するものである。本発明の硬化性組成物を硬化して得られる薄膜は、特に薄膜トランジスタのゲート絶縁膜やコンデンサ用材料として有用である。

【解決手段】アルケニル基を有する化合物(A)および特定の構造を有するポリシロキサン化合物(B)からなるヒドロシリル化反応性を有する硬化性組成物であり、得られる硬化物における1kHzでの比誘電率が3.5以上であることを特徴とする硬化性組成物により達成できる。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量値及びその変化量が大きく且つQ値の高い可変容量素子を備える半導体装置及びその製造方法を実現する。

【解決手段】半導体装置は、可変容量素子を備え、当該可変容量素子は、半導体基板11上に形成された下部電極13と、下部電極13上に形成された容量絶縁膜14と、容量絶縁膜14上に形成された上部電極15とを備える。上部電極15は、容量絶縁膜14上に位置する低濃度不純物層15aと、低濃度不純物層15a上に位置し且つ低濃度不純物層15aよりも不純物濃度が高い高濃度不純物層15bとを有する。

(もっと読む)

可変容量装置

【課題】 回路の小型化と消費電力の低減が可能な可変容量装置を提供する。

【解決手段】 容量検出回路31は、可変容量素子2の駆動容量C1のキャパシタンス値に応じた検出信号Sxと、基準となる基準信号Syとを出力する。駆動電圧制御回路21は、検出信号Sxと基準信号Syとを比較し、この比較結果に応じて駆動電圧Vcontを制御し、駆動容量C1を増加または減少させる。駆動容量C1の一端側には駆動電圧Vcontが印加され、他端側には容量検出回路31の検出用電流回路33から検出用電流Icontが周期的に入力される。このため、駆動容量C1が検出用電流回路33に接続されると、駆動容量C1のキャパシタンス値と検出用電流Icontの大きさとに応じて、駆動容量C1の他端側の電圧が上昇し、この電圧に応じた検出信号Sxが出力される。

(もっと読む)

誘電体膜及びその製造方法、並びにキャパシタ

【課題】結晶粒のサイズを制御し、誘電体膜を貫通する結晶粒界やクラックの発生を抑制することによって、リーク電流の少ない高性能のキャパシタを提供する。

【解決手段】電極3,5の間に誘電体膜4が挟持されてなるキャパシタであって、誘電体膜4は、アルカリ土類金属と遷移金属との酸化物に、アルカリ土類金属の炭酸塩を0.1〜10mol%の範囲で含む。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】消費電力を抑えることができる、プログラムユニットを用いた半導体装置を提供する。また、信頼性の高い、プログラムユニットを用いた半導体装置を提供する。さらに集積度の高い、プログラムユニットを用いた半導体装置を提供する。

【解決手段】PLD等のロジックセル間の接続構造を変更する機能を有する半導体回路において、ロジックセル間を接続や切断、あるいはロジックセルへの電源の供給を、オフ電流またはリーク電流が小さい絶縁ゲート電界効果型トランジスタを用いたプログラムユニットによって制御する。プログラムユニットにはトランスファーゲート回路を設けてもよい。駆動電圧を下げるため、プログラムユニットには容量素子を設けて、その電位をコンフィギュレーション時と動作期間とで異なるものとしてもよい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、該基板20の上に位置する第1コンデンサ30と、基板20の上に位置し且つ第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有する。第1コンデンサ30は、第1下部電極31と、第1誘電体32と、第1上部電極33とで構成される。第2コンデンサ40は、第1下部電極31と組成の異なる第2下部電極41と、第1誘電体32と同組成である第2誘電体42と、第2上部電極43とで構成される。第1コンデンサ30の温度が上昇する際に変化する静電容量と、第2コンデンサ40の温度が上昇する際に変化する静電容量とで正負が異なっている。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

1 - 20 / 762

[ Back to top ]