Fターム[5F038AR00]の内容

半導体集積回路 (75,215) | 固定抵抗 (2,429)

Fターム[5F038AR00]の下位に属するFターム

Fターム[5F038AR00]に分類される特許

1 - 3 / 3

半導体装置並びにその製造方法及び光半導体装置

【課題】本発明は、保護回路専用の回路パタンや電極を設けることなく、静電気破壊を防止できる半導体装置並びにその製造方法を提供することを目的とする。

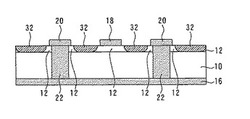

【解決手段】本発明に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、不純物が拡散された半導体層と、前記半導体層に設けられた電気回路と、前記半導体層上に設けられ、前記電気回路に接続された電極と、前記半導体層上に設けられ、接地又は一定電圧に維持された第1の定電圧導体と、を備え、前記電極及び前記第1の定電圧導体は前記半導体層にそれぞれオーミック接触し、前記半導体層は、トラップが導入されたトラップ導入領域を前記電極と前記第1の定電圧導体との間に有することを特徴とするものである。

(もっと読む)

半導体集積回路装置及びその検査方法

【課題】限られた領域に多くの被測定素子を搭載でき、かつ、短時間で多数個の被測定素子の特性の良否判定及び特性異常を検出することができ、その結果、検査コストを低減できる半導体集積回路装置及びその検査方法を提供する。

【解決手段】半導体集積回路装置は、複数個の被測定素子11と、複数の選択素子12と、所望の被測定素子11を選択するアドレス制御・選択回路14と、複数個の被測定素子11の各々の良否判定の基準値を設定する規格値設定手段15と、被測定素子11の電気特性値と基準値との比較を複数の被測定素子11の全てに対して順に行う比較回路17と、比較回路17による比較結果に基づいて計数を行うカウンタ回路18と、回路動作を制御するための制御回路16とを備える。カウンタ回路18は、基準値を外れた被測定素子11の総数を出力する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】本発明は、半導体チップに形成された抵抗素子の抵抗値を測定する際の精度を向上させることができる半導体装置及びそのテスト方法を提供する。

【解決手段】測定対象の抵抗素子Rinに直列接続されたスイッチング素子TR10と、測定対象の抵抗素子及びスイッチング素子の直列回路にそれぞれ並列接続され、オン状態にされた場合にはそれぞれ所望の抵抗値を有する複数のトランジスタTR201及びTR202と、スイッチング素子をオフ状態にした上で、複数のトランジスタのスイッチング動作を制御し、複数のトランジスタによって形成される抵抗の抵抗値を変化させることにより、測定対象の抵抗素子に接続されるように生じる寄生抵抗Rp、Rs、Rb、Rps及びRsbの抵抗値を測定した後、スイッチング素子をオン状態にすると共に、複数のトランジスタをオフ状態にすることにより、寄生抵抗の抵抗値を基に、測定対象の抵抗素子の抵抗値を測定する測定部とを備える。

(もっと読む)

1 - 3 / 3

[ Back to top ]