Fターム[5F038AR12]の内容

Fターム[5F038AR12]の下位に属するFターム

Fターム[5F038AR12]に分類される特許

1 - 20 / 58

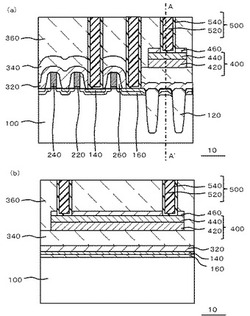

半導体装置及び半導体装置の製造方法

【課題】多層配線中に、抵抗率が高く、かつ抵抗温度係数が小さい抵抗素子を備える半導体装置を提供する。

【解決手段】第1絶縁層(層間絶縁層340)と、第1絶縁層(層間絶縁層340)上に設けられ、少なくとも表層がTaSiN層440である抵抗素子400と、第1絶縁層(層間絶縁層340)および抵抗素子400上に設けられた層間絶縁層360と、層間絶縁層360に設けられ、一端がTaSiN層440と接続する複数のビア500と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を確保する。

【解決手段】基板と、基板に埋め込まれ、複数の開口部を有する絶縁膜と、複数の開口部内に位置する基板に設けられた複数のダミー拡散層20と、抵抗素子形成領域40において、平面視でダミー拡散層20と重ならないように絶縁膜上に設けられ、かつ第1方向に延伸する複数の抵抗素子10と、抵抗素子形成領域40において、絶縁膜上およびダミー拡散層20上に設けられ、かつ第1方向に延伸する複数のダミー抵抗素子12と、を備え、ダミー抵抗素子12は、平面視で、第1方向と基板に水平な面内において垂直な第2方向に並ぶ少なくとも二つのダミー拡散層20と重なっている。

(もっと読む)

ヒータ配線付き半導体チップ

【課題】半導体チップの高信頼実装技術を提供。

【解決手段】半導体チップ4は、基板100と、前記基板の一方の面に形成されたデバイス層80と、電磁波の輻射により発熱するヒータ配線302と、前記デバイス層と電気的に接続される電極103とを備えることを特徴とする。半導体チップ4を実装基板に実装する際には、ヒータとしての金属配線膜302を発熱させることにより、固着材料を溶かして半導体チップを実装基板と接続させる。

(もっと読む)

半導体装置及びその製造方法

【課題】抵抗値の調整が容易な半導体装置及びその製造方法を得る。

【解決手段】シリコン基板上に所定間隔で形成された配線層と、前記シリコン基板上及び前記両配線層上に形成されたパッシベーション膜と、前記両配線間の前記パッシベーション膜上に形成された抵抗体層と、前記抵抗体層上に形成された、各配線層と抵抗体層とを導通する電極層とを備え、前記抵抗体層上に、前記両電極層間における該抵抗体層の平面的な大きさを決める絶縁バリア層を形成した。

(もっと読む)

集束加熱源を使用して半導体素子のインピーダンスを変更する方法

【課題】集束加熱源を使用して半導体素子すなわち半導体デバイスのインピーダンスを調整(すなわち、修正または変更)する方法が提供される。

【解決手段】この方法は、集束加熱源(例えば、レーザ)の溶融作用によって、より高ドーパント濃度の隣接領域からドーパントを拡散させることによって、低ドーパント濃度の領域のドーパント・プロファイルを変更する(すなわち、ドーパント濃度を増加させる)ことによって、半導体素子すなわち半導体デバイスのインピーダンスを微調整するために利用されてよい。本発明は、特に、以前には存在しなかった導電性リンクと導電路との形成のための、回路に対するレーザの使用に関する。さらに、本発明は、特に、ギャップ領域の長さに沿った1つまたは複数の導電性ブリッジの位置に応じてインピーダンスの変更(すなわち、トリミングまたは調整)が有利に行われることが可能な手段に関する。

(もっと読む)

高周波デバイス

【課題】 渦電流や寄生容量の発生を抑制することができ、優れた高周波特性を示す小型の高周波デバイスを提供する。

【解決手段】 開口14を有する基板11上の誘電体層13にバンドパスフィルタBPFを備える。BPFは例えば第1誘導性素子L1および第1容量性素子C1の組と、第2誘導性素子L2および第2容量性素子C2の組と、第3誘導性素子L3および第3容量性素子C3の組とにより構成されている。開口14は第1誘導性素子L1に対向する位置に設けられている。基板11に対して開口14を設けることにより第1誘導性素子L1の直下での寄生容量および渦電流の発生が抑制され、これにより信号損失が低減されてフィルタ回路の特性が向上する。

(もっと読む)

電子デバイスおよびその製造方法

【課題】抵抗値を精度よく容易に設定可能な構造の抵抗素子を有する電子デバイスを実現する。

【解決手段】半導体等の基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜(金属薄膜11)が配置されている。この金属薄膜11は、2種類以上の抵抗率をもつ。この金属薄膜11は、望ましくは、抵抗率が異なる複数の面領域(高抵抗面領域RHと低抵抗面領域RL1,RL2)をもつ複抵抗領域型の金属薄膜11Wである。

(もっと読む)

半導体装置

【課題】内部回路を静電破壊から保護するための静電気保護素子を備えた半導体装置を提供する。

【解決手段】保護トランジスタQn1及び保護トランジスタQn2各々は、ドレイン端子がパッドへと接続され、ゲート端子及びソース端子がVSSへと接続される。一方、予備トランジスタQn3及び予備トランジスタQn4は、ゲート端子及びソース端子がVSSへと接続され、ドレイン端子は各々抵抗素子R3及び抵抗素子R4を介してVSSへと接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】 設計値に近似の抵抗値を有するポリシリコン抵抗素子を備えた半導体装置およびその製造方法を提供する。

【解決手段】 本発明の半導体装置では、半導体基板の主面を含む内部にMOSトランジスタが形成され、このMOSトランジスタを取り囲んで素子分離絶縁膜3が形成されている。この素子分離絶縁膜3上方には、端子部11とこの端子11間に形成された抵抗部12とを備えたポリシリコン抵抗素子10が形成されている。そして、ポリシリコン抵抗素子10の抵抗部12は、同一形状、および同一寸法の複数の網目13を有する網構造に構成されており、かつ隣接する網目13の間隔が全て同一に形成されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】抵抗特性のばらつきが少ない抵抗素子を低コストで形成することを可能とした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】SOI領域のSi基板1上にSiGe層を形成する工程と、SiGe層上にSi層13を形成する工程と、Si層13及びSiGe層を平面視で抵抗素子の形状に形成する工程と、Si層13及びSiGe層の各側面にサイドウォール17を形成する工程と、SiGe層を露出する溝部19を形成する工程と、サイドウォール17によりSi層13の側面が支えられた状態で、溝部19を介してSiGe層をエッチングすることにより、Si層13とSi基板1との間に空洞部21を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に対し並列接続され、基板領域21とキャパシタ210と抵抗220とを含む半導体スナバ200とを備えている。抵抗220の少なくとも一部が、半導体スナバ200の基板領域21の一主面上に直接的にもしくは間接的に形成された、導電性材料からなる膜状の導電層17を含み、かつ、抵抗220に電流が流れる際に、導電層17に流れる電流の経路の少なくとも一部が、膜厚方向以外の方向へ流れる。

(もっと読む)

半導体装置

【課題】基板の面内方向のばらつきに関わらず、素子の特性値の設計値からのずれを低減する。

【解決手段】半導体装置100は、基板に形成され、それぞれ、長軸方向と短軸方向とを有する所定パターンの膜を含み、基板の面内方向の同一層に分散配置された複数の分割素子(200aまたは200b)を含む。複数の分割素子は、第1の方向において隣接する分割素子の膜の長軸方向が異なるか、または、第1の方向において隣接する分割素子が、第1の方向と直交する第2の方向に、当該第2の方向における分割素子の長さよりも小さい量だけずらして配置される。

(もっと読む)

半導体装置

【課題】半導体基板において回路が形成される領域の占有面積を削減して小型化が図られる半導体装置を提供する。

【解決手段】高電位が印加されるセンス抵抗9と第1ロジック回路26が形成された高電位ロジック領域25の周囲を取り囲むように、分離領域30を介在させて、RESURF領域24が形成されている。RESURF領域24の外側には、接地電位に対して第2ロジック回路22を駆動させるのに必要な駆動電圧レベルが印加される第2ロジック回路領域が形成されている。RESURF領域24では、電界効果トランジスタTのドレイン電極12が内周に沿って形成され、ソース電極10が外周に沿って形成されている。また、センス抵抗9に接続されたポリシリコン抵抗4が、内周側から外周側に向かってスパイラル状に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】適切な抵抗素子を得ることが可能な半導体装置を提供する。

【解決手段】素子領域11及び素子分離領域12を含む基板10と、素子領域上に形成されたゲート絶縁膜21と、ゲート絶縁膜上に形成された金属膜22及び金属膜上に形成された第1の半導体膜23を有するゲート電極とを含むトランジスタ部と、基板の上方に形成され且つ第1の半導体膜と同一の材料で形成された第2の半導体膜23と、基板と第2の半導体膜との間に形成された空洞25とを含む抵抗素子部とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】アナログ回路を構成する抵抗体において、抵抗体の抵抗長が縮小化されることがあっても、アナログ回路を構成する各抵抗体の抵抗値間にバラツキが生じることを抑制する。

【解決手段】アナログ回路を構成する抵抗体3を有する半導体装置であって、半導体基板1上に形成され、長手方向に延びるボディ部3aと該ボディ部3aの端部に連接するヘッド部3bとを有し、且つシリコンからなる抵抗体3と、抵抗体3のヘッド部3bの上部に形成された金属シリサイド膜6と、抵抗体3を覆う層間絶縁膜7中に形成され、金属シリサイド膜6を介して、抵抗体3と電気的に接続するコンタクトプラグ8とを備え、ボディ部3aとヘッド部3bとの境界長は、抵抗体3の抵抗幅よりも大きい。

(もっと読む)

1 - 20 / 58

[ Back to top ]