Fターム[5F038AR13]の内容

Fターム[5F038AR13]に分類される特許

1 - 20 / 220

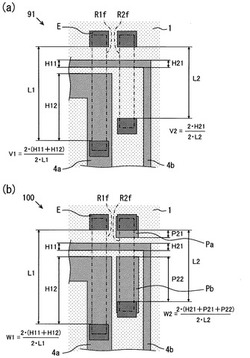

ESD保護回路およびこれを備えた半導体装置

半導体装置

【課題】任意の配線設計に適用でき、高精度な抵抗比を有する2個の抵抗体を備えた小型の半導体装置を提供する。

【解決手段】抵抗体R1f,R2fの長さをL、配線4a,4bの直上にある抵抗体R1f,R2fの外辺の長さを配線上長さH、外辺配線被覆率Vを、V=H/2Lで定義したとき、2個の抵抗体R1f,R2fのうち少なくとも外辺配線被覆率Vの小さい抵抗体R2fの下方において、配線4a,4bと同じ配線層から形成された反射補正パッドPa,Pbが、外辺の直下に配置されてなり、反射補正パッドPa,Pbの直上にある抵抗体R2fの外辺の長さを補正パッド上長さPとし、抵抗体R1f,R2fの外辺配線層被覆率Wを、W=(H+P)/2Lで定義したとき、2個の抵抗体R1f,R2fについて、外辺配線層被覆率Wの差が、記外辺配線被覆率Vの差より小さく設定されてなる半導体装置100とする。

(もっと読む)

集積電子構成要素を有する半導体発光装置

【課題】集積電子構成要素を含む半導体発光装置を提供する。

【解決手段】シリコンダイオード、抵抗体162、コンデンサ164、及び誘導子のような1つ又はそれよりも多くの回路要素が、半導体発光装置の半導体構造110と装置を外部構造に接続するのに使用される接続層との間に配置される。半導体構造に対するn接点114は、複数のバイアにわたって分散され、これは、1つ又はそれよりも多くの誘電体層によってp接点112から隔離されている。回路要素は、接点−誘電体層−接続層のスタックに形成される。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置およびその製造方法

【課題】低電圧で動作するMISトランジスタと高電圧で動作するMISトランジスタや抵抗素子等の素子とを混載した半導体装置において、不純物の導入による素子の特性のばらつきを抑える。

【解決手段】半導体装置は、第1のゲート絶縁膜4aと、第1のゲート電極6aと、第1のゲート電極6aの両側方に形成された第1のLDD領域7aと、第1のLDD領域7aの外側に位置する第1のソース/ドレイン領域13aとを有する第1のトランジスタ30を備える。第1のトランジスタ30は、第1のゲート電極6aの上面上及び側面上から第1のLDD領域7aの少なくとも一方上に亘って設けられた絶縁膜を有しており、前記絶縁膜のうち前記第1のゲート電極の側面上に設けられた部分の膜厚は、前記絶縁膜のうち前記第1のLDD領域の少なくとも一方上で最も薄い部分の膜厚よりも大きい。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

半導体抵抗素子及び半導体抵抗素子を有する半導体モジュール

【課題】無駄な電流や信号の歪み等を発生させることなく、抵抗素子層の電位と、その周辺の半導体基板や電源線、信号線等の電位との電位差によって抵抗素子層の抵抗値が変化してしまうことを抑えることのできる半導体抵抗素子及び半導体抵抗素子を有する半導体モジュールを提供する。

【解決手段】抵抗素子層13は、抵抗値変化係数K1,K2によって、正極領域である領域13Aと負極領域である領域13Bとに分かれている。基準位置oから領域13Aの中心位置a又は領域13Bの中心位置bまでの間の抵抗値を量とする指標値r1,r2と、当該抵抗値R1,R2と、抵抗値変化係数K1,K2との積の総和が零になるように形成される。つまり、領域13Aの抵抗値変化成分dR1と領域13Bの抵抗値変化成分dR2とを相殺して、抵抗素子層13の抵抗値が変化してしまうのを抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に薄膜抵抗体15を構成する金属薄膜およびバリアメタル16を構成するバリアメタル薄膜を形成する。そして、金属薄膜およびバリアメタル薄膜をパターニングし、薄膜抵抗体15と当該薄膜抵抗体15上にバリアメタル膜16aを形成する。その後、バリアメタル膜16a上に絶縁膜17を形成し、絶縁膜17にバリアメタルエッチング部16bを露出させる開口部17aと、コンタクト部を露出させるコンタクトホール17bを形成する。続いて、コンタクトホール17bを介してバリアメタル膜16aと電気的に接続される導電性薄膜18cを形成する。その後、導電性薄膜18cのうちバリアメタルエッチング部16b上に位置する部分をウェットエッチングによってパターニングし、バリアメタル膜16aのうちバリアメタルエッチング部16bをパターニングする。

(もっと読む)

半導体装置

【課題】絶縁耐量を改善することができる半導体装置を得る。

【解決手段】Si基板10(基板)上にゲート抵抗7(下配線)が設けられている。ゲート抵抗7を層間絶縁膜12が覆っている。層間絶縁膜12上に、互いに分離したアルミ配線5a,5b(第1及び第2の上配線)が設けられている。アルミ配線5a,5bを半絶縁性の保護膜4が覆っている。ゲート抵抗7の直上であってアルミ配線5aとアルミ配線5bとの間の領域に、保護膜4が設けられていない。

(もっと読む)

半導体装置

【課題】パッケージ応力に起因する回路部品の電気特性変動のバラツキによって出力信号が変動する内部回路について、パッケージ応力に起因する出力信号の変動を防止する。

【解決手段】半導体チップ5に形成された内部回路はその回路を構成する複数の回路部品の電気特性の変動のバラツキによって出力信号が変動するものである。チップタブ3の平面サイズは半導体チップ5の平面サイズよりも小さい。上方から見てチップタブ3の配置位置の全部が半導体チップ5の配置位置と重なっている。さらに、封止樹脂13に起因して半導体チップ5に加わる応力の大きさがチップタブ3上で均一になる位置関係でチップタブ3の周縁と上記半導体チップ5の周縁は間隔をもって配置されている。上記回路部品は半導体チップ5内部で上記チップタブ3上に配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】素子分離領域での電流リークを低減する。

【解決手段】抵抗素子5用の多結晶シリコン膜50の第2領域52にはドーパントがイオン注入されている。抵抗素子6用の多結晶シリコン膜60の第2領域62には窒素等がイオン注入されている。第2領域52,62は第1領域51,61よりも結晶欠陥密度が高い。抵抗素子7用の多結晶シリコン膜70中の結晶欠陥密度はシリサイド膜73付近においてより高い。抵抗素子8用の多結晶シリコン膜80は素子分離絶縁膜3の開口内のシリサイド膜を介して基板2に接している。当該シリサイド膜付近の基板表面2S内の結晶欠陥密度は周辺よりも高い。

(もっと読む)

半導体装置およびその製造方法

【課題】ダミーアクティブ領域の配置に伴うチップ面積の増大を引き起こすことなく、半導体基板の表面の平坦性を向上させる。

【解決手段】ダミーアクティブ領域であるn型埋込み層3の上部には、厚い膜厚を有する高耐圧MISFETのゲート絶縁膜7が形成されており、このゲート絶縁膜7の上部には、内部回路の抵抗素子IRが形成されている。n型埋込み層3と抵抗素子IRとの間に厚いゲート絶縁膜7を介在させることにより、基板1(n型埋込み層3)と抵抗素子IRとの間に形成されるカップリング容量が低減される構造になっている。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】半導体装置に損傷を与えることなく、単体の抵抗素子自体の抵抗値を精度良く微調整する。

【解決手段】P型の半導体基板10上にN型の半導体層11が形成されている。半導体層11の表面には薄い第2の絶縁膜13が形成され、第1の絶縁膜12及び第2の絶縁膜13上にフローティングポリシリコン層14が形成されている。フローティングポリシリコン層14は第3の絶縁膜15に覆われている。第3の絶縁膜15によって覆われたフローティングポリシリコン層14上にはポリシリコン抵抗層16が形成されている。そして、半導体層11とポリシリコン抵抗層16との間に電圧を印加することにより、第2の絶縁膜13を通してフローティングポリシリコン層14の中に電子が注入され、ポリシリコン抵抗層16の中に正孔蓄積層16Aが形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離酸化膜上に所望の形状の抵抗素子を形成して、抵抗値の精度を高めて信頼性を向上させる。

【解決手段】半導体基板1の表面に形成された所定領域の素子分離酸化膜2上に複数の抵抗素子4が形成された半導体装置であって、抵抗素子4と近接する位置に活性領域3を設けた。抵抗素子4近傍の素子分離酸化膜2を必要な範囲に区切ることができ、CMP法による素子分離酸化膜2の研磨の際に素子分離酸化膜2の中央部に凹みが形成されてしまうことを抑止できるため、抵抗素子4の形状の寸法精度を向上させることが可能となる。

(もっと読む)

抵抗素子及び反転バッファ回路

【課題】無駄な電流や信号の歪みを発生させることなく、抵抗素子層の周辺の半導体基板や、抵抗素子層の上部を通過する電源線、信号線等の電位によって抵抗値が変化するのを抑えることのできる抵抗素子及び反転バッファ回路を提供する。

【解決手段】抵抗素子10は、半導体基板14上に、第1の電極11及び第2の電極12を有する抵抗素子層13が形成されている。第1の電極11の電位によってバイアスされた第1の導電層15と、第2の電極12の電位によってバイアスされた第2の導電層16とで、抵抗素子層13の下部が均等に覆われている。このように、両端をバイアスされた抵抗素子層13の下部又は上部の少なくとも一方を覆う第1の導電層15及び第2の導電層16によって、抵抗素子層13の周辺の半導体基板14等との電圧差による抵抗値の変化を相殺することで、抵抗値の変化を抑える。

(もっと読む)

抵抗素子および抵抗素子の製造方法

【課題】膜厚のばらつきに起因する抵抗値の変動を抑制し、より高精度な抵抗素子を提供する。

【解決手段】第1膜厚(T1)(H1)で形成され、第1幅(W1)を有する抵抗素子第1部分(2)と、第1膜厚(T1)(H1)で形成され、第1幅(W1)に依存して決定する第2幅(W2)を有する抵抗素子第2部分(3)とを具備する抵抗素子を構成する。ここにおいて、第1幅(W1)と第2幅(W2)との和は一定である。また、抵抗素子第1部分(2)は、抵抗素子第1部分(2)の底面からの高さが第1高さ(H1)となる位置に、抵抗素子第1部分(2)の上面を有する。また、抵抗素子第2部分(3)は、抵抗素子第1部分(2)の底面を含む面からの高さが第1高さ(H1)となる位置に、抵抗素子第2部分(3)の上面を有する。そして、抵抗素子第1部分(2)と抵抗素子第2部分(3)とは、接続部を介して互いに接続されている。

(もっと読む)

1 - 20 / 220

[ Back to top ]