Fターム[5F038BB01]の内容

Fターム[5F038BB01]の下位に属するFターム

スレッシュホールド電圧、MOS閾電圧 (147)

ツエナ電圧 (12)

定電圧回路 (374)

分圧 (517)

キャパシタによる安定化 (51)

Fターム[5F038BB01]に分類される特許

1 - 20 / 73

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

正負電圧論理出力回路およびこれを用いた高周波スイッチ回路

【課題】負電圧の変化に対して正常な論理回路動作を確保できる範囲である動作ウィンドウの幅の拡張を可能とし、回路動作の確実性、安定性の向上を図った正負電圧論理出力回路を提供する。

【解決手段】論理入力と負電圧との間に、ゲートに論理入力するエンハンスメント型P型電界効果トランジスタEPFET1とブレークダウン保護用素子13,14とが直列に接続され、ブレークダウン保護用素子14に並列に短絡する切替スイッチ8aが接続される。切替スイッチ8aをオン、オフ制御することで、VSSの変動に対して正常な回路動作を確保できる動作ウィンドウの拡張を可能とする。

(もっと読む)

半導体デバイスの電気的にプログラミング可能なヒューズモジュール

【課題】より小型なeヒューズモジュールを提供する。

【解決手段】半導体デバイスが、eヒューズモジュールおよびプログラミング電流生成器を有する。eヒューズモジュールが電気的にプログラミングするeヒューズ素子(226)のアレイを含む。プログラミング電流発生器が、複数の基準トランジスタ素子(M0〜M6)のセットと、基準トランジスタ素子(M0〜M6)を活性化させて、選択された基準電流を生成するセレクタ(254)と、アレイの選択されたeヒューズ素子(226)に、選択された基準電流に応じたプログラミング電流を印加して、eヒューズ素子(226)の抵抗をプログラミングするカレントミラー(M7、M8、M9)とを有する。

(もっと読む)

半導体装置

【課題】レジュームモードからノーマルモードに復帰する際のラッシュカレント(突入電流)のピーク電流を低減することができる半導体装置を提供する。

【解決手段】半導体装置は、複数のディジーチェン接続されたメモリモジュールを備える。各メモリモジュール77−iは、メモリアレイ4と、レジュームモードにおいて、メモリモジュール内の構成要素への電源電圧の供給を制御するスイッチ16と、レジュームモードからノーマルモードへの移行を指示するレジューム制御信号を受けて、次段のメモリモジュールへ、入力されたレジューム制御信号よりもタイミングが遅延したレジューム制御信号を次段のメモリモジュールへ出力する遅延回路42とを含む。

(もっと読む)

半導体集積回路および電源供給方法

【課題】チップ内でデバイス特性にバラツキがあっても、消費電力を低減させることのできる半導体集積回路および電源供給方法を提供する。

【解決手段】実施形態の半導体集積回路1は、それぞれの領域に半導体デバイスが配置された領域1および領域2を有し、電源供給手段である電源端子T1、T2が、領域1、領域2それぞれに個別に電源を供給する。領域1にはデバイス特性測定回路ROSC1が配置され、領域2にはデバイス特性測定回路ROSC2が配置されている。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体集積回路装置

【課題】製造ばらつきによる出力電圧の精度劣化の補正のため、従来技術ではテストコストの増大や回路規模の増大化を招く問題が発生していた。

【解決手段】n(2以上の正の整数)桁のデジタル信号を電圧信号に変換するDAコンバータを有する半導体集積回路装置であって、それぞれが前記デジタル信号の各ビット桁に対応し、前記デジタル信号に応じて前記電圧信号を生成するn個の電圧生成素子を有し、前記n個の電圧生成素子のうちビット桁が最下位からk(k≦n)番目に対応する電圧生成素子の生成する電圧は、ビット桁が最下位からk−1番目に対応するk−1個の電圧生成素子の生成する電圧に第1の所定の値を足した電圧よりも低くなることを特徴とする半導体集積回路装置。

(もっと読む)

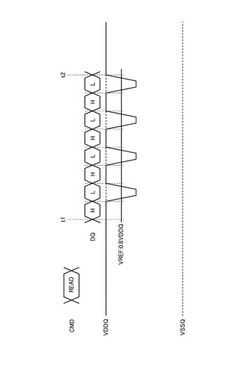

半導体装置

【課題】外部装置を駆動する駆動回路が形成されたチップの面積の増加を抑制することができる半導体装置を提供する。

【解決手段】フラッシュメモリ22がリード動作を実行する場合は、セレクタ26は、ロジック回路30から入力された選択信号SELに応じて基準電圧VREF1を選択する。VLCD昇圧回路28は、基準電圧VREF1を昇圧した駆動電圧VLCDをLCDパネルドライバ12に出力する。また、フラッシュメモリ22は、電源電圧VDDの供給のみでリード動作を実行する。プログラム動作またはイレース動作を実行する場合は、セレクタ26は、選択信号SELに応じて基準電圧VREF2を選択する。VLCD昇圧回路28は、基準電圧VREF2を昇圧した電圧VPPをフラッシュメモリ22に出力する。フラッシュメモリ22は、電圧VPPの供給を受け、プログラム動作またはイレース動作を実行する。

(もっと読む)

半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、誘導性負荷と基準電圧ラインとの間に並列接続される第2のスイッチング素子と第3のスイッチング素子とを有するローサイドスイッチング素子と、第3のスイッチング素子をオンオフする制御回路とを備えている。ローサイドスイッチング素子における誘導性負荷に接続される端子にサージが印加されたとき、制御回路から供給される信号に依らずに、サージ電流は第3のスイッチング素子を介して基準電圧ラインへと放電される。前記端子にサージよりも小さい定格電圧以内の電圧が印加された状態では、第3のスイッチング素子は制御回路から供給される信号に応じてオンオフされる。

(もっと読む)

DC/DCコンバータ用半導体装置

【課題】半導体装置の電源電圧の変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ローサイドスイッチ用のパワーMOS・FETと、そのローサイドスイッチ用のパワーMOS・FETに並列に接続されるショットキーバリアダイオードD1とを同一の半導体チップ5b内に形成した。ショットキーバリアダイオードD1の形成領域SDRを半導体チップ5bの短方向の中央に配置し、その両側にローサイドのパワーMOS・FETの形成領域を配置した。また、半導体チップ5bの主面の両長辺近傍のゲートフィンガ6aから中央のショットキーバリアダイオードD1の形成領域SDRに向かって、その形成領域SDRを挟み込むように複数本のゲートフィンガ6bを延在配置した。

(もっと読む)

プログラマブル論理集積回路

【課題】 異なったLVTTL I/O規格に対して互換性を持つように集積回路の各I/Oを個別に再構成する回路を提供する。

【解決手段】 上述課題は1つのI/O電源電圧のみを用いて達成でき、この電圧は特定の用途に要求されるI/O電圧のうち最も高いものである。回路はI/Oセルの出力電圧を、適合されるべきLVTTL規格のVOHよりも高く最高VIHよりも低くなるように調節することによって動作する。I/Oセルは、I/O電源電圧とパッドの間に接続されるプルアップトランジスタと、該パッドの電圧と対応の規格に応じた基準電圧とを差動増幅する差動増幅器と、差動増幅器の出力信号と出力制御信号とにプルアップトランジスタを選択的にオン状態とするロジックゲートを備える。各I/Oセルは別個に再構成可能であるため、任意のI/Oを任意のLVTTL仕様に適合させることができる。

(もっと読む)

半導体集積回路装置

【課題】

複数の電源を有する半導体集積回路装置において、複数の電源が半導体集積回路装置の外部、内部であるに関わらず、それら電源の立ち上げ順序に依存せずに各回路のオン状態を一意に制御するためのシーケンス制御信号を生成することができる半導体集積回路装置を提供する。

【解決手段】

半導体集積回路装置100は、第1電源VCC1で動作する第1電子回路120と、第2電源VCC2で動作する第2電子回路140と、第1電源VCC1および第2電源VCC2の電圧の大きさを所定の検知レベルで検出し、第1電子回路120のオン動作を制御するためのシーケンス制御信号PS1、および第2電子回路140の所期化を行うためのパワーオンリセット信号PORを生成するシーケンス制御回路180を備える。

(もっと読む)

半導体集積回路装置及びその温度補正方法

【課題】簡単な構成で基準信号の温度補正を行うことができる半導体集積回路装置及びその温度補正方法を提供することを目的とする。

【解決手段】少なくとも3つの異なる温度で半導体集積回路の信号発生手段21,22の出力する基準信号の値を測定し、測定した基準信号の値を目標値とするため信号発生手段のトリミング手段に与える補正制御データを求め、3つの温度で得た信号発生手段のトリミング手段に与える補正制御データから半導体集積回路の使用温度範囲における各温度の補正制御データを算出し、各温度の補正制御データを温度と対応付けて格納手段56に格納し、半導体集積回路の温度検出手段23で検出した温度に応じて格納手段から信号発生手段のトリミング手段に与える補正制御データを読み出して信号発生手段のトリミング手段に設定し、信号発生手段が出力する基準信号の温度補正を行う。

(もっと読む)

PLD回路、集積回路装置及び電子機器

【課題】消費電力を低減できるPLD回路、集積回路装置及び電子機器等を提供すること。

【解決手段】PLD回路は、各トランジスター列が直列接続されたプログラマブルな複数のトランジスターを有する第1〜第m(mは2以上の整数)のトランジスター列TA1〜TAmを含む。第1〜第mのトランジスター列TA1〜TAmの一端に第1の非直流電源VS1が供給される。第1〜第mのトランジスター列TA1〜TAmの各トランジスター列は、複数の入力信号XP(X1P〜XiP)、XN(X1N〜XiN)によってオン・オフされる。第1の非直流電源VS1の電圧により規定される第1のホールド期間に、第1〜第mのトランジスター列TA1〜TAmの他端のノードである第1〜第mのノードNA1〜NAmの電圧レベルを各々出力する。

(もっと読む)

半導体集積回路及び電子機器

【課題】システマテックばらつきとランダムばらつきの両方を考慮した適応型電圧スケーリング技術を実現することにある。

【解決手段】適応型電圧スケーリングを実施するシステム構成において、プロセスばらつきの種類毎に最適な検出回路を設置する。すなわち、システマテックばらつき検出用にゲートディレイの平均値に対する相対値を生成する第1測定回路(100)、及び、ランダムばらつき検出用にゲートディレイの標準偏差に対する相対値を生成する第2測定回路(200)を別々に設置する。夫々の測定回路で生成された相対値に基づいて電源電圧を決定するための制御情報(VCNT)を生成する。これを生成するときは例えばテーブルデータを参照する。

(もっと読む)

発振装置

【課題】発振周波数の変動を防止することができる発振装置を提供する。

【解決手段】トランジスタのゲート電圧に応じて入力端子の信号を出力端子から出力するトランスファゲートPM5,NM5と、トランスファゲートの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第1のインバータIV1と、第1のインバータの出力端子の信号を入力し、入力した信号の論理反転信号を出力する第2のインバータPM6,NM6と、第1のインバータの出力信号の論理反転信号を入力し、入力した信号の論理反転信号をトランスファゲートの入力端子に出力する第3のインバータPM4,NM4と、トランスファゲートの出力端子及び第2のインバータの出力端子間に接続される第1の容量C1と、トランスファゲートの出力端子及び基準電位ノード間に接続される第2の容量C2とを有する発振装置。

(もっと読む)

電気回路

【課題】本発明は、端子数を低減した電気回路を提供することを目的とする。

【解決手段】第一回路と、該第一回路に接続された第一端子と、該第一回路と同時使用されない第二回路と、該第二回路に接続された第二端子と、該第一回路および該第二回路に接続された第三端子と、該第一回路および該第二回路に印加される電源電圧と所定の基準電圧とを比較し、該電源電圧と該基準電圧の大小に応じて該第一回路または該第二回路のいずれか一方を停止させる切り替え手段とを備える。そして、該切り替え手段により該第一回路を停止させた場合には該第二回路が該第二端子と該第三端子により信号の入出力を行い、該切り替え手段により該第二回路を停止させた場合には該第一回路が該第一端子と該第三端子により信号の入出力を行うことを特徴とする。

(もっと読む)

半導体装置

【課題】入力信号のHレベルまたはLレベルを正しく検知できる半導体装置を提供する。

【解決手段】半導体装置100は、閾値調整信号に基づいて論理閾値電位を調整可能な入力バッファ(入力CMOS回路11)と、入力バッファの入力と出力とが結線されたレプリカ(レプリカ12)と、予め設定された基準電位(ノードNdHの電位)を発生する基準電位発生回路(基準電位発生回路13)と、レプリカ(レプリカ12)の出力電位(ノードNdRの電位)と基準電位(ノードNdHの電位)とを比較し、閾値調整信号(閾値調整信号CTRL)を入力バッファ(入力CMOS回路11)とレプリカ(レプリカ12)とに出力する比較回路(比較回路14)と、を備える。

(もっと読む)

半導体装置

【課題】LSI内部に不揮発性記憶素子が不要で、電源ICを制御するファームウェア、電源ICとLSI間の通信が不要で、LSI側のピンを削減でき、開発、検証コストを抑えつつ、最適な電源電圧供給を実現することが可能な半導体装置を提供する。

【解決手段】遅延情報に応じた電源電圧を発生する電源電圧発生回路(電源IC)13と、電源IC13から電源電圧が供給される集積回路(LSI)12と、を有し、LSI12は、電源IC13から電源電圧が供給されて動作するときの遅延情報をモニタする遅延情報モニタ121を含み、電源IC13は、遅延情報モニタ121による遅延情報に関連する遅延情報を保持可能な遅延情報レジスタ131と、遅延情報レジスタ131に保持された遅延情報に応じた電源電圧を発生してLSI12に供給する電圧制御回路133と、を含む。

(もっと読む)

1 - 20 / 73

[ Back to top ]