Fターム[5F038BH01]の内容

Fターム[5F038BH01]の下位に属するFターム

抵抗 (916)

キャパシタ、インダクタンス (556)

ダイオード順方向特性 (712)

接合ブレークダウン (639)

バイポーラトランジスタ (448)

MOSトランジスタ (976)

ピンチオフ、JFET (22)

ガードリング (301)

シールド (400)

Fターム[5F038BH01]に分類される特許

1 - 20 / 146

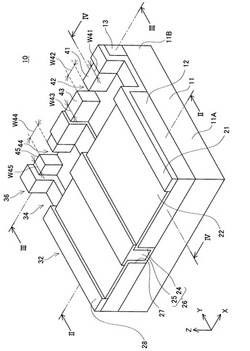

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法

【課題】低ノイズ及び高性能のLSI素子、レイアウト及びその製造方法を提供する。

【解決手段】NMOS素子及びPMOS素子が何れもアナログ及びデジタルモードのような相異なるモードで動作される半導体素子において、これら素子の要求される動作モードによって特定素子にストレスエンジニアリングを選択的に適用する。フォトレジスト160をデジタル回路領域のPMOSトランジスタのみを覆うように形成し、Ge、Siなどのイオン162をストレスコントロール膜150に注入する。デジタル回路領域のPMOSトランジスタを除くあらゆる領域でストレスコントロール膜150はストレス解除膜またはストレス緩和膜152に変換され、デジタル回路領域のPMOSトランジスタのチャネル104bだけに圧縮応力が印加される状態が残る。

(もっと読む)

半導体装置

【課題】半導体装置の放熱効率を向上させる。

【解決手段】ぺルチェ効果によって吸熱する吸熱部(32、35、41)(37、40、43)と、ぺルチェ効果によって放熱する放熱部(31、35、41)(36、40、43)の両方が単一の半導体チップに集積化されている。このような構成によれば、半導体チップにおいて熱を拡散させ、全体としての放熱抵抗を低下させることができる。これは、放熱効率の向上に寄与する。

(もっと読む)

半導体装置

【課題】安定した静電気保護機能を有する半導体装置を提供すること。

【解決手段】半導体装置は、シリコン柱を有するシリコン基板、シリコン柱の側壁に沿って形成されたゲート電極、ゲート電極とシリコン柱との間に形成されたゲート絶縁膜シリコン柱の上部に形成された上部拡散層、及びシリコン基板において上部拡散層より下方に形成された下部拡散層、を有する縦型MOSトランジスタと、下部拡散層と電気的に接続されたパッドと、を備える。サージ電圧が印加された際に下部拡散層と基板との間においてブレイクダウンが発生する。

(もっと読む)

半導体装置

【課題】

マイクロ波帯域において容易に設計可能な半導体チップおよび半導体パッケージ(ディジタル受信装置)を提供することを目的とする

【解決手段】

半導体チップと、前記半導体チップ上に配置されたディジタル部と、前記半導体チップ上に配置されたアナログRF部と、前記ディジタル部から伝播するノイズを遮断するような位置に配置された周期構造を有する誘電体と、を備えた半導体装置である。

(もっと読む)

入力保護回路および半導体集積回路

【課題】全ての入力端子に対してアナログ電流検出回路を設けなくても、入力端子に入力される信号にもとづくデバイスの誤動作やデバイスの故障を防止することができるようにする。

【解決手段】入力保護回路2は、入力回路11と電流供給源12との間に設けられているスイッチ回路21と、入力信号11における所定時間内の論理レベルの変化を検出するレベル変化検出回路22と、レベル変化検出回路22が検出した論理レベルの変化回数を計数し、計数値が所定のしきい値を越えているか否か判定するレベル変化判定回路23と、レベル変化判定回路23が上記の所定時間よりも長い所定期間において計数値が所定のしきい値を越えていると判定した回数が、所定回数を越えているか否か判定し、所定回数を越えていると判定した場合にスイッチ回路21を遮断状態に設定する異常判定回路24とを含む。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路(1000)が、中央配置のドレイン拡散領域(1008)及び分散型SCR端子(1010)を備える1つのドレイン構造(1006)と、分散型ドレイン拡散領域(1016)及びSCR端子(1018)を備える別のドレイン構造(1012)とを含むSCRMOSトランジスタを有する。中央配置のドレイン拡散領域とソース拡散領域との間のMOSゲート(1022)がソース拡散領域へ短絡される。SCRMOSトランジスタを有する集積回路を形成するためのプロセスも開示される。  (もっと読む)

(もっと読む)

BiCMOSプロセス技術における高電圧SCRMOS

集積回路が、ドレイン領域(1010)及びSCR端子(1012)の周りに、低減された表面フィールド(RESURF)領域(1024)と共に形成されるSCRMOSトランジスタを含む。RESURF領域は、ドリフト領域(1014)と同じ導電型であり、ドリフト領域(1014)より一層重くドープされる。  (もっと読む)

(もっと読む)

高周波半導体スイッチ

【課題】トランジスタのドレインとバックゲート間およびソースとバックゲート間に生じる電流の漏洩を抑圧し、高周波信号の透過損失の増大を抑制できる高周波半導体スイッチを得る。

【解決手段】高周波半導体スイッチは、接地部を有するSi等の真性半導体基板と、この真性半導体基板に形成され、バックゲート端子を有するMOSトランジスタと、真性半導体基板の接地部およびMOSトランジスタのバックゲート端子間に設けられたインダクタとを備える。

(もっと読む)

半導体装置

【課題】シールド膜を設けることなく、最上層配線層に形成された信号電位配線を治具の接触による破損から保護する。

【解決手段】半導体基板と、半導体基板上に形成され、半導体素子が形成される半導体層及び前記半導体素子に接続される信号配線が形成される下層配線層と、半導体層及び前記下層配線層より上層に形成され、動作時に電位が変化しない固定電位配線、動作時に電位が変化しうる上層信号電位配線、及び、固定電位が入力される固定電位用ボンディングパッド、及び信号電位が入出力される信号電位用ボンディングパッドが形成された最上配線層と、を備えている。固定電位配線及び固定電位用ボンディングパッドの少なくとも一部は、下層に半導体層及び下層配線層のうち少なくとも一方が形成されることにより、信号電位配線及び前記信号電位用ボンディングパッドの最も高い表面より高く形成されている。

(もっと読む)

静電気放電保護回路

【課題】ESDによる半導体内部回路の破壊を防止し、かつミリ波・準ミリ波帯のような高周波領域において当該半導体内部回路の高周波特性が劣化しないESD保護回路を提供する。

【解決手段】本発明の静電気放電保護回路は、半導体集積回路に接続され、静電気放電から前記半導体集積回路を保護する静電気放電保護回路であって、導電性半導体基板10と、前記導電性半導体基板10の上方に形成された誘電体層13bと、前記誘電体層13bの表面上に形成されている第2の配線層15とを備え、前記第2の配線層15は、一端がパッドに接続され、他端が前記半導体集積回路に接続された第1の信号線17と、一端が前記第1の信号線17に接続され、他端が接地された第2の信号線18とを含む。

(もっと読む)

半導体制御整流素子を有する電源回路及びこれを用いた電源装置

【課題】追加回路を省略して簡易かつ低コストに構成できる突入電流防止回路を提供する。

【解決手段】半導体基体と、該半導体基体の一方の主面上に設けられた第1の主電極及びゲート電極と、前記半導体基体の他方の主面に設けられた第2の主電極とを備えた逆阻止3端子サイリスタと抵抗素子とを並列接続して成る突入電流防止回路であって、

前記逆阻止3端子サイリスタは、

第1の導電型の第1の半導体領域と、

前記第1の半導体領域の一方の主面に露出する部分を有し且つ第2の導電型を有している第2の半導体領域と、

前記第1の半導体領域の一方の主面に露出する部分を有し且つ第1の導電型を有している第5の半導体領域とから成る前記半導体基体を備え、

前記第1の主電極は前記第2の半導体領域のみに接続され、

前記ゲート電極は前記第5の半導体領域及び前記第2の半導体領域に接続されることを特徴とする突入電流防止回路。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタやダイオードなどの回路素子が形成されている半導体装置において、安価で高い信頼性を持つ非破壊ESD保護素子を有する半導体装置を提供することを課題とする。

【解決手段】回路素子と、前記回路素子を静電破壊から保護するための静電気保護素子と、前記静電気保護素子と接続する回路グラウンド線又は回路電源線とを備え、前記静電気保護素子が、前記回路素子と接続する第1導電体と、前記回路グラウンド線又は回路電源線と接続する第2導電体とを備え、前記第1導電体と第2導電体とが、前記第1導電体に印加されたサージ電流を第2導電体へ静電放電し得る間隔の空隙を介して重なるように配置され、前記第1導電体、前記第2導電体、又は前記第1導電体及び第2導電体の両方が、前記重なるように配置された部位の内、少なくとも1部の全周囲において、前記空隙を含む空間内に備えられていることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

スイッチ及びESD保護素子

【課題】低消費電力のスイッチ及びESD保護素子を提供する。

【解決手段】本発明の例に関わるスイッチは、基板10上に設けられた第1及び第2の電極11,12と、第1の電極11上に設けられたアンカー14と、アンカー14に支持され、アンカー14から第2の電極12上方まで延在し、導電体が用いられ、第2の電極12に対して上下方向に動く可動構造15と、可動構造15の端部に設けられ、第2の電極上方に配置される接点部16と、可動構造15上に設けられ、可動構造15を構成する材料と応力差を有し、接点部16を第2の電極12に向かって反らせる調整膜18と、可動構造16の周囲を取り囲むように基板10上に設けられ、調整膜18に接触し、駆動電極として機能するキャップ20と、を具備する。

(もっと読む)

集積回路において静電放電を防止し放散する方法

【課題】従来技術の素子よりも少ない構成部品しか必要とせずおよび/または複雑でない構造を備え、集積回路がオンまたはオフになったときにそれを保護することを可能にし、保護される集積回路に対する非常に低い寄生容量を有する、かさ高にならない保護素子を提供すること。

【解決手段】少なくとも1つの集積回路を静電放電から保護するための素子(100)は、少なくとも、イオン化可能金属部分(106)と、イオン化可能金属部分に接して配置され、前記イオン化可能金属部分の金属と同様の性質の金属イオンを有する固体電解質(104)と、この固体電解質に電気的に接続された電極(102)とを備えており、固体電解質中の金属イオン濃度が、固体電解質中の金属イオン飽和濃度より小さい。

(もっと読む)

半導体装置

【課題】高耐圧を有する半導体装置において、製造工程を追加することなく、求められる機能を満たしたESD保護素子を提供する。

【解決手段】高耐圧を有する半導体装置をノイズやサージから守るESD保護素子において、ゲート電極33の両端に形成されたドレイン側でないLOCOS酸化膜21bの下に形成される拡散層14bの導電型をP型にすることにより、ドレインの表面ブレークダウンにより生じる電流がソース側N型高濃度拡散層15a下を流れる量を制限して、寄生NPNバイポーラ動作の保持電圧を高くすることが可能となり、工程追加無しに、内部素子に必要な拡散層や絶縁膜を用いてESD保護素子を設定することが可能となる。定常状態においてはオフ状態にあるが、サージやノイズが半導体装置に印加された場合には、内部素子が破壊に至る前にESD保護素子が動作して大電流を放出し、その後再びオフ状態に戻るという機能を満たす。

(もっと読む)

半導体装置

【課題】集積回路の高性能化、小型化を妨げることなく、集積回路のESD(静電気放電)に対する耐性を向上する。

【解決手段】2つの入出力端子の間に保護回路104が挿入されている。ESDが発生したとき、保護回路によって2つの入出力端子を短絡して、回路103に過電圧が印加されることを防ぐ。回路は、接続配線110,120を介して、入出力端子に電気的に接続されている。回路は、接続配線との複数の電気的な接続部を有しており、各接続部と入出力端子間の配線抵抗が等しくなるように、接続配線を形成する。これにより、ESDが発生しても、1つの接続部に電圧が集中して印加することが回避されるため、ESDによって回路が破壊される確率が低減される。

(もっと読む)

半導体装置

【課題】内部に流入するイミュニティノイズを接地端子に逃がすことで、イミュニティ耐性を向上させる半導体装置を提供する。

【解決手段】静電気保護素子51の一端及び抵抗体Rの一端は、電源端子または基準電源端子に接続され、静電気保護素子51の他端は、グランド端子に接続され、静電気保護素子51は、ダイオード、PMOSトランジスター、NMOSトランジスター、バイポーラトランジスター及びサイリスター構造を有するもののいずれか1つである。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、寄生容量を充放電する変位電流が発生することを抑制し、回路の誤動作を防止する。

【解決手段】電界緩和層2dと支持基板2におけるp型の部分2eとによって構成されるPN接合により、高耐圧ダイオードを構成する。これにより、高耐圧ダイオードを構成するPN接合部に空乏層が形成され、この空乏層によって各部位および各支持台31a、31bを独立した電位に固定することが可能となる。このため、dv/dtサージによる変位電流の発生を抑制することが可能となる。また、変位電流が発生したとしても、支持台31aを通じて変位電流を引抜ける。このため、変位電流が低電位基準回路部LV内に流れることを防止することが可能となり、変位電流によって回路の誤動作が生じることを防止できる。

(もっと読む)

1 - 20 / 146

[ Back to top ]