Fターム[5F038BH05]の内容

Fターム[5F038BH05]に分類される特許

1 - 20 / 639

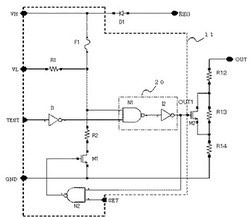

半導体集積回路

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】本発明は、電圧測定回路における電流損失を抑え、異常動作の場合であっても電圧測定回路が破壊されない半導体装置を提供する。

【解決手段】

本発明は、第1導通電極と、第2導通電極とを有する半導体スイッチ素子10と、半導体スイッチ素子10の第1導通電極および第2導通電極間の電圧を測定するための電圧測定回路31とを備える半導体装置101である。電圧測定回路31は、半導体スイッチ素子10と並列に接続され、半導体スイッチ素子10の導通方向に印加される電圧を所定値に制限するダイオード素子11と、ダイオード素子11に直列に接続された制御用スイッチ7と、半導体スイッチ素子10がオフ状態のときに制御用スイッチ7をオフ状態にし、半導体スイッチ素子10がオン状態のときに制御用スイッチ7をオン状態にするスイッチ制御部15とを含む。

(もっと読む)

集積回路

【課題】静電破壊に対する耐性を向上させることが可能な集積回路を提供する。

【解決手段】バイアス回路4は、増幅トランジスタM1が増幅を行えるようにバイアス電圧BA1を設定し、静電保護回路2は、増幅トランジスタM1にかかる電圧に基づいて、増幅トランジスタM1がオフするように増幅トランジスタM1のバイアス電圧BA1を設定し、切替回路3は、電源の供給状態に基づいて、増幅トランジスタM1のバイアス電圧BA1を切り替える。

(もっと読む)

電気光学装置および表示装置

【課題】静電破壊が起こりにくく、しかも、静電破壊が起こったときにショートが起こりにくい静電保護回路を有する電気光学装置およびそれを備えた表示装置を提供する。

【解決手段】電気光学装置は、絶縁基板上に、複数の画素を有する画素領域と、画素領域の周縁に形成されたフレーム領域とを備えている。フレーム領域は、画素を駆動する駆動回路と、制御信号線と、共通電位と同一電位の共通電位電極と、駆動回路を保護する静電保護回路とを有している。静電保護回路は、制御信号線と共通電位電極との間に互いに直列に接続されるとともに、薄膜トランジスタで構成された複数のダイオードを有している。本技術の表示装置は、上記の電気光学装置を表示パネルとして備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

ESD耐量検証方法及びESD耐量検証装置

【課題】 ESD耐量の低いパス及びその原因素子を安易且つ良好に特定できる検証方法及び検証装置を提供する。

【解決手段】 設計用回路データから2つの検証対象端子とその間に接続される検証対象素子を特定し、電流方向を設定し、検証対象素子の夫々を識別情報、電流方向別の特性情報及び耐量情報を記憶した素子シンボル情報を備える素子シンボルで表した等価回路データを作成し、2ノード間の特性情報及び耐量情報を記憶可能な分岐点シンボルを用い、検証対象端子に対応する分岐点シンボルを頂点とし、等価回路データをツリー構造データに変換し、素子シンボル情報に基づいて分岐点シンボル情報を作成し、頂点の分岐点シンボルの耐量情報が基準耐量以下の場合に、耐量情報に基づいて耐性が最も低い最低耐量経路と耐量制限シンボルを特定し、当該耐量制限シンボルに対応する設計用回路データの素子を特定する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】ホールド電圧が高いエミッタ・ベース短絡型の保護素子が設けられた半導体装置を提供する。

【解決手段】半導体装置1は、基板10と、前記基板上に形成された第1導電形の半導体層11と、前記基板と前記半導体層との間に形成された第1導電形の埋込層13と、前記半導体層上に形成された第2導電形のウェル14と、前記半導体層上であって、前記ウェルから離隔し、前記埋込層の直上域に形成された第1導電形の第1コンタクト層15と、前記ウェル上に形成された第2導電形の第2コンタクト層16と、前記ウェル上であって、前記第1コンタクト層と前記第2コンタクト層との間に形成された第1導電形の第3コンタクト層17と、前記埋込層と前記第1コンタクト層との間に形成され、前記第1コンタクト層に接した第1導電形のディープ層18と、を備える。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させることなく、ゲート−ソース間のESD耐量を向上させることのできる半導体装置を提供すること。

【解決手段】ポリシリコンゲート層を利用して形成したツェナーダイオードをESD耐量を向上させるために、並列接続させる構造を有する半導体装置とするものであって、ストライプ状または矩形状のツェナーダイオードを並列接続させて、それぞれ活性部内部に形成する半導体装置とする。

【選択図】 図3  (もっと読む)

(もっと読む)

ウェハ裏面のキャパシタを有する半導体デバイスを形成する方法

【課題】 ウェハ裏面のキャパシタを有する半導体デバイスの形成方法を提供する。

【解決手段】 本発明の方法は、その前面の活性シリコン層とその裏面のバルク・シリコン層との間に挿入された埋込み絶縁層を有する、SOI基板を準備するステップと、SOI基板の前面から埋込み絶縁層を貫通して延びる埋込みコンタクト・プラグを含む集積回路を、SOI基板の前記前面に形成するステップと、裏面エッチング・プロセスを実施してバルク・シリコン層内にトレンチを形成し、埋込みコンタクト・プラグの端部を埋込み絶縁層の裏表面に露出させるステップと、第1キャパシタ・プレートと、第2キャパシタ・プレートと、該第1及び第2キャパシタ・プレートの間に挿入されたキャパシタ誘電体層とを含むキャパシタをトレンチ内に形成するステップとを含み、第1キャパシタ・プレートは、埋込みコンタクト・プラグの露出した端部に接触するように形成される。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】静電気放電が印加されたときの熱破壊を抑制すること。

【解決手段】半導体装置1の半導体活性層16には、n型領域23とp型領域26とn型の埋込み領域30が形成されている。n型領域23は、カソード電極Kに電気的に接続している。p型領域26は、アノード電極Aに電気的に接続している。埋込み領域30は、半導体活性層16のうちのp型領域26の裏面側の少なくも一部を含むように形成されており、p型領域26の裏面に接触しているとともに、不純物濃度が半導体活性層16の不純物濃度よりも濃い。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】低消費電力化及び回路面積の削減を図れるようにした半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、電源端子と接地端子の間に接続されたMOSトランジスタと、MOSトランジスタのドレインとゲートの間に接続された第1のダイオードと、MOSトランジスタのドレインとゲートの間に第1のダイオードと互いの順方向が逆向きに直列に接続された第2のダイオードと、MOSトランジスタのドレインとゲートの間に第1及び第2のダイオードと直列に接続されたキャパシタとを備えている。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

半導体装置

【課題】積層チップシステムにおいて、各チップのIO回路の大きさを、そのドライブ能力やESD耐性能力を維持した上で、従来のサイズから縮小し、積層システムでは積層数に応じてIO数を変化させることができる半導体装置を提供する。

【解決手段】積層チップシステムにおいて、各チップは、各IO用の貫通ビア接続用パッド201に接続するIO回路202、スイッチ回路206にてIOチャネル207を構成し、このIOチャネル207を最大積層予定数のIOチャネル分まとめて接続してIOグループを構成し、このIOグループを1個以上持つ。各IO用の貫通ビア接続用パッド201は、貫通ビアにて別層のチップの同一位置のIO端子と接続される。インターポーザにおいては、実際の積層数が最大積層予定数に満たない場合はインターポーザ上で隣接するIOグループ内のIO用の接続用パッドが導体で接続されている。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

1 - 20 / 639

[ Back to top ]