Fターム[5F038BH11]の内容

Fターム[5F038BH11]の下位に属するFターム

入出力 (1,872)

熱 (378)

光 (13)

寄生効果(ラッチアップ等) (220)

誤動作(ソフトエラー、ノイズ等) (1,289)

Fターム[5F038BH11]に分類される特許

1 - 20 / 123

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

半導体素子の破壊を検知する検知回路

【課題】監視対象の素子の破壊を直接的に検知することを可能にする。

【解決手段】監視対象の半導体素子近傍にモニタ用配線を敷設する一方、所定のクロックを出力するクロック出力手段を当該モニタ用配線の一端に接続し、同モニタ用配線の他端に監視手段を接続する。そして、クロック出力手段からモニタ用配線へ出力されるクロックを伝播を監視手段に監視させ、クロックの伝播が途絶えたことを検出した場合に、監視対象の半導体素子の破壊が生じた旨を通知する破壊通知信号を出力させる。

(もっと読む)

半導体装置と制御手段とを備えるシステム、及び、半導体装置を流れる電流の制御方法

【課題】メイン素子に流れる電流に応じて適切に半導体装置を制御することができる技術を提供する。

【解決手段】半導体装置と制御手段とを備えるシステム。半導体装置の半導体基板には、メイン素子と、第1検出素子と第2検出素子が形成されている。制御手段は、第1検出素子の電流密度Id1と、第2検出素子の電流密度Id2と、係数K1と、係数K2から、Im=K1Id1+K2Id2の数式により得られる値Imに基づいて半導体装置を流れる電流を制御する。半導体装置を動作させたときに、メイン素子が形成されている領域の中で、第1検出素子の温度に近い温度となる領域の面積が面積SHであり、第2検出素子の温度に近い温度となる領域の面積が面積SLである。係数K1と係数K2の比K1/K2が、面積SHと面積SLの比SH/SLと略等しい。

(もっと読む)

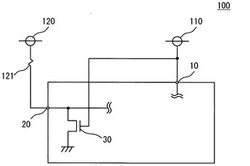

半導体装置

【課題】半導体素子が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断できる半導体装置を提供すること。

【解決手段】半導体装置100を構成するパワー半導体素子を小さな半導体素子1に分割し、この小さな半導体素子1にそれぞれ1本のボンディングワイヤ17を接続する。小さな半導体素子1が短絡破壊したとき、破壊した小さな半導体素子1に接続するワイヤ17(ヒューズの役割をさせる)を溶断し、且つ、制御回路30からオフ信号を健全な半導体素子1に与える。このようにして、半導体装置100が短絡破壊したとき、ヒューズを設けることなく、主電流を遮断することができる。

(もっと読む)

パワーモジュール

【課題】センス電流を抵抗で検出する場合であっても、カレントミラー回路を用いて検出する場合であっても、誤検出や電流検出精度の低下を起こさないパワーモジュールを提供する。

【解決手段】IGBT1の電流センス素子STのセンスエミッタにエミッタが接続されたトランジスタQ5と、トランジスタQ5のコレクタに一方端が接続され、他方端が共通接続部BPに接続された電流検出抵抗SRとを有し、トランジスタQ5のベースがGNDに接続された電流検出回路C3と、電流検出抵抗SRによって発生する共通接続部BPを基準とした電位差を電流検出電圧Vsとして検出し、所定の閾値電圧との比較を行い、両者の大小関係によってIGBT1に過電流が流れているか否かを判定する。

(もっと読む)

半導体装置

【課題】ボンディングパッドの直下の酸化膜を壊すことなくウエハテストを行う。

【解決手段】半導体基板9と、半導体基板9上に形成された5層の配線層と、前記5層の配線層のうち、最上層の第5配線層5に形成され、それぞれ一部が露出した複数のボンディングパッド5eと、半導体基板9上に形成され、かつボンディングパッド5eの下において平面視でボンディングパッド5eと重なる位置に配置され、さらにボンディングパッド5eと電気的に接続されたトランジスタ素子等の能動素子と、を有しており、ボンディングパッド5eの直下には、5層の配線層のうちのいずれの配線層も設けられていない緩衝膜7が形成されている。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法及びプログラム

【課題】半導体集積回路において、シールド配線を配置することで配線間のクロストークの影響を削減するとともに、配置したシールド配線の電位を安定化させること。

【解決手段】半導体集積回路の設計方法は、コンピュータが、半導体集積回路の配線パターンにおいて、配置済の信号配線に対して複数のシールド配線を配置する工程と、前記複数のシールド配線のそれぞれを電源配線に接続する工程と、前記複数のシールド配線を相互に接続する工程と、前記複数のシールド配線のうちの電源配線に接続されていないものを除去する工程と、を含む。

(もっと読む)

半導体装置

【課題】ヒューズの線幅の縮小化を図ることが可能な半導体装置を提供する。

【解決手段】この半導体装置1では、ヒューズFUに隣接してダミーヒューズDFUを設け、ヒューズFUおよびダミーヒューズDFUの各々の配線幅を最小線幅に設定し、ヒューズFUおよびダミーヒューズDFUの間隔を最小間隔に設定した。したがって、OPCによってヒューズFUおよびダミーヒューズDFUの露光条件が最適化されるので、最小線幅のヒューズFUを形成することができる。

(もっと読む)

ボルテージレギュレータ

【課題】短絡電流を正確に設定できるボルテージレギュレータを提供する。

【解決手段】過電流保護回路の短絡電流の電流値を決定する回路として、電流を電圧に変換する抵抗を用いず、Nchデプレッション型トランジスタのゲートとドレインを接続して非飽和状態で動作させる回路を用いて電流で制御する回路を備えた。Nchデプレッション型トランジスタは検出用トランジスタとプロセスばらつきが連動するためトリミングを行うことなく短絡電流を正確に設定することが出来る。

(もっと読む)

シリコン貫通ビアのためのESD/アンテナダイオード

概略を述べると、アンテナダイオードが、少なくとも一部がTSVの周囲の排他的区域内に形成され、金属1層の導電体を介してTSV(シリコン貫通ビア)に接続されている。それと同時に、TSVは、排他的区域の外側に位置する1又は複数のトランジスタのゲートポリ又は拡散領域に接続している。 (もっと読む)

半導体装置

【課題】シールド膜を設けることなく、最上層配線層に形成された信号電位配線を治具の接触による破損から保護する。

【解決手段】半導体基板と、半導体基板上に形成され、半導体素子が形成される半導体層及び前記半導体素子に接続される信号配線が形成される下層配線層と、半導体層及び前記下層配線層より上層に形成され、動作時に電位が変化しない固定電位配線、動作時に電位が変化しうる上層信号電位配線、及び、固定電位が入力される固定電位用ボンディングパッド、及び信号電位が入出力される信号電位用ボンディングパッドが形成された最上配線層と、を備えている。固定電位配線及び固定電位用ボンディングパッドの少なくとも一部は、下層に半導体層及び下層配線層のうち少なくとも一方が形成されることにより、信号電位配線及び前記信号電位用ボンディングパッドの最も高い表面より高く形成されている。

(もっと読む)

電気ヒューズ回路及び電気ヒューズ回路の動作方法

【課題】確実に切断を行うことのできる、電気ヒューズ回路及び電気ヒューズ回路の動作方法を提供する。

【解決手段】一端で電源に接続され、他端から切断用電圧を出力する、保護素子と、一端で前記保護素子の他端に接続され、他端でグランドに接続された、電気ヒューズと、前記電気ヒューズと前記グランドとの間に介装され、前記電気ヒューズに流れる電流の有無を切り替える、切断用トランジスタとを具備する。前記保護素子の他端は、前記切断用トランジスタのゲートに接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

入力回路および半導体集積回路

【課題】電磁波による誤動作を低減することのできる入力回路および半導体集積回路の提供を図る。

【解決手段】入力端子2に供給される入力信号を受け取る入力回路10aであって、一端が前記入力端子に接続された容量42と、前記入力信号を、当該入力信号と同じ正論理の信号に変換し、前記容量の他端に供給して駆動する容量駆動回路51,52,41と、を有するように構成する。

(もっと読む)

半導体装置

【課題】検知セルからのセンス電流を正確に検出することができる半導体装置を提供する。

【解決手段】半導体装置は、第1および第2主表面を有する半導体基板80と、半導体基板80に形成された主電流スイッチセル32および電流検知セル31と、電流検知セル31に接続されると共に、ボンディングワイヤが接続される外部配線接続部とを備え、主電流スイッチセル32は、エミッタ電極17と、金属コレクタ電極19と、ゲート電極16とを含み、電流検知セル31は、エミッタ電極27と、金属コレクタ電極19と、ゲート電極16とを含み、外部配線接続部49は、半導体基板上に形成された抵抗部および検知用ボンディングパッドとを含む。

(もっと読む)

改善されたESD保護回路を有する増幅器

【解決手段】改善されたESD保護回路を有する増幅器が述べられる。典型的な一設計では、この増幅器は、トランジスタ、インダクタ、及びクランプ回路を含む。トランジスタは、パッドに結合されたゲートを有し、増幅器についての信号増幅を提供する。インダクタは、トランジスタのソースに結合され、トランジスタについてのソース・ディジェネレーションを提供する。クランプ回路は、トランジスタのゲートとソースとの間に結合され、トランジスタのESD保護を提供する。クランプ回路は、トランジスタのゲートとソースとの間に結合された少なくとも1つのダイオードを含み得る。クランプ回路は、大電圧パルスがパッドに印加された際に、インダクタを介して電流を導き、インダクタの両端に電圧降下を生じさせる。 (もっと読む)

単方向金属酸化膜半導体電界効果トランジスターとその応用

【課題】単方向金属酸化膜半導体電界効果トランジスターとその応用を提供する。

【解決手段】本発明は、金属酸化膜半導体電界効果トランジスター(MOS)、電流検出回路、および、快速ターンオフ回路、からなる単方向金属酸化膜半導体電界効果トランジスター(UMOS)を提供する。電流検出回路は、MOSを流れる電流の方向を検出する。順方向電流が検出される時、快速ターンオフ回路は機能せず、MOSのチャネルが形成される。逆電流が検出される時、快速ターンオフ回路は有効で、MOSのチャネルは形成されない。このUMOSは、同期整流器に応用されて(これに限定されるものではない)、逆電流、又は、シュートスルー電流を検出することができ、快速的にMOSのチャネルをオフにすることができる。

(もっと読む)

半導体装置

【課題】本発明は、配線抵抗成分をセンス抵抗として利用しながら、過電流保護回路の検出精度を向上することが可能な半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、監視対象となる電流ラインの配線抵抗成分であるセンス抵抗Rsと、センス抵抗Rsでの降下電圧と所定の閾値電圧を比較して過電流保護信号Socpを生成する過電流保護回路OCPと、前記電流ラインの形成工程と同一の工程により、他の回路要素から電気的に分離して形成されたダミーラインの配線抵抗成分であって、センス抵抗Rsよりも大きな抵抗値を有するダミー抵抗Rdと;ダミー抵抗Rdの両端に各々接続されたダミーパッドT1、T2と;を集積化して成り、過電流保護回路OCPは、前記閾値電圧を調整するための閾値電圧調整部を有する構成とされている。

(もっと読む)

半導体装置

【課題】高周波パルス駆動が可能でスイッチング損失が小さく、過熱遮断動作後のゲート電流も小さい、パワーMOSFETの保護回路ならびに保護回路を有する保護回路内蔵パワーMOSFETを提供する。

【解決手段】 第1、第2、第3外部端子を備え、第1半導体チップをパッケージ内に実装し、前記第1半導体チップは第1ソース端子用パッドと第1ゲート端子用パッドと第3パッドを備え、前記第1半導体チップの裏面は前記第1外部端子に接続され、前記第1ソース端子用パッドは前記第3外部端子に接続され、前記第3パッドは前記第2外部端子に接続されている。

(もっと読む)

双方向スイッチ、及び半導体装置

【課題】オン抵抗を低減することのできる安定したスレッショールド電圧の双方向スイッチ、及び半導体装置を提供すること

【解決手段】本発明にかかる双方向スイッチは、P半導体基板1上に形成され、第1及び第2MOSスイッチM1、M2のドレインとなるNウェル領域2と、Nウェル領域2に設けられた第1トレンチ3内にゲート絶縁膜6を介して形成された第1ゲート電極71aと、Nウェル領域2に第1トレンチ3と離間して設けられた第2トレンチ3内にゲート絶縁膜6を介して形成された第2ゲート電極72aと、第1トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第1N+ソース領域9と、第2トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第2N+ソース領域10と、を備え、第1トレンチ3と第2トレンチ3との間の領域には、Nウェル領域2が形成されているものである。

(もっと読む)

1 - 20 / 123

[ Back to top ]