Fターム[5F038CA01]の内容

Fターム[5F038CA01]の下位に属するFターム

素子配置 (1,574)

回路ブロック配置 (981)

領域設定 (1,104)

対称配置 (380)

分散配置 (308)

熱的結合に関するもの (208)

寄生防止 (242)

電極パッド配置 (1,058)

Fターム[5F038CA01]に分類される特許

1 - 20 / 66

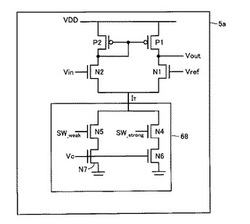

半導体装置

【課題】レイアウト面積を大きくすることなく、差動対を高速/高消費電流と、低速/低消費電流の両方で動作させることができるようにした半導体装置を提供する。

【解決手段】差動回路5aは、差動対トランジスタN1,N2と、差動対トランジスタN1,N2に流れる電流量が少なくとも2つのレベルで切替わるように、切替可能なテール電流を供給するテール電流源68とを備える。差動対トランジスタN1,N2は、差動対トランジスタN1,N2に流れる電流の減少に伴って、σ(ΔI/gm)の値が単調に減少する特性を有する、ただし、σは標準偏差、ΔIは、差動対トランジスタN1,N2の電流量の差分、gmは、差動対トランジスタN1,N2のトランスコンダクタンスを表わす。

(もっと読む)

半導体装置

【課題】マルチフィンガーFETセル内のループ発振を抑制させ、かつチップ面積の増大を抑制する。

【解決手段】ユニットフィンガーの並列接続からなるマルチフィンガー単位FETセルと、マルチフィンガー単位FETセルのゲートフィンガーを並列接続する指定ゲートバスラインと、指定ゲートバスラインに接続されたゲート引き出しラインとを備え、ゲート引き出しラインと指定ゲートバスラインの接続点をマルチフィンガー単位FETセル内の中心からずらすことによって、接続点の一方に接続されたゲートフィンガー数が、他方に接続されたゲートフィンガー数よりも多くする。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

半導体装置

【課題】RDRに従い設計され、活性領域と電源配線との境界部や周辺部における不具合の発生が抑制された、小型化かつ高集積化された半導体装置を提供する。

【解決手段】少なくとも1つのスタンダードセル内における半導体基板SBの主表面に形成される第1導電型の機能素子用不純物領域Apと、電源電位が印加される第2導電型の電源電位用不純物領域Anとを備える。半導体基板SBの主表面上に形成され、かつ半導体基板SBの主表面に達する貫通孔SCTHを有する絶縁層II1、II2と、絶縁層II1、II2の貫通孔内に形成されたコンタクト用導電層PCLとを備える。上記機能素子用不純物領域Apと電源電位用不純物領域Anとをまたぐように形成されるコンタクト用導電層PCLを通じて電気的に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】 ダイシングに伴う膜剥れの防止および異常放電防止に好適な半導体装置を提供する。

【解決手段】 半導体装置はスクライブ領域003とIC領域004からなり、スクライブ領域003の層間絶縁膜002には少なくとも一つの分離溝007が設けられ、分離溝007の両側の側壁にはプラグ金属膜からなるサイドウォール011が形成され、少なくともサイドウォールを覆うパッシベーション膜を設ける構成とした半導体装置とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 電力等の信号の合成効率が高く、チップ占有面積を低減可能な半導体装置および半導体装置の製造方法を提供する。

【解決手段】 本発明の半導体装置10は、電極パッド11と、複数の信号伝送電極12a、12bおよび12cと、複数の伝送線路13、14および15とを有し、前記電極パッド11と前記各信号伝送電極12a、12bおよび12cとは、前記各伝送線路13、14および15により電気的に接続され、前記複数の伝送線路13、14および15の少なくとも一本は、その線路長が他の伝送線路14以上であり、前記線路長が他の伝送線路以上である伝送線路13および15は、その一部または全部が空中配線され、前記空中配線された伝送線路13aおよび15aが、マイクロストリップラインであることを特徴とする。

(もっと読む)

半導体装置

【課題】アンチヒューズ素子として用いられる半導体装置において、導通状態における抵抗値のばらつきを低減することで、アンチヒューズ素子として安定した動作を実現する。

【解決手段】半導体基板1の主面上に形成されたアクティブフィールド11と、アクティブフィールド11の表面に形成されたゲート絶縁膜5を介してアクティブフィールド11上に設けられたゲート電極12と、を有し、ゲート電極12は、半導体基板2の主面を平面視する方向から見て、アクティブフィールド11に周囲を囲まれるように配置されているとともに、ゲート電極12の周縁部がゲート電極12の周囲に配置されたアクティブフィールド11に重なって重なり領域13を形成するように配置されている。

(もっと読む)

半導体集積回路装置

【課題】フリップチップ構造を有する半導体集積回路装置において、パッドからチップ内部素子へ加わる応力の影響に起因するタイミング信頼性の劣化を低コストで防止する。

【解決手段】フリップチップ構造を有する半導体集積回路装置において、応力の影響を受ける半導体チップ101の外周列におけるパッド102の構造及び配置位置等について、応力の影響に起因するLSIの動作不具合が発生しにくいように予めレイアウトする。

(もっと読む)

電気回路

【課題】物理長の異なる複数の伝送線路において、電気長を等しくする。

【解決手段】半導体基板1上の薄膜絶縁体上に形成された物理長の異なる複数の伝送線路A、Bのうち、物理長の長いほうの伝送線路において、伝送線路を構成する信号線メタルと半導体基板1との間に低誘電率絶縁膜3を挟むことによって信号伝搬速度を速くした領域を設け、この低誘電率絶縁膜3を挟んだ領域の長さを伝送線路Aの物理長に応じて調整することによって、すべての伝送線路の電気長を等しくする。

(もっと読む)

半導体装置

【課題】半導体チップのチップサイズを縮小化することができる技術を提供する。特に、LCDドライバを構成する長方形形状の半導体チップにおいて、短辺方向のレイアウト配置を工夫することにより、半導体チップのチップサイズを縮小化することができる技術を提供する。

【解決手段】LCDドライバを構成する半導体チップCHP2は、複数の入力用バンプ電極IBMPのうち一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されている一方、複数の入力用バンプ電極IBMPのうち他の一部の入力用バンプ電極IBMPの下層には入力保護回路3a〜3cが配置されずにSRAM2a〜2c(内部回路)が配置されている。

(もっと読む)

CAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体

【課題】本発明は、高速にインダクタの巻き数を求めることが出来るCAD装置、インダクタの巻き数求め方法、プログラム及び記憶媒体を提供することを課題とする。

【解決手段】CADデータ表示部22が表示したレイアウト表示上で、インダクタ位置指定部23によって、ユーザにインダクタの位置を指定させる。この頂点抽出部24は指定位置の範囲内の頂点の数を求め、巻き数計算部25はこの頂点の数からインダクタの巻き数を算出する。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。非重畳領域下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、ゲートパッド部から保護ダイオードまでの距離が、ソースパッド部から保護ダイオードまでの距離より小さくなる位置に保護ダイオードを配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方にはトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、ソース電極層を基板水平方向に流れる電流の経路において、素子領域内で抵抗の偏りが発生する問題もあった。

【解決手段】電極構造を2層とし、2層目のゲート電極層(ゲートパッド部)の下方にトランジスタセルおよび1層目のソース電極層を配置する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介してゲート電極と接続する。ゲートパッド部下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減できる。またソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

絶縁ゲート型半導体装置

【課題】基板の一主面側に全ての外部接続手段が接続される絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置される構造では、トランジスタセルおよびソース電極層が配置できず、基板内部の抵抗が大きい問題があった。

【解決手段】電極構造を2層とし、保護ダイオードは素子領域外で素子領域に隣接し、素子領域外周の、主な電流経路に垂直となる辺に隣接して配置する。また、2層目のゲート電極層(ゲートパッド部)の少なくとも一部に保護ダイオードとの非重畳領域を形成する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介して保護ダイオードおよびゲート電極と接続する。ゲートパッド部の下方にトランジスタセルおよび1層目のソース電極層を配置する。これにより基板内を流れる電流の抵抗が小さくできる。

(もっと読む)

半導体装置、セルライブラリおよび半導体集積回路の設計方法

【課題】回路設計に要する期間を短縮することが可能な機能セルとその機能セルを含む半導体装置およびその機能セルを用いた半導体回路設計方法を提供する。

【解決手段】半導体装置は、同一の論理回路機能を実現し、互いに電気的特性の異なる第1および第2の機能セル3a、3bを備える。第1の機能セル3aは第1の外部接続配線を含む。第2の機能セル3bは第2の外部接続配線を含む。第1の機能セル3aの外周の形状は、第2の機能セル3bの外周の形状とほぼ同一である。第1の外部接続配線の第1の機能セル3a平面内における位置は、第2の外部接続配線の第2の機能セル3b平面内における位置とほぼ同一である。

(もっと読む)

静電気放電保護素子

【課題】 SOI基板上に形成され、ESD耐性の高い半導体装置を提供する。

【解決手段】 SOI基板上に形成されたMOSトランジスタ2と、MOSトランジスタのソース電極及びドレイン電極間に少なくとも一つのダイオード3、及び抵抗4が直列接続されており、ダイオードと抵抗の接続点にMOSトランジスタ2のゲート電極5を接続することによってESD耐性を高める。さらに、ダイオードと抵抗の接続点と、ボディコンタクト領域6とを接続することによって、より高いESD耐性を得ることができる。

(もっと読む)

集積回路

【課題】集積回路において、入力保護回路セルとクランプ回路を含む電源セル間の寄生抵抗を小さくし、ESD強度の低下を補うためにダイオードサイズをダイオード単体のESD強度以上に大きくすることを抑え、入力保護回路のダイオードによる大きい入力容量成分、および直列抵抗の寄生抵抗成分により高周波信号電力が減衰するのを防ぐことを目的とする。

【解決手段】入力保護回路セルは、信号ピンに接続される入力端子7、高周波回路に接続されるとともに、入力端子7とノード60により接続される出力端子8、ノード60とVDD間に設けられ、ノード60からVDDへ電流を流すダイオード1、ノード60とGND間に設けられ、GNDからノード60へ電流を流すダイオード2を備える。また、VDDとGND間において、ダイオード1およびダイオード2と並列に接続されるクランプ回路4を備える。

(もっと読む)

半導体ウェハ

【課題】半導体ウェハに、細長い同一形状の半導体チップを配置したときの、半導体ウェハの周縁部の未使用部分を減らす。

【解決手段】細長い同一形状の半導体チップ3a、4aを、半導体ウェハ10aに配置する。半導体ウェハ10aの中央部に、同じ向きに揃えた半導体チップ3aの列を配列する。これが第1グループとなる。第1グループの上下の周縁部に、半導体チップ4aを、半導体チップ3aの向きとは90度異なる向きに配置する。半導体チップ4aは、その長辺が半導体チップ3aの短辺に隣接するように配置されている。

(もっと読む)

インダクタおよびその製造方法

【課題】インダクタを形成する導体において実質的な直列抵抗成分の増加を防止すると共に、導体間容量の増加を低減することができる。これらのことから、Q値を向上させたインダクタおよびその製造方法を提供する。

【解決手段】インダクタ10は、平板状の基板とスパイラル形状の導体11とを備えている。導体11が形成された形成面は、基板の主面に対して実質的に平行である。導体11では、形成面に対して水平な方向において等間隔であり、外側に位置する部分の方が内側に位置する部分よりも幅広且つ肉薄であり、形成面に対して垂直な方向においては上面及び下面の少なくとも一方の面が周回毎に相異なる位置に存在している。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaN系あるいはGaAs系FET用エピでは、バッファ層耐圧を向上させるために最近ではバッファ層に高抵抗のエピを用いる傾向にある。しかし、微細ゲートのパターニングのための電子ビーム露光によるリソグラフィーの際、チャージアップ現象が生じるという問題がある。

【解決手段】金属配線によって電子が放電する経路を形成する。すなわち、FETを作製するウエハ上の各チップの周辺部のスクライブラインあるいはエッチカットする部分に相当する部分に金属配線を配し、電子線にとってウエハ上で陽極あるいは接地導体となる部分とその金属配線が金属で接続されており、さらにチップ内においてFETのソース電極がチップ周辺の金属配線と金属で接続されるようにした。

(もっと読む)

1 - 20 / 66

[ Back to top ]