Fターム[5F038CA02]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 素子配置 (1,574)

Fターム[5F038CA02]に分類される特許

1 - 20 / 1,574

半導体集積回路

半導体装置

半導体装置

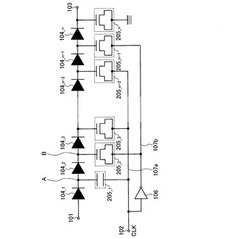

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

半導体装置及びトリミング方法

【課題】ヒューズ素子の列数増に伴うトリミング時間の伸長を抑制する。

【解決手段】x方向に延伸する接地配線Gと、接地配線のy方向の一方側に設けられたヒューズ素子領域Aにx方向に沿って3列に並べて配置され、かつそれぞれの一端が接地配線Gに共通に接続される複数のヒューズ素子と、ヒューズ素子領域Aを挟んで接地配線Gの反対側に設けられ、ヒューズ素子領域Aに配置された複数のヒューズ素子それぞれの他端と接続される救済回路とを備え、上記複数のヒューズ素子は、それぞれ1つの欠陥選択線を示すアドレス情報を記憶する複数のヒューズ素子グループに所定個ずつグループ化され、同一のヒューズ素子グループに属する所定個のヒューズ素子は、同一列に配置されることを特徴とする

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

電源制御装置、電源制御装置の制御方法、およびプログラム

【課題】多様な信号規格の処理に対応する半導体集積回路において、様々な周期性の違いに伴いタイミングと時間幅が変わるアイドル状態に対応した電源制御を適用し、消費電力を低減する。

【解決手段】処理状態と待機状態とを周期的に繰り返して処理を行う半導体集積回路の電源ドメインを制御する電源制御装置であって、待機状態の発生期間および発生間隔を含む周期的特徴情報を取得する周期情報取得部103と、電源ドメインが待機状態における待機電圧から半導体集積回路が動作可能となる電圧へ復帰するまでに要する復帰時間と対応付けられた待機電圧候補から、発生期間よりも復帰時間が短くなる待機電圧を電源制御情報として設定する電源制御情報設定部104と、電源制御情報に従って発生期間における電源ドメインの待機電圧を制御する電源制御部105とを備える。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体記憶素子及び半導体記憶装置

【課題】LSI素子の性能劣化及びヒューズ素子の欠陥の増加を抑制できる半導体記憶素子及び半導体記憶装置を提供する。

【解決手段】半導体記憶素子100は、第1ヒューズ線111と、第1ヒューズ線111と並列接続された第2ヒューズ線112とを有し、切断されているか否かによって2値のデータを保持するヒューズ素子110と、一端がワード線130に接続されており、ヒューズ素子110に電流を流すか否かを選択する選択素子120と、を備える。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体装置

【課題】配線間の寄生容量を削減可能にした半導体装置を提供する。

【解決手段】X方向に配列する複数のトランジスタについて、夫々が、対応するダミーゲートDG1,DG2を挟む複数のソース拡散層S1,S2に接続する第2及び第3の金属配線M12,M13は、2つのS1,2つのS2に夫々接続する複数の第1のビアV1の両方を含む第1の幅L1と、V1を含まず、L1よりも短い第2の幅L2と、を有する。ドレイン拡散層D1に接続する第1の金属配線M11と、M12との間、並びにM11及びM13の間の夫々は、L1に対応する第1のギャップSP1と、L2に対応する、L1よりも大きな第2のギャップSP2と、を有する。好ましくは、M11〜M13の夫々と第2のビアV2を介して接続される第4〜第6の金属配線M24〜M26の夫々は、L1よりも短い第3の幅L3を有する。

(もっと読む)

1 - 20 / 1,574

[ Back to top ]