Fターム[5F038CA13]の内容

Fターム[5F038CA13]に分類される特許

181 - 187 / 187

半導体集積回路の検査方法および半導体集積回路

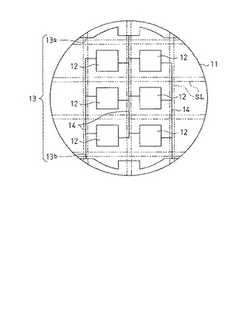

【課題】テスティング基板はもとより、検査後の後処理等も不要としながら、より簡易且つ的確に半導体ウエハ上の集積回路を検査することのできる半導体集積回路の検査方法およびその方法の実施に使用される半導体集積回路を提供する。

【解決手段】半導体ウエハ11上に形成されている複数の集積回路12を検査するに先立って、同半導体ウエハ11上の上記複数の集積回路12が形成される領域を除く領域に、給電パッド13と、この給電パッド13および上記複数の集積回路12の各給電部を電気的に接続する給電配線14とを予め形成、敷設しておく。そして、給電パッド13に所定の電圧を印加することにより、上記給電配線14を通じて上記半導体ウエハ11上の各集積回路12に対する通電試験を行う。

(もっと読む)

半導体装置の製造方法,半導体装置、エッチング条件の設定方法、導電膜除去条件の設定方法、及びレチクル

【課題】 導電膜が正常にパターニングされて配線が形成されていることを、少ない労力で確認することができるようにする。

【解決手段】 層間絶縁膜8上に導電膜を形成する工程と、前記導電膜をパターニングすることにより、チップ領域1aに配線10a〜10cを形成すると共に、スクライブライン1b上に、複数のダミー配線31〜33を互いに平行に形成する工程と、複数のダミー配線31〜33相互間の抵抗値を測定する工程とを具備する。最外側に位置するダミー配線31,33それぞれに接続するパッド34,35を形成し、このパッド34,35に抵抗計の端子を接触させてもよい。

(もっと読む)

トランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子

【課題】 トランジスタの電気的特性に異常がある場合に、その不良解析に要する時間を短縮することができるようにしたトランジスタの製造プロセス評価方法及び、トランジスタの製造プロセス評価素子を提供する。

【解決手段】 ウエーハWに形成されたICチップ100に含まれる代表的なMOSトランジスタ1の製造プロセスを評価するための評価素子10であって、MOSトランジスタ1と同一の製造プロセスによってウエーハWに形成された通常のMOSトランジスタ10aと、この製造プロセスからチャネルドープ工程だけを除いた不完全製造プロセスによって当該ウエーハWに形成されたネイティブトランジスタ10bと、を備えたものである。通常のMOSトランジスタ10aの閾値等に異常があった場合に、その値とネイティブトランジスタ10bの閾値等とを比較することで、その原因がチャネルドープ工程に有るか否かを容易に判断することができる。

(もっと読む)

プラズマチャージ評価基板、プラズマチャージ評価方法及び半導体装置の製造方法

【課題】少ない労力でプラズマチャージ量が基準値より多いか否かを評価することができるようにする。

【解決手段】プラズマチャージ評価基板を、半導体装置の製造工程で使用されるプラズマに曝露する工程と、プラズマチャージ評価基板を調べることにより、プラズマが基板に与えるプラズマチャージ量を評価する工程とを具備する。プラズマチャージ評価基板は、半導体基板1に形成された放電領域1aと、半導体基板1上に形成された層間絶縁膜2と、層間絶縁膜2に形成され、放電領域1a上に位置する接続孔2aと、層間絶縁膜2上に形成されたアンテナ用導電膜3と、層間絶縁膜2上に形成され、接続孔2aを介してアンテナ用導電膜3と放電領域1aとを接続するヒューズ用配線4とを備える。ヒューズ用配線4が溶断している場合には、プラズマチャージ量が基準値より多いと評価する。

(もっと読む)

半導体装置及びその製造方法

【課題】メッキ膜厚のウェハ面内均一性を向上させる。

【解決手段】本発明の例に関わる半導体装置は、メタル配線を用いた多層配線構造を有する半導体集積回路が形成され、各々が独立したチップになる複数のチップ領域11と、メタル配線を用いた多層配線構造を有し、複数のチップ領域の各々を取り囲む複数のチップリング12とを備え、複数のチップリング12は、互いに電気的に接続される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 保護回路により、プラズマ処理に伴うチャージングを抑え、かつエッチング工程に依存しない保護回路との切り離しを実現する半導体装置の製造方法及び半導体装置を提供する。

【解決手段】 素子分離領域11に囲まれた基板10上にゲート酸化膜12、ゲート電極13を形成する。スクライブ領域14では保護ダイオードD1のPN接合部15を形成する。層間絶縁膜16、ビア接続部17の形成後、第1層目の金属配線層181でゲート電極13に関係する回路配線の一部を形成する。その際、ゲート電極13とPN接合部15の一方端が結ばれる電荷放電経路用の接続構成CNTも同時に形成する。これにより、ゲート電極13は保護ダイオードD1と電気的に接続され、以降、プラズマ処理を伴う工程を経てもチャージングは回避される。

(もっと読む)

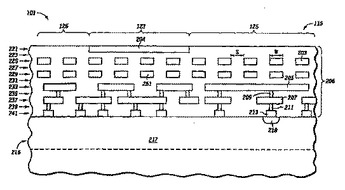

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

181 - 187 / 187

[ Back to top ]