Fターム[5F038CA13]の内容

Fターム[5F038CA13]に分類される特許

21 - 40 / 187

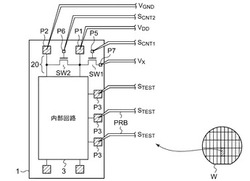

試験装置

【課題】プローブ検査においても、理想の電源環境を提供する。

【解決手段】試験装置は、ウエハ上に形成されたDUT1を試験する。電源補償回路20は、制御信号SCNT1、SCNT2に応じて制御されるソーススイッチSW1、シンクスイッチSW2を含み、それぞれがオンした状態において補償パルス電流ISRC、ISINKを生成し、補償パルス電流ISRCをメイン電源とは別経路からDUT1の電源端子P1に注入し、またはメイン電源からDUT1へ流れる電源電流から、補償パルス電流ISINKをDUT1とは別経路に引きこむ。電源補償回路20のうち、ソーススイッチSW1、シンクスイッチSW2を含む一部は、ウエハW上に形成される。ウエハには、ウエハ上に形成される電源補償回路20の一部に信号を印加するためのパッドP5〜P7が設けられる。

(もっと読む)

テストエレメントグループおよび半導体装置

【課題】保護ダイオードの有無に拘らず、素子特性を精度良く測定することの可能なテストエレメントグループおよびそれを備えた半導体装置を提供する。

【解決手段】テストエレメントグループ10において、電界効果型トランジスタからなるn個の素子DUT1〜DUTnが規則的に配置されている。ドレイン線DLおよびソース線SLがそれぞれ、全ての素子DUT1〜DUTnに対して共通化されており、その一方で、ウェル線WLが素子DUT1〜DUTnごとに1つずつ設けられている。選択対象の素子(選択素子DUTx)の素子特性を測定する際には、基板バイアス効果を利用して、非選択対象の素子(非選択素子DUTy)に流れるオフリーク電流を小さくする。

(もっと読む)

半導体装置、半導体テスタおよび半導体テストシステム

【課題】テストコストを増大させることなく、オープン不良を検出することができる半導体装置、これを試験するための半導体テスタおよびこの半導体テスタを用いた半導体テストシステムを実現する。

【解決手段】内部回路の出力ピンと電気的に接続された複数のパッドを有する半導体装置において、一端が共通電位に接続され、他端がパッドに接続された第1のスイッチ回路と、内部回路の出力ピンとパッドの間に設けられ、第1のスイッチ回路が接続されたパッドと試験時に半導体テスタのテスタピンが接続されるパッドとを電気的に接続するマルチプレクサとを備える。

(もっと読む)

半導体装置

【課題】外部ループバックテストが容易な半導体装置を提供する。

【解決手段】主面に形成された格子状のダイシングライン14、15と、ダイシングライン14、15で囲まれた矩形状格子に形成され、信号出力パッド24有する送信回路22と、信号入力パッド25を有する受信回路23と、送信回路22および受信回路23に入出力されるデータを処理する内部回路21とを有する複数の集積回路12と、ダイシングライン14、15上に形成され、信号出力パッド24と信号入力パッド25間を電気的に接続する信号配線26とを具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 半導体基板上に形成された半導体集積回路の、特にプローブ検査時間を短縮することができる検査工程を提供する。

【解決手段】 検査対象となる半導体基板には、半導体集積回路本体を含む回路領域2aと、それに隣接するスクライブエリアにTEG3aが形成され、回路領域2aには第1パッド電極5a、5bの列が、またTEG3aには第2パッド電極6の列が設けられる。ここでTEG3aに隣接している方の第1パッド電極5aが第2のパッド電極6に対向しないように配置される。このような状態の第1パッド電極5a、5bおよび第2パッド電極6にプローブ針8a、8b、9を接触させて半導体集積回路の検査とTEGの測定とを同時に行う。

(もっと読む)

半導体装置、半導体装置の製造方法、及び半導体装置の設計方法

【課題】TEGパターンより上の層を除去しなくてもTEGパターンを用いた検査を行うことができるようにする。

【解決手段】複数の配線層200,300,400は第1TEGパターン30の上に形成されている。複数の配線層200,300,400には、それぞれ配線242,342,442及び複数のダミーパターン224,324,424が形成されている。電極パッド444は、最上層の配線層400に形成されている。そして平面視において、第1TEGパターン30は、いずれの配線242,342,442及びダミーパターン224,324,424にも重なっていない。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】工程を追加せずに、アライメントマークの形成領域におけるゲート電極膜の残渣を低減する。

【解決手段】半導体装置の製造方法は、アライメントマーク10を有する第1領域R1と、抵抗体40が形成される第2領域R2と、ゲート電極15が形成される第3領域R3と、を主面1aに有する基板の主面1a上に、金属材料を含有するゲート電極膜11を形成する工程を有する。更に、第1及び第2領域R1、R2のゲート電極膜11を等方性エッチングにより除去する工程を有する。更に、ゲート電極膜11を除去した第2領域R2と、第3領域R3と、に導電膜(ポリシリコン膜13)を成膜する工程を有する。更に、導電膜を成膜する工程の後に、基板の主面1a上にフォトレジスト膜を形成し、アライメントマーク10をアライメントに用いて所定のパターンをフォトレジスト膜に転写する工程を有する。

(もっと読む)

半導体装置

【課題】ダイシング処理に起因する、チップ用パッド同士のショートを抑制することが可能な半導体装置を提供する。

【解決手段】半導体基板と複数の第1のパッドと、複数の第2のパッドとを備える半導体装置であり、第1のパッドは素子形成領域IMC内に、第2のパッドは素子形成領域IMCを取り囲むダイシングライン領域DLR内に形成される。ダイシングライン領域DLRには、第2のパッド同士が電気的短絡を生じさせやすい第1の領域SLRと、第2のパッド同士が電気的短絡を生じさせにくい第2の領域SURとを有している。第1の領域SLRに対向する位置に配置された一部の第1のパッドは、第2の領域SURに対向する位置に配置された残りの第1のパッドよりも、素子形成領域IMCの外縁の1辺BDLから離れて配置されている。

(もっと読む)

リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法

【課題】 リーク電流モニタ、リーク電流モニタ方法、及び、半導体装置の製造方法に関し、複数種類のデバイス特性をできるかぎり同じ構造のモニタで評価する。

【解決手段】 形状或いはしきい値電圧の少なくとも一方が異なる複数種類のトランジスタを異なった領域に同じ間隔で配置するとともに、前記複数種類のトランジスタの内、設計データにおける設置頻度の比を反映した数のトランジスタのゲート電極同士、ソース電極同士、及び、ドレイン電極同士を電気的に共通に接続する。

(もっと読む)

半導体装置

【課題】半導体チップを切り出す際に生じるばりによる半導体装置の歩留まりの低下及び信頼性の低下を防止し且つ半導体チップの取り数を向上させることができるようにする。

【解決手段】上面に複数のボンディングパッド14と複数の検査用パッドのパッド断片19とが形成された平面方形状の半導体チップにおいて、複数のパッド断片19は半導体チップの4辺のうちの対向する2辺に沿って形成されている。複数のボンディングパッド14は異なる2辺に沿って形成されている。

(もっと読む)

半導体ウエハとその製造方法、及び半導体チップ

【課題】半導体チップ領域内へのクラック伝播を抑制でき新規な構造を持つ金属リングを有する半導体ウエハを提供する。

【解決手段】半導体ウエハは、半導体素子が形成された第1半導体チップ領域と、半導体素子が形成された第2半導体チップ領域と、第1半導体チップ領域と第2半導体チップ領域との間に挟まれたスクライブ領域とを有し、第1半導体チップ領域は、第1半導体チップ領域に形成された半導体素子を囲む金属リングを含み、金属リングは、下側金属層と下側金属層上に重なる上側金属層とを含む複数の金属層で形成され、上側金属層の第1半導体チップ領域外側の側面が、下側金属層の外側の側面と揃っているか、または、下側金属層の外側の側面に対して第1半導体チップ領域内側に位置しているように、下側金属層上に上側金属層が重なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】層間絶縁膜が剥離しにくい半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法において、複数のデバイス領域がスクライブライン領域によって区画された半導体ウェーハ上に、層間絶縁膜内に配線及びビアが設けられた多層配線膜を形成する工程と、前記スクライブライン領域内に設定されたダイシング領域の一部に配置された前記多層配線膜及び前記半導体ウェーハを除去することにより、前記多層配線膜及び前記半導体ウェーハを前記デバイス領域毎に切り分ける工程と、を設ける。そして、前記多層配線膜を形成する工程において、前記スクライブライン領域における前記ダイシング領域を除く領域には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成し、前記ダイシング領域における前記層間絶縁膜の少なくとも上部には、前記配線及び前記ビアを上下方向に連結させたダミーパターンを形成しない。

(もっと読む)

半導体装置及び抵抗測定方法

【課題】製造時に発生する不具合を減少しつつ、回路面積を縮小可能なチップレイアウトを設計する。

【解決手段】本発明による半導体装置は、電流源接続用の第1パッド1と、一端が、第1パッド1に接続され、他端が、基板20と同じ導電型の拡散層21を介して基板20に接続されたヴィアチェーンと、電圧測定用の第2パッド2及び第3パッド3とを具備する。ヴィアチェーンは、第1パッド1及び第2パッド2が接続される第1配線4と、一端が第1配線4に接続され、他端が第3パッド3に接続された、抵抗測定対象となるヴィア又はコンタクト6とを備える。

(もっと読む)

半導体ウェハ

【課題】テストパッドの数を減らすことができ、かつウェハ状態で各トランジスタを個別にテストすることができる半導体ウェハを得る。

【解決手段】半導体ウェハ1内に複数の半導体装置2が行列状に配置されている。複数の半導体装置2を分離するためのダイシングライン3が設けられている。各半導体装置2は、複数のトランジスタ4を含む。複数のトランジスタ4のコレクタ(第1端子)に、それぞれ個別に複数のテストパッド5(第1テストパッド)が接続されている。複数のトランジスタ4のエミッタ(第2端子)に接地電極11が共通に接続されている。複数のトランジスタ4のベース(制御端子)に、ダイシングライン3内を通る配線6を介して、共通にテストパッド7(第2テストパッド)が接続されている。

(もっと読む)

半導体装置

【課題】 ウエハ上に形成された半導体チップを試験するときに、プローブの移動回数を最小限にし、試験時間を短縮する。

【解決手段】 半導体装置は複数の半導体チップを有し、各半導体チップは、試験信号に応じて試験される回路ブロックと、回路ブロックから出力される試験結果を、隣接する半導体チップの少なくともいずれかと試験結果出力端子とに出力するとともに、隣接する半導体チップから転送される試験結果を隣接する別の半導体チップと試験結果出力端子とに出力する転送回路とを有する。これにより、半導体チップの試験結果を隣接する半導体チップに順次に転送できるため、全ての半導体チップの試験結果を1つの半導体チップの試験結果出力端子から出力できる。

(もっと読む)

半導体装置の製造方法、半導体装置の検査方法、及び半導体装置

【課題】半導体装置の検査において、電極パッドの配列、スクライブ領域の幅に影響されることなくプローブカードを共有化し、プローブカードの製作費用を低減する。

【解決手段】基板20はチップ領域100、スクライブ領域200および電極パッド300を備えている。チップ領域100は基板20上の第1の方向に沿って、スクライブ領域200により互いに分離されるように並んでいる。電極パッド300は第1の方向に沿って周期性をもって配列している。接続用電極パッド320はチップ領域100に形成され、ダミー電極パッド340は少なくともスクライブ領域200に形成されている。電極パッド300の間隔はスクライブ領域200の幅よりも狭い。電極パッド300の配列と平行な方向における、チップ領域100とスクライブ領域200を合わせた幅は、電極パッド300間隔の整数倍である。

(もっと読む)

半導体装置およびその製造方法

【課題】ダイシング時に、アクセサリパターンが剥離することを抑制する。幅の狭いスクライブラインを使用して、1枚の半導体基板から得る半導体チップの個数を増加させる。

【解決手段】半導体装置は、半導体チップと、半導体チップの周囲に接するように設けられ層間絶縁膜とアクセサリとを有するスクライブラインとを有する。アクセサリは、層間絶縁膜上に設けられた層状の第1の部分と、第1の部分から層間絶縁膜の厚み方向の下方に向かって伸長する第2の部分と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 ダイシングに伴う膜剥れの防止および異常放電防止に好適な半導体装置を提供する。

【解決手段】 半導体装置はスクライブ領域003とIC領域004からなり、スクライブ領域003の層間絶縁膜002には少なくとも一つの分離溝007が設けられ、分離溝007の両側の側壁にはプラグ金属膜からなるサイドウォール011が形成され、少なくともサイドウォールを覆うパッシベーション膜を設ける構成とした半導体装置とする。

(もっと読む)

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】OBIRCH法を行う際に、特性チェック素子の特性を容易に測定することができる、半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】レーザ光が照射されることにより特性が検査される、特性チェック素子と、前記特性チェック素子よりも上層に位置し、ダミーメタルが配置された、上部配線層とを具備する。前記上部配線層は、前記特性チェック素子に重なる第1領域と、前記特性チェック素子に重ならない第2領域とを備える。前記第1領域における前記ダミーメタルの密度は、前記第2領域における前記ダミーメタルの密度よりも、小さい。

(もっと読む)

21 - 40 / 187

[ Back to top ]