Fターム[5F038CA13]の内容

Fターム[5F038CA13]に分類される特許

41 - 60 / 187

半導体装置及び半導体装置の製造方法

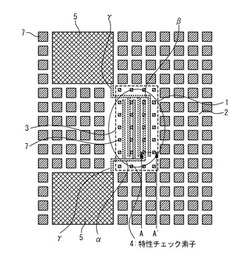

【課題】OBIRCH法を行う際に、特性チェック素子の特性を容易に測定することができる、半導体装置、及び半導体装置の製造方法を提供する。

【解決手段】レーザ光が照射されることにより特性が検査される、特性チェック素子と、前記特性チェック素子よりも上層に位置し、ダミーメタルが配置された、上部配線層とを具備する。前記上部配線層は、前記特性チェック素子に重なる第1領域と、前記特性チェック素子に重ならない第2領域とを備える。前記第1領域における前記ダミーメタルの密度は、前記第2領域における前記ダミーメタルの密度よりも、小さい。

(もっと読む)

半導体ウェーハ、及びその製造方法

【課題】シリコン基板にダメージを与えずに、ゲート下の不純物分布の正確な評価を安定して行うことのできる半導体ウェーハとその製造方法を提供する。

【解決手段】 半導体ウェーハは、半導体基板上の所定の箇所に設定されたモニター領域に、他と電気的接続を有しない断面形状がW字型のダミー充填部を有する。

(もっと読む)

半導体装置、そのプローブテスト方法及びその製造方法

【課題】本発明は、プローブテストが行われてから、プローブテストのためのロジック回路を除去し得る半導体装置を提供する。

【解決手段】本発明の半導体製造装置は、第1のチップ;前記第1のチップの周囲に配置されるスクライブレーン;及び、前記第1のチップのプローブテストを行うプローブテストロジック回路を含み、前記プローブテストロジック回路は、前記スクライブレーンの一部分に位置することを特徴とする。

(もっと読む)

半導体装置

【課題】ダイシングブレードでダイシングする際の層間絶縁膜間の密着性を良好にしつつ、層間絶縁膜の層間クラックを防ぐ。

【解決手段】スクライブライン領域202において、ダイシング工程においてダイシングブレードが通るブレード領域204およびブレード領域204の両側に形成され、ダイシングブレードが通らない非ブレード領域206にそれぞれダミー配線が形成され、非ブレード領域206においては上下に隣接するダミー配線106bとダミー配線110bとがダミービア108bで接続され、ブレード領域204においては、上下に隣接するダミー配線106aとダミー配線110aとがダミービアで接続されていない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】液晶ドライバ等の半導体集積回路装置においては、その形状が極端に細長いため、長手方向にプロセス特性がばらつくと、所望のデバイス特性が得られない。そこで、実製品ウエハにプロセスモニタ用の検査用素子を各種配置して、それらを測定することによって、プロセス特性のばらつきを監視している。しかし、ウエハ内におけるグローバルなプロセスばらつきは、比較的抽出しやすいものの、チップ内の局所的なプロセスばらつきの高精度の抽出は、大幅に検査用素子密度を上げない限り、困難であることが、本願発明者等により明らかにされた。

【解決手段】本願の一つの発明は、半導体集積回路装置の製造方法において、ウエハ上のチップ領域の近傍に複数のテスト素子領域を異なるピッチで配列し、プローブテストにおいて、それらを電気的に計測することにより、プロセスの局所的ばらつきをモニタするものである。

(もっと読む)

無線集積回路装置の製造方法、無線集積回路装置及び電子機器

【課題】効率的な動作試験ができる無線集積回路装置の製造方法、無線集積回路装置及び電子機器等を提供すること。

【解決手段】無線集積回路装置の製造方法は、ウェハー上に複数の無線集積回路装置100を形成し、複数の無線集積回路装置100のうちの少なくとも1つの無線集積回路装置を送信モード無線集積回路装置100aに設定し、複数の無線集積回路装置100のうちの送信モード無線集積回路装置100aを除く少なくとも1つの無線集積回路装置を受信モード無線集積回路装置100bに設定する。送信モード無線集積回路装置100aの送信回路により動作試験用の送信データを送信し、受信モード無線集積回路装置100bの受信回路により動作試験用の送信データを受信して動作試験を実行する。動作試験の完了後に複数の無線集積回路装置100をダイシングする。

(もっと読む)

半導体装置テスト接続体

【課題】テスト用のパッドを共用可能とする半導体装置テスト接続体を提供する。

【解決手段】半導体ウェーハ5と、半導体ウェーハ5に形成され、ダイシングライン13により個片化される予定の複数の半導体チップ11と、半導体ウェーハ5に形成され、半導体チップ11を特定する識別符号の少なくとも一部を付与するシフトレジスタ(33、34)と、半導体チップ11から離間し、半導体ウェーハ5の周辺に設けられ、外部から電気的な接続が可能なテスト用パッド18が複数配設されたパッド部17と、ダイシングライン13にあり、一端が識別符号に基づいて選択された半導体チップ11に接続され、他端がパッド部17の側に引き出されたテスト用のバス配線15と、バス配線15の他端とパッド部17との間にあり、バス配線15を決められたテスト用パッド18に接続する接続線部19とを備える。

(もっと読む)

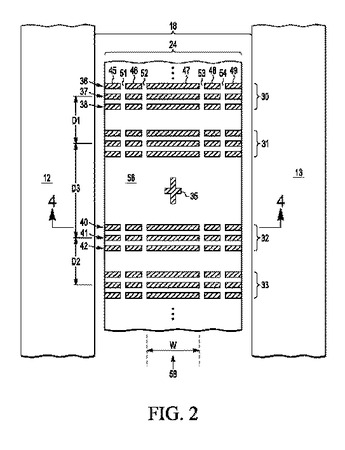

半導体ウェハ

少なくとも1つの第1ダイ12および少なくとも1つの第2ダイ13を含むウェハ10が提供され、国庫で、第1ダイおよび第2ダイは第1ダイと第2ダイとの間の領域によって互いに分離される。ウェハが、ウェハをパターニングするために使用されるツールとウェハの位置を合わせるために使用される第1位置決めマーク群31をさらに含む。位置決めマーク群31は第1ダイ12と第2ダイ13との間の領域に全体的に配置され、位置決めマーク群が複数の位置決め線36、37、38を含み、ここで、複数の位置決め線の各線は絶縁材料によって充填される複数のギャップ51、52、53,54によって互いに分離される複数のセグメント45、46、48、49を用いて形成される。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】本発明は、収納容器に半導体ウエハを長期間保管しても、パッド部にフッ化物などの汚染物質が付着することを防止できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、スクライブライン及びスクライブラインの内側に位置する製品チップ領域を有する半導体ウエハ上に絶縁膜を形成する工程(S12)と、製品チップ領域上に位置する第1のパッド部及びスクライブライン上に形成された評価用素子に接続された第2のパッド部を絶縁膜上に形成する工程8(S13)と、絶縁膜上、第1及び第2のパッド部の上にパッシベーション膜を形成する工程(S14)と、半導体ウエハを、収納容器に保管する工程(S15)と、収納容器から半導体ウエハを取り出し、パッシベーション膜をエッチングすることにより、パッシベーション膜に第1のパッド上に位置する開口部を形成する工程(S17)とを具備することを特徴とする。

(もっと読む)

集積回路装置

【課題】チップサイズを増加させずに、チップ位置情報等の識別情報を記録した集積回路装置を提供すること。

【解決手段】集積回路を有する集積回路基板と、前記集積回路に接続された導電性パッドと、前記導電性パッドを露出する開口部を持つ絶縁膜を備えた外部電極構造体とを有し、前記外部電極構造体が、前記集積回路基板の識別情報に対応する形状を有すること。

(もっと読む)

半導体集積回路装置

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体装置の製造方法、製造プログラム、及び半導体装置

【課題】回路規模の増大を抑制しつつ、素子破壊によってノード間の電気的接続を制御する電流制御素子を有する半導体装置の信頼性を高める。

【解決手段】本発明による半導体装置の製造方法は、半導体ウエハ1上に形成された素子特性抽出用パタン30の素子特性を測定するステップと、測定された素子特性を、素子特性抽出用パタン30に対応付けられた電流制御素子20の素子特性として抽出するステップと、抽出された素子特性に基づいて、半導体ウエハ1上におけるノード間に形成された電流制御素子20に供給するエネルギーを設定するステップと、設定されたエネルギーを電流制御素子に供給し、電流制御素子の素子破壊によってノード間の電気的接続を不可逆的に制御するステップとを具備する。

(もっと読む)

半導体装置の製造方法

【課題】より多数のリソグラフィ用合わせマークおよびPCMを設けることができ、かつPCMによる情報の漏えいを防止することができる半導体装置の製造方法を提供する。

【解決手段】複数の第1半導体チップ領域CRaに挟まれる第1スクライブ領域SCaの一部には、第1領域RAおよび第2領域RBが平行に配置されている。第1領域RAには、能動素子(トランジスタなど)および受動素子(抵抗、容量など)の少なくともいずれかの電気的評価を行うための第1モニター、寸法管理を行うための第2モニター、および、膜厚測定を行うための第3モニターから選択された少なくとも1つのモニターが配置されている。第2領域RBにはリソグラフィ用合わせマークが配置されている。切断する工程において第1領域RAが切り落とされる。

(もっと読む)

ダイシングされた集積回路における破壊の抑制

【課題】低誘電率誘電体を使用するICの歩留り損失及び初期故障を抑止する。

【解決手段】半導体デバイスは基板210及びダイ縁部を有する個片化されたダイ110を備える。相互接続誘電体層220a、220b、220c、220dが基板上に配置され、集積回路がその相互接続誘電体層内に配置された相互接続部230を有する。トレンチ250が、相互接続誘電体層内で、かつシール・リング270と相互接続誘電体層の残部との間に配置される。シール・リングは、相互接続誘電体層内で、かつトレンチと集積回路の間に配置され、相互接続誘電体層の残部はトレンチとダイの縁部との間に配置される。

(もっと読む)

半導体集積回路装置

【課題】組み合わせ回路と順序回路から構成される回路部の特性評価を容易化する。

【解決手段】半導体集積回路装置80には、同期回路部1、信号処理部2、テスト回路部3、テスト端子Padt1、テスト端子Padt2、及びテスト端子Padt3が設けられる。同期回路部1には、フリップフロップFF11、フリップフロップFF12、及び組み合わせ回路部11が設けられる。同期回路部1のテスト対象のパス以外のパスは、信号処理部2により適宜設定される。テスト回路部3は同期回路部1と同一回路構成を有し、且つテスト対象のパス以外のパスが所定の値に設定される。テスト回路部3はテスト端子Padt1から出力される入力信号Sinaとテスト端子Padt2から出力されるクロック信号Sclkaが入力され、テスト対象のパスのテスト結果がテスト端子Padt3を介して出力される。

(もっと読む)

集積回路の並行検査の方法、装置及びシステム

【課題】 検査コストを低減し、製品化までの時間を短縮し、欠陥デバイスが合格デバイスとして通過してしまう誤りの率を低下できる集積回路の検査の方法、装置及びシステムを提供する。

【解決手段】 本発明の装置では、共通の基板に、複数の被検査デバイス(DUT)と、複数の比較装置が設けられる。この複数のDUTは、すべて同一の入力刺激で動作し、各々が実行結果を発生する。この実行結果は比較装置で比較されて、比較特徴が生成され、その特徴により、欠陥のある被検査デバイスを検出する。

(もっと読む)

半導体装置

【課題】シールリングを加工することなく、半導体装置周辺部の異常を検出可能な半導体装置を提供する。

【解決手段】多層配線層が形成された半導体基板2上に、複数の電極端子5,6,7,8,9を設けるとともに、半導体基板2の外周部に設けられたシールリング3,4と、電極端子5,6,7,8,9とを電気的に接続する不純物注入領域(ドープ領域)2a,2b,2cを半導体基板2に形成することで、電極端子5,6,7,8,9間の抵抗などを測定することにより、半導体装置1周辺部の異常が検出可能になる。

(もっと読む)

半導体ウェーハおよび半導体装置ならびにその製造および設計方法

【課題】最小パッド間隔の制約を受けずに半導体チップサイズを縮小する。

【解決手段】半導体ウェーハ(1)は、ウェーハレベルバーンイン時に同じ信号が与えられるパッド(11a,11b)どうしを短絡する配線(20)を備えている。配線(20)は、半導体チップ(10a,10b)領域外にレイアウトされ、かつ、一部がダイシング領域(30)に含まれている。

(もっと読む)

モニター用結晶欠陥検出素子、半導体装置及びその製造方法

【課題】本発明は、プロセスの影響によって発生するシリコン基板の結晶欠陥を高感度に検出できるモニター用結晶欠陥検出素子、半導体装置及びその製造方法を提供する。

【解決手段】本発明に係るモニター用結晶欠陥検出素子は、シリコン基板に形成された素子分離膜11と、素子分離膜11の内側の素子領域10cに形成された複数のトランジスタとを有するモニター用結晶欠陥検出素子であって、複数のトランジスタそれぞれのゲート電極12が互いに電気的に接続されており、複数のトランジスタそれぞれのソース領域の拡散層10aが互いに電気的に接続されており、複数のトランジスタそれぞれのドレイン領域の拡散層10bが互いに電気的に接続されていることを特徴とする。

(もっと読む)

信号送受信方法、半導体装置の製造方法、半導体装置、およびテスタ装置

【課題】インダクタを配置するための必要面積を小さく保ちつつ、電磁誘導で信号の送受信を良好に行う。

【解決手段】一面にインダクタ114が形成された半導体装置100に、半導体装置100のインダクタ114に対応する位置に設けられた外部インダクタ204を含む外部装置(200)から信号の送受信を行う。この手順は、少なくとも半導体装置100のインダクタ114と外部装置200の外部インダクタ204との間に強磁性体の微粒子を含む強磁性体膜130を配置し、強磁性体膜130を介してインダクタ114と外部インダクタ204とを対向配置させる工程と、インダクタ114と外部インダクタ204とを対向配置させた状態で、インダクタ114と外部インダクタ204との間で電磁誘導で信号の送受信を行う工程と、を含む。

(もっと読む)

41 - 60 / 187

[ Back to top ]