Fターム[5F038CA13]の内容

Fターム[5F038CA13]に分類される特許

61 - 80 / 187

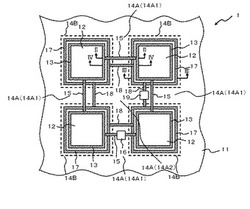

半導体装置

【課題】手間を要さずに回路部のテストを行うことができ、スクライブ領域の有効活用を図ることができ、半導体チップを安定的に製造することができ、非接触で外部との通信を行うことができる半導体装置を提供する。

【解決手段】半導体装置1は、半導体チップ形成領域14Bと、半導体チップ形成領域14B間に位置するスクライブ領域14Aとが形成された半導体ウェハ11と、半導体ウェハ11上に設けられた複数の半導体チップの回路部12と、各半導体チップ形成領域14B内に設けられ、各回路部12に電気的に接続される複数の第一の導電層13と、第一の導電層13同士をスクライブ領域14Aの一部をまたいで電気的に接続する第一の接続部15とを有する。第一の導電層13および第一の接続部15のいずれか一方に、外部電源供給用あるいは接地用のパッド16が接続される。半導体装置1は、回路部12に接続され、容量結合あるいは誘導結合により外部との通信を行う通信部Tを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】強い圧縮応力を有するシリコン窒化膜を用いたpMISFETを有する半導体装置及びその製造方法において、歩留まりが高く且つスイッチングスピードが高い半導体装置及びその製造方法を提供する。

【解決手段】ボックスマーク102内においてシリコン基板1を覆うようにシリコン酸化膜14を形成する。次に、基板上の半導体領域にシリサイド化反応によりニッケルシリサイド8を形成する。その後、強い圧縮応力を有するシリコン窒化膜9をpMISFET101及びボックスマーク102を覆うように形成する。その上に層間絶縁膜11を形成した後レジストをパターニングしてコンタクトホール13を形成する。この際、重ね合わせ精度が所定の規格を満たすまで、レジストを一旦除去し再度レジスト12bを形成する。

(もっと読む)

レチクルレイアウトデータ作成方法及びレチクルレイアウトデータ作成装置

【課題】半導体チップに応じて異なるスクライブ幅を備えるレチクルレイアウトデータを作成するレチクルレイアウトデータ作成方法及びレチクルレイアウトデータ作成装置を提供する。

【解決手段】複数種類の半導体チップのレチクルレイアウトデータに対して、実際にダイシングにて必要なスクライブ幅をそれぞれ設定する。設定した実際にダイシングにおいて必要なスクライブ幅の二分の一の幅で、前記複数種類の半導体チップのレチクルレイアウトデータに対して、その外周に配置されるチップスクライブ領域をそれぞれ作成する。

(もっと読む)

半導体装置及びその評価方法

【課題】半導体装置の回路特性の微調整に必要なトリミング情報を高精度に取得できると共に、測定時間の増大を防ぐことができるようにする。

【解決手段】半導体装置は、複数の被評価素子(TEG)2と、複数の被評価素子2のそれぞれに印加される電流値又は電圧値をモニタするモニタ用素子4と、複数の被評価素子2のそれぞれの一端と接続された複数の第1の電極パッド1と、モニタ用素子4の一端と接続された第2の電極パッド3とを有している。複数の被評価素子2のそれぞれの他端は、モニタ用素子4の他端と共通に接続されている。

(もっと読む)

半導体装置、半導体装置の試験方法

【課題】半導体ウエハのダイシング前に、出力バッファ、又は入力バッファを介した特性試験を行なうことができる半導体装置を提供する。

【解決手段】 本発明による半導体装置は、半導体ウエハ100上に形成され、出力バッファ23、入力バッファ29、スイッチ26、スクライブ領域20に設けられた第1伝送路25及び第2伝送路27を具備する。スイッチ26は、出力バッファ23の出力端子24と入力バッファ29の入力端子28との電気的接続を制御する。第1伝送路25は、出力端子24とスイッチ26とを接続する。第2伝送路27は、入力端子28とスイッチ26とを接続する。

(もっと読む)

半導体ウエハ及び半導体装置

【課題】スクライブ領域の幅を狭くするのに適した半導体ウエハを提供する。

【解決手段】半導体ウエハは、半導体素子の形成された複数のチップ領域が、隣接するチップ領域間にスクライブ領域を介して画定されており、スクライブ領域内に配置されたモニタ素子と、チップ領域内に配置されたパッドと、モニタ素子とパッドとを接続する配線とを有する。

(もっと読む)

半導体装置

【課題】半導体装置の製造歩留まりを向上できる。

【解決手段】本発明の例に関わる半導体装置は、ウェハ1内に設けられる第1及び第2半導体チップエリア21,22と、第1及び第2半導体チップエリア21,22内の各々に設けられ、トランジスタが形成される第1素子領域51,52と、第1及び第2半導体チップ51,52間に設けられるダイシングエリア3Aと、ダイシングエリア3A内に設けられ、アライメントマークが形成されるアライメント領域35と、第1素子領域51,52とアライメント領域35との間に設けられ、ウェハ1表面に対して垂直方向に突出した凸部91,92を有する凸部形成領域71,72とを具備し、凸部91,92の上端は、ウェハ1表面より高い位置にあり、トランジスタのゲート電極12上端よりも低い位置にある。

(もっと読む)

集積回路装置の評価方法

【課題】 集積回路装置の評価方法に関し、個々のトランジスタやロジック回路の経時劣化の実測による確認を含む設計フローを構築する。

【解決手段】 回路設計を終了した集積回路から信頼性評価対象素子或いは信頼性評価対象回路の少なくとも一方を含む信頼性評価対象要素を抽出し、前記抽出した信頼性評価対象要素を信号遅延測定回路に接続するように配置し、前記信頼性評価対象要素に対して電源電圧をストレス電圧として印加して、前記信頼性評価対象要素の経時劣化を信号遅延の劣化として測定する。

(もっと読む)

半導体装置及びその試験方法

【課題】大掛かりな装置を付加使用することなく可及的に簡易な構成により半導体チップ単位における試験用針の接触回数を容易且つ確実に把握して管理することができ、ひいては製造コストの削減及び製造時間の短縮化を可能とする。

【解決手段】スクライブ領域3上に、半導体チップ2ごとに対応して、第1の電極パッド11にプローブ針が接触した接触回数、更には試験回数を記憶する記憶部である複数のヒューズ13が設けられている。そして、半導体チップ2上で第1の電極パッド11に隣接して、ヒューズ13に対して接触回数及び試験回数の読み取り及び書き込みを行うための複数の第2の電極パッド12が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】ドライエッチング時のゲート絶縁膜へのプラズマチャージを抑制することにより、製品の歩留まり及び信頼性を向上させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体ウェハの有効領域に製品チップを形成すると共に、前記半導体ウェハの無効領域に有効領域の外周を囲むようにダミーチップを形成している。また、ダミーチップ及び製品チップそれぞれは、ゲート絶縁膜、ゲート電極、層間絶縁膜及びコンタクトホールを有している。その為、層間絶縁膜の膜厚は半導体ウェハの中央部に比べて外周部が薄くなっている場合において、ドライエッチング時のゲート絶縁膜へのプラズマチャージを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】不純物イオン注入時に、実効注入ドーズ量の場所によるばらつきが生じるのを防ぐ。

【解決手段】レジスト膜152をマスクとして半導体層(108)の所定の領域(112)に不純物イオンを注入する工程を含む半導体装置の製造方法であって、所定の領域に不純物イオンを注入するためにレジスト膜に開口部を形成する際に使用するレチクル領域全体に対する開口部の割合を示すマスクデータ率が第1の基準値未満の場合に、所定範囲の領域以外の領域に、ダミーイオン注入領域142を設け、レチクルのマスクデータ率が第1の基準値以上の第2の基準値より大きくなるようにする。

(もっと読む)

レチクルデータ作成方法、レチクルデータ作成装置及びウェハ

【課題】マルチダイ用レチクルを使用して製造されるチップの歩留まりを向上させ得るマルチダイ用レチクルのデータ作成方法を提供する。

【解決手段】プロセスパターンからメインチップの未配置領域を検出する工程と、未配置領域を矩形に分割する工程と、分割された矩形をダミーチップとしてスクライブデータを発生させる工程と、ダミーチップにダミーパターンを発生させる工程とを備えた。

(もっと読む)

電源遮断トランジスタを有する半導体装置

【課題】パワーゲーティングの適用に困難さをもたらすコストアップと性能低下のトレードオフを打開する。

【解決手段】P型基板2と、P型基板2に互いに離れて形成されている第1のPウェル4および第2のPウェル5と、を有し、第1のPウェル4にN型ロジックトランジスタLTnが形成され、第2のPウェル5に電源遮断トランジスタPGTが形成され、第1のPウェル4と第2のPウェル5との間に、P型基板2内の電位干渉を遮蔽する遮蔽部(例えば2つのPN接合)が形成されている。遮蔽部により電位干渉が遮蔽された2つの基板領域のうち、第2のPウェル5側の基板領域に、電源遮断トランジスタPGTに基板バイアス電圧VBBを印加するための基板コンタクト領域11が形成されている。

(もっと読む)

半導体集積回路の検査回路

【課題】組み込み自己検査(BIST)回路において検査対象回路に修正が発生した場合に、BISTの期待値を半導体集積回路の修正なく変更可能とする。

【解決手段】半導体集積回路100は、検査対象回路101とBIST回路とを有する半導体集積回路であって、当該BIST回路は多入力シフトレジスタ(MISR)103と期待値格納回路104と期待値照合回路105とを有する。検査対象回路101の回路修正が発生した場合に、当該回路修正に対応した圧縮シグネチャの期待値118を期待値格納回路104に半導体集積回路100の外部から設定することにより検査が可能となる。

(もっと読む)

半導体集積回路ウエハ、半導体集積回路チップ及び半導体集積回路ウエハのテスト方法

【課題】ボンディングパッドに傷跡を残さず、かつボンディングの不良の削減や接続の信頼性を向上することが可能な半導体集積回路ウエハを提供する。

【解決手段】半導体集積回路領域2aと、スクライブ領域3と、前記スクライブ領域内に備えられたBIST回路4と、半導体集積回路2とBIST回路4とを接続する接続配線9と、BIST切替信号入力パッド7と、BIST切替信号入力パッド7からの駆動信号により駆動されるBIST切替回路8とを備え、BIST切替回路8は、半導体集積回路用の入出力パッド6と、入出力パッド6と半導体集積回路2とを接続する回路配線11と、回路配線11の途中に設けられて、BIST切替信号入力パッド7からの駆動信号によって駆動するスイッチ素子10とを具備してなる半導体集積回路ウエハを採用する。

(もっと読む)

半導体ウエハ、半導体チップ、半導体装置、及び半導体装置の製造方法

【課題】信頼性の高い半導体ウエハ、半導体チップ、及びこの半導体チップを搭載した半導体装置を提供すること。

【解決手段】本発明に係る半導体ウエハ50は、スクライブ線領域1と、スクライブ線領域1により区画される複数の素子形成領域2有する半導体ウエハ50であって、スクライブ線領域1に配設された導電性パターン30と、導電性パターン30のうち、少なくともスクライブ線領域1に沿ってダイシングすることにより得られる半導体チップ51の側面に露出する、若しくは露出する可能性のある導電性パターン30の上層に、当該導電性パターン30と対向配置するように形成された島状のパッシベーション膜20と、を備える。

(もっと読む)

半導体装置製造用基板、半導体装置、および半導体装置の製造方法

【課題】非破壊で迅速にトレンチ形状の仕上がりを検査することができる、半導体装置製造用基板、半導体装置、および半導体装置の製造方法を提供する

【解決手段】ウエハは、有効領域と、無効領域とを備えている。有効領域は、第1溝部を有する半導体素子を含んでいる。無効領域は、有効領域の周りに設けられ、ダイシングにより切断される位置を含んでいる。この無効領域は、不純物層60と、第1半導体層51と、第2溝部T2とを含んでいる。不純物層60は第1導電型を有している。第1半導体層51は、不純物層60上に設けられ、第1導電型と異なる第2導電型を有している。第2溝部T2は、第1溝部と同時に形成され、厚み方向に第1半導体層51を貫通し、平面パターンにおいて第1半導体層51に囲まれている。

(もっと読む)

半導体集積回路装置及びその検査方法

【課題】限られた領域に多くの被測定素子を搭載でき、かつ、短時間で多数個の被測定素子の特性の良否判定及び特性異常を検出することができ、その結果、検査コストを低減できる半導体集積回路装置及びその検査方法を提供する。

【解決手段】半導体集積回路装置は、複数個の被測定素子11と、複数の選択素子12と、所望の被測定素子11を選択するアドレス制御・選択回路14と、複数個の被測定素子11の各々の良否判定の基準値を設定する規格値設定手段15と、被測定素子11の電気特性値と基準値との比較を複数の被測定素子11の全てに対して順に行う比較回路17と、比較回路17による比較結果に基づいて計数を行うカウンタ回路18と、回路動作を制御するための制御回路16とを備える。カウンタ回路18は、基準値を外れた被測定素子11の総数を出力する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaN系あるいはGaAs系FET用エピでは、バッファ層耐圧を向上させるために最近ではバッファ層に高抵抗のエピを用いる傾向にある。しかし、微細ゲートのパターニングのための電子ビーム露光によるリソグラフィーの際、チャージアップ現象が生じるという問題がある。

【解決手段】金属配線によって電子が放電する経路を形成する。すなわち、FETを作製するウエハ上の各チップの周辺部のスクライブラインあるいはエッチカットする部分に相当する部分に金属配線を配し、電子線にとってウエハ上で陽極あるいは接地導体となる部分とその金属配線が金属で接続されており、さらにチップ内においてFETのソース電極がチップ周辺の金属配線と金属で接続されるようにした。

(もっと読む)

半導体装置及びその評価方法

【課題】大規模なコンタクトチェーン又は大規模な配線パターンにおける複数の素子の電気的な測定を行う際に、不具合箇所の検出をより容易に行える回路構成を有する半導体装置とその評価方法を得られるようにする。

【解決手段】半導体装置は、直列に接続された複数の被測定単位素子101からなる被測定素子回路と、隣り合う被測定単位素子101間の各ノードにそれぞれ接続された複数の選択素子104と、複数の選択素子104と接続されるノード情報伝達回路107とを備えている。被測定素子回路の両端の第1のテストパッド102又は第2のテストパッド103に電圧を印加したときに各ノードに発生する電位が、ノード情報伝達回路107に入力され、入力された各ノードの電位を接続された順に出力する。

(もっと読む)

61 - 80 / 187

[ Back to top ]