Fターム[5F038CA13]の内容

Fターム[5F038CA13]に分類される特許

141 - 160 / 187

半導体装置

【課題】 チップサイズの増大を抑制しつつ、半導体チップの特性検査によるボンディング用パッドの損傷を防止する。

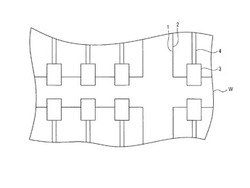

【解決手段】 半導体ウェハWには、能動領域が形成されたチップ領域1が配置され、チップ領域1はスクライブライン2を介して互いに隔てられ、チップ領域1の周辺部には、スクライブライン2上に延伸されるようにして電極パッド3が配置されている。

(もっと読む)

半導体装置の製造方法

【課題】ダイシング前に半導体装置内に書き込まれた情報が、ダイシング後に読み出されたり、改ざんされるのを防ぐこと。

【解決手段】 半導体ウエハ20上に、記憶領域を内蔵するチップ領域21、半導体ウエハを切断するためのスクライブ領域24、記憶領域にデータを書き込むために外部から電気信号が供給されるパッド22、およびパッド22と記憶領域とを電気的に接続する引き出し配線23を形成する。その際、パッド22をスクライブ領域24内に形成する。そして、パッド22を介して記憶領域にデータを書き込んだ後、スクライブ領域24に沿って半導体ウエハを切断して半導体チップを得る。その切断の際にパッド22が一緒に切り落とされるか、または引き出し配線23がパッド22から切り離される。

(もっと読む)

半導体装置

【課題】 LSIチップとスクライブTEGにある電極端子によるLSIチップ面積の増大と高コスト化を抑制し、LSIチップ面積の縮小と低コスト化を実現する。

【解決手段】 半導体素子からなる内部回路および内部回路の検査に用いる検査回路が集積して形成されたLSIチップ1と、LSIチップ周辺のスクライブ領域上に形成され、評価素子と電極端子6が形成されたスクライブTEG5とを備え、スクライブTEG5内の電極端子6のうちの少なくとも一つは、スクライブTEG5内の評価素子およびLSIチップ1内の検査回路と電気的に接続されている。これにより、スクライブTEG内の電極端子でLSIチップ内の検査回路を評価でき、LSIチップ内の電極端子を削減できる。

(もっと読む)

大規模集積回路のウェハおよびその製造方法

【課題】 スクライブライン幅を増加することなく、半導体装置を容易に短時間で評価することができるように改良された大規模集積回路のウェハを提供する。

【解決手段】 第1のスクライブライン12aが延びる方向に、複数個の半導体装置1が並んで半導体装置の列を形成している。半導体装置の列は、第1のスクライブライン12aと直交する第2のスクライブライン12bが延びる方向に複数並んで設けられる。第2のスクライブライン12b内に、各半導体装置1と対になるように、中継回路9が設けられる。中継回路9と半導体装置1は、ポリシリコン配線13で接続される。中継回路9にその一方端が接続された第2層配線6が、第2スクライブライン12b内に延びている。テストチップ3内に形成されたパッド電極4aにその一方端が接続された第3層配線5cが、第1のスクライブライン12a内に延びている。第2層配線6と第3層配線5aは、ビアホール10を介して電気的に接続されている。

(もっと読む)

半導体装置

【課題】 スクライブTEGの電極端子によるLSIチップのウエハ上での取れ数削減を抑制して、低コスト化を実現する。

【解決手段】 半導体素子からなる内部回路が集積して形成されたLSIチップ1と、LSIチップ周辺のスクライブ領域4上に形成され、評価素子5と電極端子6が形成されたスクライブTEGとを備え、スクライブTEGの評価素子5の少なくとも一つとスクライブTEGの電極端子6とが、それぞれスクライブ領域4内の異なる領域に分離して形成され、互いに電気的に接続されている。これにより、スクライブTEGの電極端子と評価素子の接続の制約が緩和され、結果的にスクライブ領域面積の縮小ができ、LSIチップの低コスト化を実現できる。

(もっと読む)

半導体ウエハ、その製造方法及びマスク

【課題】 半導体素子のパターン寸法を検証する際の検証精度を高め、且つ、その歩留ま りを損なうことなく検証するためのTEGを形成する。

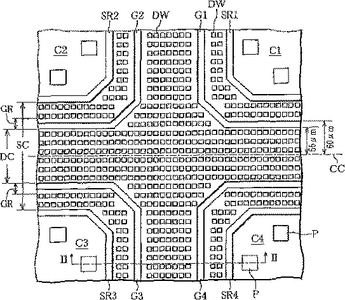

【解決手段】 半導体ウエハの製造にあたり、2つの素子形成領域12と、素子形成領域12を相互に区画するスクライブ線領域13とが1つのレチクルショット11で形成される。各レチクルショット11の4隅のスクライブ線領域13上、及び、中央のスクライブ線領域13上に、スクライブ線領域13の幅の1/2以下の寸法を有するTEG14を形成する。各TEG14には、素子形成領域12内の半導体素子のパターンと同じ形状で、且つ、相互に同一形状のパターンが形成される。各スクライブ線領域13上で隣接する2つのTEG14は、スクライブ線領域13の長手方向に離間して配置される。

(もっと読む)

半導体ウエーハ

【課題】個々に分割された半導体チップにテスト用の金属パターンが残存しても、デバイスの構成を検出することができない半導体ウエーハを提供する。

【解決手段】半導体基板3の表面に格子状に形成されたストリート4によって複数の領域が区画され、この区画された領域に複数のデバイス5が形成され、ストリート4にテスト用の金属パターン6が配設されている半導体ウエーハ2であって、テスト用の金属パターン6はストリート4の中心より一方側に配設されているとともに、ストリート4の中心を跨いで配設された導線7によってストリート4の他方側に形成されたデバイス5に接続されている。

(もっと読む)

半導体集積回路ウェハ、その試験方法および半導体集積回路部品の製造方法

【課題】 ウェハからの半導体素子の取り数を減少させず、ウェハ段階で複数チップのリークテストを一括して行って良品率を簡単に予測してウェハ検査を簡略化する。

【解決手段】 スクライブライン3上に制御信号用配線31a、電源用配線31bおよび接地用配線31cを配置して、これらをそれぞれブロック内の複数の半導体素子2の各端子21a〜21cにそれぞれ接続させ、ブロック内に設けられたTEG4内の各測定用端子41a〜41cにそれぞれ接続して、ブロック毎に一括してリーク電流を測定する。リーク電流が設定値未満の場合には、ブロック内の半導体素子の良品率が高いと判断して、ウェハ状態で個々の半導体素子の個別テストを省略する。リーク電流が所定値以上の場合には、ブロック内の半導体素子の良品率が低いと判断して、半導体素子2の各端子21a〜21cから、ウェハ状態で個々の半導体素子の個別テストを行う。

(もっと読む)

半導体装置の製造方法および半導体ウェーハ

【課題】 チップサイズを増大させることなく、狭隘なダイシングライン上に複数のテスト領域を配置した半導体装置の製造方法および半導体ウェーハを提供する。

【解決手段】 主面に形成された格子状のダイシングライン11、12と、ダイシングライン11、12で囲まれた矩形状格子に形成された複数の集積回路13と、一方向のダイシングライン11上に互いに離間して形成され、複数のテスト素子M1、M2とテスト用パッド31〜34と配線37〜39のみからなる複数のテスト領域21、22を有する複数のテスト領域群と、を具備し、各群のテスト領域21、22においては、互いに異なるテスト素子M1、M2が配線37〜39によってテスト用パッド31〜34に接続されている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線に対する接続孔の位置ずれ量及び位置ずれ方向を精度よく測定することができる半導体装置の製造方法を提供する。

【解決手段】本半導体装置の製造方法では、第1の絶縁膜上に、複数の第1のTEG用配線10dを形成する。第1の絶縁膜上及び複数の第1のTEG用配線10d上に、第2の絶縁膜11を形成する。第2の絶縁膜11に、複数の第1のTEG用配線10dの端部それぞれ上又はその近傍に位置し、前記複数の端部に対する相対位置が同一方向にずれている複数のTEG用接続孔11bを形成する。第2の絶縁膜11上に、複数のTEG用接続孔11bそれぞれに接続する複数の第2のTEG用配線13bを形成する。いずれの第1のTEG用配線10dと第2のTEG用配線13bが相互に導通しているか検査することにより、第1のTEG用配線10dとTEG用接続孔11bの位置ずれが検査される。

(もっと読む)

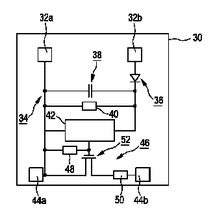

外部スイッチング機能を提供する集積回路

本発明は、論理回路(42)、及び外部信号を受信し、この受信した外部信号を論理回路(42)に伝送する受信手段(34)を具えた集積回路(30,34,70)に関するものであり、そしてこうした集積回路に結合された装置(72)、及びこうした集積回路を製造し動作させる方法、及び制御データを装置に伝送する方法に関するものである。こうした集積回路(30,54,70)に、従来のトランスポンダに比べて拡張された機能を提供するために、論理回路(42)、少なくとも2つの外部接点(44a,44b,76a,76b)、この論理回路(42)をこれらの外部接点(44a,44b,76a,76b)に接続するためのスイッチング手段(46)、及び外部信号を受信し、この受信した外部信号を前記論理回路(42)に伝送するための受信手段(34)を具えた集積回路(30,54,70)を提案し、この集積回路(30,54,70)は、前記スイッチング手段(46)によって前記外部接点(44a,44b,76a,76b)間の電気接続をスイッチングする前記外部接点(44a,44b,76a,76b)を通したスイッチング機能を提供する第1動作モードで動作可能であり、前記スイッチング手段(46)は、前記受信した外部信号に応答して前記論理回路(42)によって制御される。さらに、こうした集積回路(30,54,70)に結合された対応する装置(72)、及びこうした集積回路(30,54,70)を製造し動作させる対応する方法、及び制御データを装置(72)に伝送する対応する方法を提案する。  (もっと読む)

(もっと読む)

半導体装置及びその試験方法

【課題】同時に試験する半導体チップ数を増加して効率のよい半導体装置の試験を実現し、また、信頼性の高い半導体装置の試験を実現しうる半導体装置及びその試験方法を提供する。

【解決手段】半導体ウェーハ10に形成され、半導体集積回路を含む半導体チップ領域12と、半導体チップ領域12に隣接して設けられたスクライブライン14と、スクライブライン14に半導体チップ領域12の半導体集積回路と電気的に分離して形成され、半導体集積回路を試験する際に入力するテスタ信号を制御する試験用素子18とを有し、半導体チップ領域12の半導体集積回路と、試験用素子18とは、プローブカード16に設けられた配線を38L、38Rを介して互いに電気的に接続される。

(もっと読む)

半導体装置

【課題】内部集積回路の試験動作を行うとともに、不純物濃度を電気特性で確認する半導体装置を提供する。

【解決手段】ウェハ100上には、半導体集積回路が形成されているチップ101とスクライブ領域102を交互に繰り返し形成する。スクライブ領域102上にはマスク合わせや寸法測定を行うためのパターンとともに、試験動作用パッド105、不純物測定TEG104を配置する。不純物測定TEG104は不純物の濃度、深さを確認出来るモジュールであり、試験動作用パッド105とはスイッチ106を介して接続する。試験動作用パッド105は、半導体装置101の内部回路107とヒューズ108、スイッチ109を介して接続している。スイッチ106、109の切り替えによって、試験動作用パッド105から不純物測定TEGと内部集積回路107の電気特性を測定する。スイッチ106、109は、スイッチ制御回路110の信号により切り替えを行う。

(もっと読む)

高周波半導体装置

【課題】 インピーダンス不整合を生じることなしに、動作周波数が高くなったときのワイヤボンド接続部分における高周波特性の劣化が低減された高周波半導体装置を提供する。

【解決手段】 高周波半導体装置は、半導体基板8の上に形成された高周波半導体素子1と、一端が高周波半導体素子1に接続する高周波信号伝送線路7と、高周波信号伝送線路7の延伸方向に対し垂直になるようにして高周波信号伝送線路7の他端に接続する高周波信号入出力用パッド2と、高周波信号入出力用パッド2の長手方向の両側にそれぞれ形成される接地電位用パッド4,5とを有する。高周波信号伝送線路7の幅方向の寸法W2と、高周波信号入出力用パッド2の幅方向の寸法W1とが実質的に一致し、高周波信号入出力用パッド2の長手方向に沿って複数の金線3,3´が接続していることが好ましい。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】TEG上のパッド部の浸食を防止し、また、実デバイスのパッド部の半田のぬれ性や半田形成後のシェア強度の向上を図る。

【解決手段】半導体ウエハのチップ領域CAの第3層配線M3およびスクライブ領域SAの第3層配線M3を、それぞれ、TiN膜M3a、Al合金膜M3bおよびTiN膜M3cで構成し、チップ領域CAの再配線49上の第2パッド部PAD2を洗浄し、もしくはその上部に無電界メッキ法でAu膜53aを形成する。さらに、Au膜53a形成後、リテンション検査を行い、その後、さらに、Au膜53bを形成した後、半田バンプ電極55を形成する。その結果、TiN膜M3cによってTEGであるスクライブ領域SAの第3層配線M3の第1パッド部PAD1のメッキ液等による浸食を防止でき、また、Au膜53a、53bによって第2パッド部PAD2の半田のぬれ性や半田形成後のシェア強度の向上を図ることができる。

(もっと読む)

半導体集積回路、プローブカードおよび半導体集積回路の試験方法

【課題】 試験を低コスト化できる半導体集積回路、プローブカードおよび半導体集積回路の試験方法を実現する。

【解決手段】 半導体ウエハ189上で同時に試験される2個の各半導体集積回路チップである各被測定チップ109、110を、互いに出力端子用パッド111、112、115、116側が隣り合うように対称配置して設ける。一方の被測定チップ109の個々の出力端子用パッド111、112と、隣り合う他方の被測定チップ110の個々の出力端子用パッド115、116との対応するもの同士をそれぞれ短絡するパターン配線190を設ける。

(もっと読む)

半導体チップの製造方法及び半導体ウェハ

【課題】 TEGが形成された半導体ウェハにおいて、半導体チップの取得数が増大可能な配置を実現可能とするとともに、形成されたTEGの効率的な除去を実現可能とする。

【解決手段】 複数の素子形成領域内に配置される半導体素子と、上記それぞれの素子形成領域を画定する分割領域内に配置されるTEGとを有する半導体ウェハにおいて、上記分割領域にその領域幅が部分的に拡大されたTEG配置部を形成し、当該TEG配置部に上記TEGを配置する。さらに、上記半導体ウェハに保護シートを貼り付けて、プラズマエッチングを施すことで、上記それぞれの素子形成領域を個片に分割して半導体チップを形成し、その後、上記保護テープを剥がすことで、上記分割領域内に残存しかつ上記保護テープに貼り付けられた状態の上記TEGを当該保護テープとともに除去する。

(もっと読む)

半導体装置の製造方法、半導体ウエハおよび半導体装置

歩留まり良く、スクライブ領域をダイシングできる半導体装置の製造方法を提供する。 半導体装置の製造方法は、(a)半導体素子を形成した複数のチップ領域と、前記複数のチップ領域を分離し、切断用ダイシング領域を内包するスクライブ領域とを有し、前記スクライブ領域内のダイシング領域より外側に各チップ領域を囲む様に溝形成領域が画定された半導体ウエハを準備する工程と、(b)前記半導体ウエハの上方に、層間絶縁膜と配線層とを交互に形成した多層配線構造とダミー配線を配置する工程と、(c)前記多層配線構造を覆って、パッシベーション層を含むカバー層を形成する工程と、(d)前記溝形成領域において、前記複数のチップ領域の各々を取り囲む溝を上方から、少なくとも前記パッシベーション層を貫通して形成する工程と、を含む。  (もっと読む)

(もっと読む)

半導体装置

【課題】 多層配線の層間絶縁膜としてlow−k材料を用いた半導体チップを樹脂封止した場合において、そのlow−k材料からなる層間絶縁膜の剥離を防止する。

【解決手段】 半導体装置は、その主面の厚さ方向にローカル層、中間層、グローバル層が順に形成されている半導体チップ1Cと、半導体チップ1Cを被覆する封止樹脂8とを備えている。ローカル層は酸化シリコンを主成分とする層間絶縁膜3を有しており、中間層はlow−k材料からなる層間絶縁膜5を有しており、グローバル層は酸化シリコンを主成分とする層間絶縁膜6を有している。半導体チップ1Cのコーナ部において、層間絶縁膜3、層間絶縁膜5および層間絶縁膜6が除去されて、長溝9が形成されている。

(もっと読む)

配線形成工程の検査方法、半導体装置の製造方法、評価用半導体基板、及び半導体装置

【課題】配線形成工程の条件が適切であるか否かを容易かつ安価に判断できるようにする。

【解決手段】モニター用の半導体基板1の上方に、互いに略平行かつ幅が互いに異なる複数の下地配線2a,2b,2cを形成する工程と、複数の下地配線2a,2b,2c上に絶縁膜4を形成する工程と、絶縁膜4上に導電膜を形成する工程と、導電膜をパターニングすることにより、複数の下地配線2a,2b,2cを跨ぐ評価用配線パターン6を形成する工程と、評価用配線パターン6の抵抗を測定する工程と、抵抗値が基準を満たさない場合には、導電膜の形成条件及び導電膜のパターニング条件の少なくとも一つを変更し、抵抗値が基準を満たす場合には、導電膜の形成条件及び導電膜のパターニング条件それぞれが適切であると判断する工程とを具備する。

(もっと読む)

141 - 160 / 187

[ Back to top ]