Fターム[5F038CD18]の内容

Fターム[5F038CD18]の下位に属するFターム

シリサイド (91)

Fターム[5F038CD18]に分類される特許

1 - 20 / 615

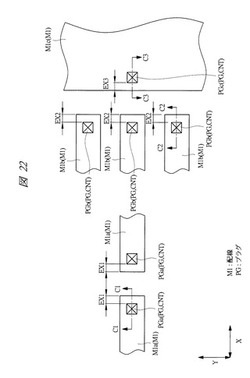

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置

【課題】任意の配線設計に適用でき、高精度な抵抗比を有する2個の抵抗体を備えた小型の半導体装置を提供する。

【解決手段】抵抗体R1f,R2fの長さをL、配線4a,4bの直上にある抵抗体R1f,R2fの外辺の長さを配線上長さH、外辺配線被覆率Vを、V=H/2Lで定義したとき、2個の抵抗体R1f,R2fのうち少なくとも外辺配線被覆率Vの小さい抵抗体R2fの下方において、配線4a,4bと同じ配線層から形成された反射補正パッドPa,Pbが、外辺の直下に配置されてなり、反射補正パッドPa,Pbの直上にある抵抗体R2fの外辺の長さを補正パッド上長さPとし、抵抗体R1f,R2fの外辺配線層被覆率Wを、W=(H+P)/2Lで定義したとき、2個の抵抗体R1f,R2fについて、外辺配線層被覆率Wの差が、記外辺配線被覆率Vの差より小さく設定されてなる半導体装置100とする。

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

半導体装置及びこれを備える半導体モジュール

【課題】データ出力バッファの正確なインピーダンスキャリブレーション動作を行う。

【解決手段】電源ラインVL1とデータ端子24との間に接続されたP型トランジスタユニット201と、電源ラインVL1とキャリブレーション端子ZQとの間に接続されたP型トランジスタユニット111〜114と、キャリブレーション端子ZQの電位が基準電位VREFと一致するよう、P型トランジスタユニット111〜114インピーダンスを調整し、一致した状態におけるP型トランジスタユニット111〜114の一つのインピーダンスをP型トランジスタユニット201に反映させるインピーダンス制御回路とを備える。これにより、基準電位VREFが電源電位VDDの半分のレベルからオフセットしたレベルに設定されている場合であっても、正確なキャリブレーション動作を行うことができる。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体装置

【課題】残渣による配線間のショートの発生を防ぐ。

【解決手段】本発明の半導体装置は、高誘電率材料を含む第1のゲート絶縁膜4と第1のゲート絶縁膜4上に形成された第1のメタルゲート電極5とを備える第1のトランジスタが形成される半導体基板上の第1の領域と、高誘電率材料を含む第2のゲート絶縁膜4と第2のゲート絶縁膜上に形成された第2のメタルゲート電極12とを備え、第1のトランジスタとは閾値電圧の異なる第2のトランジスタが形成される半導体基板上の第1の領域に並ぶ第2の領域と、電位の異なる第1および第2の配線と、を有し、第1の領域と第2の領域との境界が、第1および第2の配線の少なくとも一方としか重ならない。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

半導体集積回路装置

【課題】過電流に対して内部回路を保護する半導体集積回路装置を提供することを目的としている。

【解決手段】多層配線構造を有する半導体集積回路装置であって、半導体集積回路装置の内部にある内部回路と半導体集積回路装置の外部にある外部回路とを接続するために半導体集積回路装置の内部に設けられたパッドパターンにおいて、第1の配線層と、第1の配線層が形成されている層とは別の層に形成されている第2の配線層と、第1の配線層と第2の配線層を接続するビアと、を備え、第2の配線層にヒューズパターンが形成されており、ヒューズパターンを経由して内部回路と外部回路とを電気的に接続する。

(もっと読む)

半導体集積回路

【課題】設計する回路の中で電流の多く流れる信号線を容易に見つけ出すことができ、容

易にその部分の電流を測定できるスタンダードセルを提供することを課題とする。

【解決手段】電流検出用テストパッドを少なくとも2つ有するスタンダードセルを自動レ

イアウトで配置する。そして、2つのテストパッド間を接続する配線を切断することで、

該2つのテストパッドを電流測定用テストパッドとして利用する。なお、スタンダードセ

ル内の2つのテストパッド間は、過電流が流れることにより電流の流れる経路が遮断され

る配線によって接続される構成としてもよい。また、2つのテストパッド間をつなぐ配線

部にメモリ又はアナログスイッチを設ける構成としてもよい。

(もっと読む)

半導体装置

【課題】半導体素子を、より小型化することができる半導体装置、当該半導体素子、及び基板を得る。

【解決手段】半導体素子12は、階調電圧を出力する半導体素子内部出力部30C,30D(第1及び第2の階調電圧出力部)と、半導体素子内部出力部30Cの周辺に配置され、半導体素子内部出力部30Cに電源を供給する第1の電源端子電極52aと、半導体素子内部出力部30Dの周辺に配置され、半導体素子内部出力部30Dに電源を供給する第2の電源端子電極52aと、を備え、基板18は、半導体素子内部出力部30C,30Dの両方に共通して接続され、半導体素子12の下側に設けられた共通接続部94(第1の配線パターン)と、共通接続部94と外部入力端子(22)とを電気的に接続するインピーダンス調整部96(第2の配線パターン)と、を備える。

(もっと読む)

電磁波干渉フィルタ

【課題】小型化が可能な電磁波干渉フィルタを提供すること。

【解決手段】実施形態に係る電磁波干渉フィルタ10は、半導体基板11の表面上に形成された抵抗R、およびこの抵抗Rの両端にそれぞれ電気的に接続された一対のキャパシタC、をそれぞれ具備する複数の電磁波干渉フィルタ回路12と、これらの電磁波干渉フィルタ回路12間の半導体基板11に埋め込み形成された素子分離層13と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

半導体装置

【課題】多層配線内の信号線とそれに接続されるビアとを共に同軸構造にする。

【解決手段】多層配線には、例えば、異なる層に設けられる信号線10,20と、これらの信号線10,20間を接続する接続部30(ビア)が設けられる。信号線10,20は、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。更に、信号線10,20間を接続する接続部30も、配線層及び配線層間を接続する接続層で囲み、同軸構造とする。信号線10,20のほか接続部30も同軸構造とすることで、信号線10,20及び接続部30を伝送される信号の、周囲からの、又は周囲への、電磁気的な影響が効果的に抑制されるようになる。

(もっと読む)

半導体装置

【課題】プログラマブルなアナログデバイスを提供する。また、電源電位の供給が遮断されたときでもデータの保持が可能で、且つ、低消費電力化が可能なアナログデバイスを提供する。

【解決手段】アナログ素子を含むユニットセルにおいて、ユニットセルのスイッチとして、第1乃至第4のトランジスタを用い、第1のトランジスタと第2のトランジスタとが接続された第1のノード、及び、第3のトランジスタと第4のトランジスタが接続された第2のノードの電位を制御することで、ユニットセルの出力を導通状態、非導通状態、又はアナログ素子を介した導通状態のいずれかに切り替える半導体装置を提供する。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

撚り合わされた導線を有する集積回路インダクター

【課題】集積回路インダクターを提供すること。

【解決手段】第1の端子と、第2の端子と、第1の端子と第2の端子との間に連結された伝導性経路とを備え、伝導性経路は、集積回路上に複数の撚り合わされた伝導性線を含む、インダクター。撚り合わされた伝導性線は、集積回路上に少なくとも1つの金属層から形成された少なくとも第1の伝導性線と、集積回路上に少なくとも1つの金属層から形成された少なくとも第2の伝導性線とを含む、インダクター。

(もっと読む)

受光デバイス、これを用いた光受信機、及び受光デバイスの製造方法

【課題】 従来のPD製造プロセスと同じ工程で大受光径PDの帯域を拡大して、光受信部の高速化を図る。

【解決手段】 受光デバイスは、半導体基板の上方に形成された第1導電型の第1半導体層、前記第1半導体層上の光吸収層、および前記光吸収層上の第2導電型の第2半導体層の積層構造を有する光検出素子と、前記半導体基板の上方で、前記光検出素子に接続されるインダクタと、前記光検出素子で生成された電流を前記インダクタを介して取り出す出力電極と、前記光検出素子にバイアス電極を印加するバイアス印加用電極と、前記インタダクタの金属配線と交差して、前記光検出素子と、前記出力電極又は前記バイアス印加用電極との間を電気的に接続する交差配線と、を含む。

(もっと読む)

1 - 20 / 615

[ Back to top ]