Fターム[5F038DT12]の内容

Fターム[5F038DT12]に分類される特許

1 - 20 / 1,067

半導体集積回路

半導体チップ及びその抵抗測定方法、並びに半導体装置

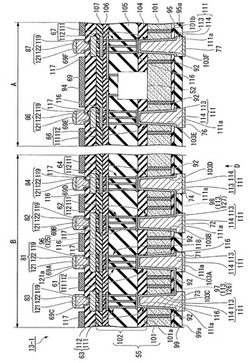

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体基板の評価方法および評価用半導体基板

【課題】例えばCCD、CMOSセンサ等の高歩留まりが要求される製品に使用される高品質ウェーハに関して、接合リーク電流特性を高精度で評価することが可能な半導体基板の評価方法および評価用半導体基板を提供する。

【解決手段】評価する半導体基板1に、複数のPN接合5と、該複数のPN接合5同士を分離する分離酸化膜6と、該分離酸化膜6の下に位置するチャネルストップ層3とを形成してから、前記複数のPN接合5における接合リーク電流を測定して評価を行う半導体基板の評価方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体装置

【課題】本発明は、電圧測定回路における電流損失を抑え、異常動作の場合であっても電圧測定回路が破壊されない半導体装置を提供する。

【解決手段】

本発明は、第1導通電極と、第2導通電極とを有する半導体スイッチ素子10と、半導体スイッチ素子10の第1導通電極および第2導通電極間の電圧を測定するための電圧測定回路31とを備える半導体装置101である。電圧測定回路31は、半導体スイッチ素子10と並列に接続され、半導体スイッチ素子10の導通方向に印加される電圧を所定値に制限するダイオード素子11と、ダイオード素子11に直列に接続された制御用スイッチ7と、半導体スイッチ素子10がオフ状態のときに制御用スイッチ7をオフ状態にし、半導体スイッチ素子10がオン状態のときに制御用スイッチ7をオン状態にするスイッチ制御部15とを含む。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

半導体装置

【課題】回路構成の簡素化を図るとともに、遅延回路の遅延時間のばらつき等に起因して生じる問題点を解消し、コンパレータの動作を保証する2逓倍器を備えた半導体装置を提供する。

【解決手段】入力クロック信号CLKを可変遅延器16で遅延させた遅延クロック信号CLKDと、前記入力クロック信号の位相を位相比較器18で比較することで前記入力クロック信号CLKの周波数を2逓倍した2逓倍クロック信号CLKX2を生成する2逓倍器20と、前記2逓倍器20からの2逓倍クロック信号CLKX2が第1の論理レベルのとき入力信号の大小の比較動作を行い、前記2逓倍クロック信号CLKX2が第2の論理レベルのとき、比較動作を停止するコンパレータ10と、前記コンパレータ10の出力をモニタし、前記コンパレータ10が比較結果を出力したことを検出した時点でトリガ信号DLCLKを生成する第1の回路12、14を備える。

(もっと読む)

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

半導体装置

【課題】分割抵抗回路で消費される消費電力を低減することが可能な半導体装置を提供する。

【解決手段】半導体装置は、抵抗分割回路で抵抗分割された分割電圧を受けるための入力端子と、入力端子から供給される分割電圧と、所定の基準電圧と、の電圧差を検出する検出回路と、外部から入力信号を受けるための信号入力端子と、分割電圧と入力信号の電圧を比較するカレントミラー回路と、を備え、カレントミラー回路は、検出回路が検出した電位差に応じて、カレントミラー回路に入力される分割電圧を実効的に補正する電位補正回路と、を含む。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】複数の出力トランジスタが並列接続された構成を備え、出力トランジスタを含む各電流経路間で分担電流を高精度に均一に揃えることができる半導体装置、および当該半導体装置の駆動方法を提供する。

【解決手段】互いに並列に接続された複数の出力トランジスタを備える半導体装置であって、出力トランジスタごとに設けられ第1の制御信号を供給する駆動回路と、第1の制御信号に含める出力トランジスタのコンダクタンスの情報を有するデータを記憶するメモリと、メモリにデータを入力するための第1の外部入力端子と、各駆動回路に出力トランジスタを1つずつ入れ替わり導通させる第2の制御信号を入力するための第2の外部入力端子とを備え、各駆動回路は、メモリに記憶されている駆動対象の出力トランジスタについてのデータを読み出して、コンダクタンスの情報を含む第1の制御信号を生成する。

(もっと読む)

論理回路の故障検出方法、テスト回路挿入方法、テスト回路挿入装置および半導体集積回路

【課題】 論理ゲートの一方の入力を含む信号パスの遅延故障と、論理ゲートの他方の入力を含む信号パスの遅延故障とを、1つの制御点により検出する。

【解決手段】 第1および第2ユーザロジックと、第1ユーザロジックの出力に接続される第1入力を有する第1論理ゲートと、第1論理ゲートの出力に接続された第3ユーザロジックと、第2ユーザロジックと第1論理ゲートとの間に挿入された制御点とを有する。制御点は、第1または第3ユーザロジックの第1スキャンフリップの1つのデータ出力がデータ入力に接続された第2スキャンフリップフロップと、一対の入力が第2スキャンフリップフロップのデータ出力および第2ユーザロジックの出力にそれぞれ接続され、出力が第1論理ゲートの第2入力に接続された第2論理ゲートとを有する。

(もっと読む)

電源制御装置、電源制御装置の制御方法、およびプログラム

【課題】多様な信号規格の処理に対応する半導体集積回路において、様々な周期性の違いに伴いタイミングと時間幅が変わるアイドル状態に対応した電源制御を適用し、消費電力を低減する。

【解決手段】処理状態と待機状態とを周期的に繰り返して処理を行う半導体集積回路の電源ドメインを制御する電源制御装置であって、待機状態の発生期間および発生間隔を含む周期的特徴情報を取得する周期情報取得部103と、電源ドメインが待機状態における待機電圧から半導体集積回路が動作可能となる電圧へ復帰するまでに要する復帰時間と対応付けられた待機電圧候補から、発生期間よりも復帰時間が短くなる待機電圧を電源制御情報として設定する電源制御情報設定部104と、電源制御情報に従って発生期間における電源ドメインの待機電圧を制御する電源制御部105とを備える。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

半導体装置

【課題】直流電源配線に電流が流れたか否かを検出可能な回路を備えた半導体装置を提供する。

【解決手段】半導体装置において、駆動回路BLDU,BLDD,BLBDU,BLBDDは、電流磁界またはスピン注入によってトンネル磁気抵抗素子TMR,TMRBを第1の磁化状態に初期設定するために、制御信号線BL,BLBに直流電流を流す。電源配線DLは、トンネル磁気抵抗素子TMR,TMRBに近接して設けられる。ここで、トンネル磁気抵抗素子TMR,TMRBは、電源配線DLに直流電流が流れるときに生じる電流磁界によって第2の磁化状態に変化する。センスアンプ10は、トンネル磁気抵抗素子TMR,TMRBが第1の磁化状態から第2の磁化状態に変化したか否かを判定するために、制御信号線BL,BLBを介してトンネル磁気抵抗素子TMR,TMRBに流れる電流を検出する。

(もっと読む)

半導体装置および電源供給方法

【課題】消費電力を低減することが可能な半導体装置および電源供給方法を提供することである。

【解決手段】本発明にかかる半導体装置は、内部回路3に電源を供給する電源供給部4と、内部回路3の複数の場所における特性をモニタする複数のモニタ部1_1〜1_Nと、複数のモニタ部1_1〜1_Nから出力された信号C_1〜C_Nに基づき算出されたモニタ値C_AVEと、設定された比較値COMPとの比較結果に応じて電源供給部4を制御する制御部2と、を備える。制御部2は、複数のモニタ部1_1〜1_Nにおける特性のばらつきに応じて比較値COMPを設定する。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

1 - 20 / 1,067

[ Back to top ]