Fターム[5F038EZ14]の内容

Fターム[5F038EZ14]に分類される特許

1 - 20 / 1,200

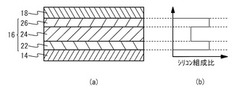

三次元配置部品を有する化合物半導体集積回路

容量素子

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体装置

【課題】任意の配線設計に適用でき、高精度な抵抗比を有する2個の抵抗体を備えた小型の半導体装置を提供する。

【解決手段】抵抗体R1f,R2fの長さをL、配線4a,4bの直上にある抵抗体R1f,R2fの外辺の長さを配線上長さH、外辺配線被覆率Vを、V=H/2Lで定義したとき、2個の抵抗体R1f,R2fのうち少なくとも外辺配線被覆率Vの小さい抵抗体R2fの下方において、配線4a,4bと同じ配線層から形成された反射補正パッドPa,Pbが、外辺の直下に配置されてなり、反射補正パッドPa,Pbの直上にある抵抗体R2fの外辺の長さを補正パッド上長さPとし、抵抗体R1f,R2fの外辺配線層被覆率Wを、W=(H+P)/2Lで定義したとき、2個の抵抗体R1f,R2fについて、外辺配線層被覆率Wの差が、記外辺配線被覆率Vの差より小さく設定されてなる半導体装置100とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ブレード欠けやチップ端部のチッピングを防ぎ、かつウエハプロセスの評価を行うこともできる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1の有効領域2と有効領域2の周囲の無効領域3にそれぞれ拡散層4,5を同時に形成する。拡散層4,5上にそれぞれエミッタ電極6及び小信号電極7を同時に形成する。小信号電極7にプローブ12を接触させて拡散層5の電気特性又は拡散層5と小信号電極7のコンタクト抵抗を測定するテストを行う。テストの後に、エミッタ電極6上に開口10を有し、小信号電極7を覆う絶縁膜9を形成する。開口10を介してエミッタ電極6上にメッキ11を形成する。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

磁気抵抗素子構造の製造方法

【課題】本発明は、磁気抵抗材料と集積回路とを巧みに統合することのできる、磁気抵抗素子構造の製造方法を提供する。

【解決手段】基板を提供する工程と、上記基板の上に金属ダマシン構造を形成する工程と、該金属ダマシン構造に電気的に接続するように該金属ダマシン構造の上にパターン化磁気抵抗ユニットを形成する工程とを含む、磁気抵抗素子構造の製造方法である。

(もっと読む)

集積電子構成要素を有する半導体発光装置

【課題】集積電子構成要素を含む半導体発光装置を提供する。

【解決手段】シリコンダイオード、抵抗体162、コンデンサ164、及び誘導子のような1つ又はそれよりも多くの回路要素が、半導体発光装置の半導体構造110と装置を外部構造に接続するのに使用される接続層との間に配置される。半導体構造に対するn接点114は、複数のバイアにわたって分散され、これは、1つ又はそれよりも多くの誘電体層によってp接点112から隔離されている。回路要素は、接点−誘電体層−接続層のスタックに形成される。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

半導体装置

【課題】半導体基板の上方にコイルが設けられた半導体装置において、コイル直下の半導体基板に回路を形成することができる半導体装置を提供する。

【解決手段】半導体装置は、一面11を有する半導体基板10と、半導体基板10の一面11に形成された絶縁層20と、絶縁層20の上方に形成されたコイル30と、を備えて構成されており、半導体基板10はコイル30の直下にスリット12を備えている。このスリット12は、コイル30のうち、半導体基板10の一面11に平行な面方向のうちの一方向に沿って形成された部分の直下に位置している。これにより、スリット12を境界として半導体基板10の渦電流面積が小さくなるので、半導体基板10に発生する渦電流による損失が低減し、コイル30の下部に位置する半導体基板10に回路を形成することが可能となる。

(もっと読む)

コンデンサ

【課題】小型でかつ高い静電容量を得られ、さらに絶縁性能の高い薄膜誘電体を用いたコンデンサを提供する。

【解決手段】薄膜コンデンサは無機物層と、自己組織化によって形成した有機物層とを積層した厚み10nm以下の誘電体膜と、前記誘電体膜の表面に形成された電極膜とを有する。電極膜はアルミを蒸着法によって、誘電体膜はアルミ蒸着膜を酸素プラズマ処理によって酸化膜を形成した表面に有機膜を付与して、形成することができる。これらを繰り返し積層、さらに巻回することが望ましい。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

高速スイッチング動作回路

【課題】より高電圧をより高速にスイッチングできる高速スイッチング動作回路を提供する。

【解決手段】DC/DCコンバータ1は、活性領域がSiC半導体からなるMISFETで構成されたスイッチング素子10を有する。駆動回路11は、スイッチング素子10を1MHz以上の駆動周波数で駆動する。スイッチング素子10のスイッチング時の電圧変化速度は5×109V/秒以上である。前記MISFETは、活性領域に形成されたトレンチと、トレンチの底面および壁面を絶縁膜と、絶縁膜を介して活性領域に対向するゲート電極とを含むトレンチゲート構造を有していてもよい。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

半導体装置

【課題】スパイラルインダクタを有する半導体装置における寄生容量の低減と、Q値の低下を抑制すること。

【解決手段】半導体基板と、前記半導体基板の表面近傍に設けられた複数個の素子分離領域と、前記素子分離領域間の半導体基板上に設けられた能動素子部と、基板上に積層された複数の配線層と、前記素子分離領域のうち第1の素子分離領域の鉛直上方であって、かつ、前記配線層のうち少なくとも最上の配線層に設けられたスパイラルインダクタとを備え、前記スパイラルインダクタが形成されたインダクタ形成領域の鉛直下方であって、かつ、前記第1の素子分離領域の半導体基板表面上にシリサイド形成防止膜が形成されていることを特徴とする半導体装置。

(もっと読む)

トレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法

【課題】製造コストの増加を抑制し、キャパシタの端部の段差を小さくできるトレンチ型PIPキャパシタとそれを用いたパワー集積回路装置およびパワー集積回路装置の製造方法を提供することにある。

【解決手段】トレンチ52内壁に分離絶縁層53を配置し、この分離絶縁層53を介して下部電極となる第1ポリシリコン54を埋め込んだトレンチ型PIPキャパシタ50を半導体基板に形成することで、キャパシタの端部に形成される段差を低減できる。その結果、配線となるメタル層59を過度に厚くする必要がなく、メタル層59を微細化することができる。その結果、パワーICを微細化することができる。

(もっと読む)

1 - 20 / 1,200

[ Back to top ]