Fターム[5F038EZ17]の内容

Fターム[5F038EZ17]に分類される特許

1 - 20 / 527

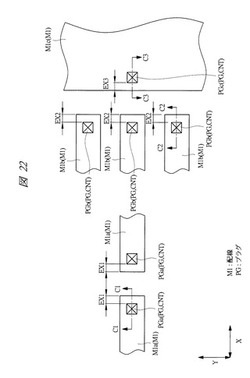

半導体装置の設計方法、半導体装置の製造方法および半導体装置

【課題】半導体装置の性能を向上させる。

【解決手段】半導体装置の設計フローは、プラグPGに接続された配線M1を含むチップレイアウトを設計するステップと、設計されたチップレイアウトにおけるプラグPGに対する配線M1のマージンを、プラグPGに対する配線M1のリセス量に応じて修正するステップとを有している。この修正ステップは、テストウエハに試験用プラグとそれに3次元的に接続された試験用配線とを含むテストパターンを形成するサブステップと、試験用配線の配線幅および配線密度と試験用プラグに対する試験用配線のリセス量との相関を調べるサブステップを有している。更に、得られた相関に基づいてプラグPGに対する配線M1のリセス量を予測するサブステップと、予測されたリセス量に応じてプラグPGに対する配線M1のマージンを修正するサブステップを有している。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

型押し構造体の製造方法、薄膜トランジスター、薄膜キャパシター、アクチュエーター、圧電式インクジェットヘッド及び光学デバイス

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより金属酸化物又は金属となる液体材料を準備する第1工程と、基材上に液体材料を塗布することにより金属酸化物又は金属の前駆体組成物からなる前駆体組成物層を形成する第2工程と、前駆体組成物層に対して凹凸型を用いて型押し加工を施すことにより前駆体組成物層に残膜を含む型押し構造を形成する第3工程と、型押し構造が形成された前駆体組成物層に対して大気圧プラズマ又は減圧プラズマによるアッシング処理を施すことにより残膜を処理する第4工程と、前駆体組成物層を熱処理することにより、前駆体組成物層から金属酸化物又は金属からなる型押し構造体を形成する第5工程とをこの順序で含む型押し構造体の製造方法。

(もっと読む)

炭化珪素半導体装置

【課題】 少ない工程数で形成でき、耐熱性に優れた温度センサを備える炭化珪素半導体装置を得る。

【解決手段】 炭化珪素基板1の活性領域ARに形成された半導体素子と、活性領域ARを取り囲むように炭化珪素基板1中に形成されたウエル領域5と、炭化珪素基板1上に配設される多結晶シリコンからなるゲート電極8と、ゲート電極8と同時に形成され、その一部を用いて形成した測温抵抗体17と、を備えることを特徴とする。

(もっと読む)

半導体装置

【課題】静電破壊による歩留まりの低下を防ぐことができる半導体装置。

【解決手段】複数の画素を選択するための信号を走査線に供給する走査線駆動回路が、上記信号を生成するシフトレジスタを有しており、上記シフトレジスタにおいて、複数のトランジスタのゲート電極として機能する一の導電膜を複数に分割し、上記分割された導電膜どうしを、分割された導電膜と異なる層に形成された導電膜により、電気的に接続する構成を有する。上記複数のトランジスタには、シフトレジスタの出力側のトランジスタが含まれるものとする。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3からなるPN接合ダイオード35と、P+型拡散層6と繋がるP+型引き出し層5aをエミッタ、N−型エピタキシャル層4をベース、P型半導体基板1をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構成する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それと接続され、取り囲むN+型拡散層7とはカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、そのときの放電電流I1によりP+型引き出し層5aよりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし、大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】消費電力が小さく抑えられ、出力される電位の振幅が小さくなるのを防ぐことができる、単極性のトランジスタを用いた半導体装置。

【解決手段】第1電位を有する第1配線、第2電位を有する第2配線、及び第3電位を有する第3配線と、極性が同じである第1トランジスタ及び第2トランジスタと、第1トランジスタ及び第2トランジスタのゲートに第1電位を与えるか、第1トランジスタ及び第2トランジスタのゲートに第3電位を与えるかを選択し、なおかつ、第1トランジスタ及び第2トランジスタのドレイン端子に、1電位を与えるか否かを選択する複数の第3トランジスタと、を有し、第1トランジスタのソース端子は、第2配線に接続され、第2トランジスタのソース端子は、第3配線に接続されている半導体装置。

(もっと読む)

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

多層膜キャパシタ構造及び方法

【課題】多くの電極あるいは電極の組合せのいずれにも簡単に接近できる改良された膜キャパシタ構造の提供。

【解決手段】多層膜キャパシタ構造が、モノリシック基板上の下部電極層、下部電極上に敷かれている膜電極及び誘電体材料の対からなる中間層、及び中間層対の上に敷かれている膜電極及び膜誘電体の対からなる上部層を有する。この構造は、デバイスの全周縁にわたって、それぞれの電極層がその上の層の周縁の外側まで側方に広がる、

メサ形状を有することが望ましい。電極をいかなる組合せでも接続でき、いかなる所望の回路接続もできるように、各電極層はその突き出している縁にビアを通して接続できる上部表面を有する。望ましければ、単層キャパシタ構造をフィルタに最適化し得るように、誘電体材料に異なる周波数特性をもたせることができる。

(もっと読む)

エネルギー変換素子並びにその製造及び動作方法

【課題】エネルギー変換素子並びにその製造及び動作方法を提供する。

【解決手段】エネルギー変換素子並びにその製造及び動作方法に係り、該エネルギー変換素子は、複数のドーピング領域を含むモノリシック単結晶シリコン層、単結晶シリコン層に内在し、複数のドーピング領域のうち1つのドーピング領域30にのみ連結された振動体32、34、振動体32、34に印加される入力信号が経由するPN接合ダイオード(第1ダイオード)、及び振動体32、34から出力される信号が経由するPN接合ダイオード(第2ダイオード)を含み、単結晶シリコン層は、内部に密閉された空間60を含み、振動体32、34は、空間60に備えられてもよい。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

電力増幅器

【課題】本発明は、発振電力を吸収する抵抗の抵抗値を容易に制御できる電力増幅器を提供することを目的とする。

【解決手段】本願の発明に係る電力増幅器10は、複数のトランジスタセルが形成された半導体基板12と、該半導体基板上に形成された、該複数のトランジスタセルのドレイン電極40と、該半導体基板上に該ドレイン電極と接続されるように形成された、ドレインパッド42と、該半導体基板に、該ドレインパッドに沿って該ドレインパッドと接するように形成されたイオン注入抵抗44と、該半導体基板上に該イオン注入抵抗を介して該ドレインパッドと接するように形成されたフローティング電極46と、該半導体基板の外部に形成された出力整合回路16と、該ドレインパッドと該出力整合回路を接続する配線18a,18b,18c,18dと、を備える。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を

提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワ

ー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと

、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界

効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が

小さい半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】素子特性を悪化させず、アクティブ領域を終端領域に対して、簡単な方法により電気的に独立させることができ、さらには素子サイズの小型化を図ることができる半導体装置およびその製造方法を提供すること。

【解決手段】エピタキシャル層23のアクティブ領域12と終端領域11との間に、エピタキシャル層23の表面24を形成するように、当該表面24に沿って全体にわたって形成されたチャネル層26を、ゲートトレンチ28の深さD1と同じ深さD2を有するアイソレーショントレンチ39で分断する。互いに同じ深さのゲートトレンチ28およびアイソレーショントレンチ39は、同一のエッチング工程で形成される。

(もっと読む)

組合せ出力バッファおよびESDダイオードデバイス

【課題】改良されたESD保護デバイスおよび該動作方法が、必要とされる。

【解決手段】集積回路ESD保護回路270は、ゲートダイオード271および出力バッファMOSFET272を含有する組合せデバイスとともに形成される。第1導電性タイプのボディタイフィンガ307は、基板301、302に形成され、複数のダイオードポリフィンガ231、232を用いて第2導電性タイプ310のドレイン領域から分離される。複数のダイオードポリフィンガ231、232は、出力バッファMOSFET272を形成する複数のポリゲートフィンガ204、205と交互配置される。

(もっと読む)

1 - 20 / 527

[ Back to top ]