Fターム[5F038EZ20]の内容

Fターム[5F038EZ20]に分類される特許

1 - 20 / 9,019

半導体集積回路

半導体装置

データドライバ、表示パネル駆動装置及び表示装置

半導体集積回路

ESD保護回路およびこれを備えた半導体装置

可変インダクタ

三次元配置部品を有する化合物半導体集積回路

半導体集積回路

半導体集積回路、半導体集積回路の制御方法

半導体装置

出力制御スキャンフリップフロップ、それを備えた半導体集積回路及び半導体集積回路の設計方法

半導体装置

ESD保護回路

ダミーパターンの設計方法

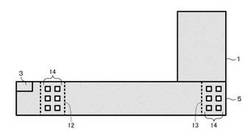

【課題】金属配線パターンの寄生抵抗を低減可能なダミーパターンの設計方法を提供する。

【解決手段】切り欠きパターン2を一及び逆方向に各所定値Δx1だけ縮小して縮小図形4を生成した後、各所定値Δx1だけ拡大してダミーパターン5を生成し、その外形を抽出して矩形図形6を生成した後、各所定値Δx1だけ縮小して縮小図形7を生成し、ダミーパターン5から縮小図形7を論理減算して切り欠き図形8及び矩形図形9を生成し、切り欠き図形8を抽出してダミーパターン5から論理減算して矩形図形10を生成した後、各所定値Δx1だけ縮小して縮小図形11を生成し、矩形図形10から縮小図形11を論理減算して第1,第2のビア配置領域12,13を生成し、各ビア配置領域12,13にビア14をそれぞれ配置する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

容量素子

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

(もっと読む)

発振回路およびテスト回路

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体チップ及びその抵抗測定方法、並びに半導体装置

【課題】本発明は、貫通電極のサイズ(直径)が縮小化された場合でも、4端子法により貫通電極の抵抗値を正確に測定することの可能な半導体チップ及びその抵抗測定方法、並びに半導体装置を提供することを課題とする。

【解決手段】半導体基板101及び回路素子層102を有する半導体チップ本体55と、半導体チップ本体55を貫通する第1乃至第4の貫通電極61〜64と、回路素子層102に設けられた回路素子を介することなく、第1の貫通電極61と第2の貫通電極62とを電気的に接続する第1の導電経路96と、回路素子を介することなく、第1の貫通電極61と第3の貫通電極63とを電気的に接続する第2の導電経路97と、回路素子を介することなく、第2の貫通電極62と第4の貫通電極64とを電気的に接続する第3の導電経路98と、を有する。

(もっと読む)

1 - 20 / 9,019

[ Back to top ]